РГР Арифметические и логические основы информационных систем. РГР Арифм. и лог.. Отчет по расчетнографической работе по дисциплине Арифметические и логические основы вычислительных систем

Скачать 241.22 Kb. Скачать 241.22 Kb.

|

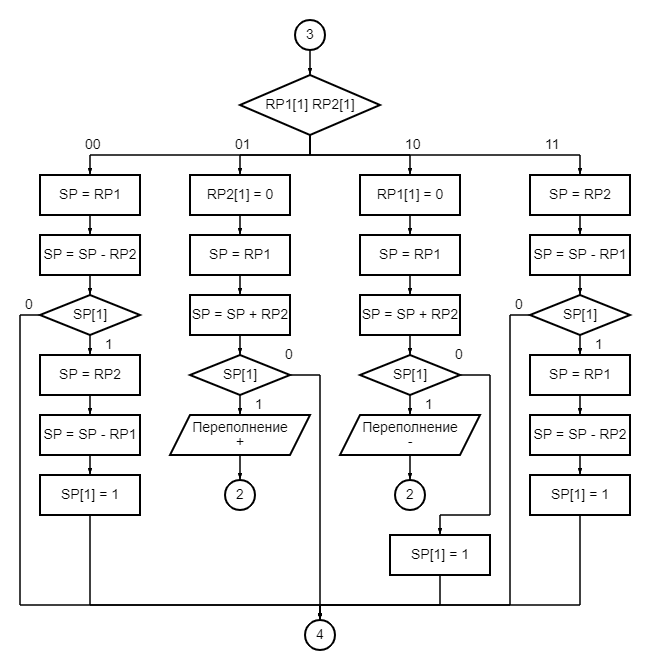

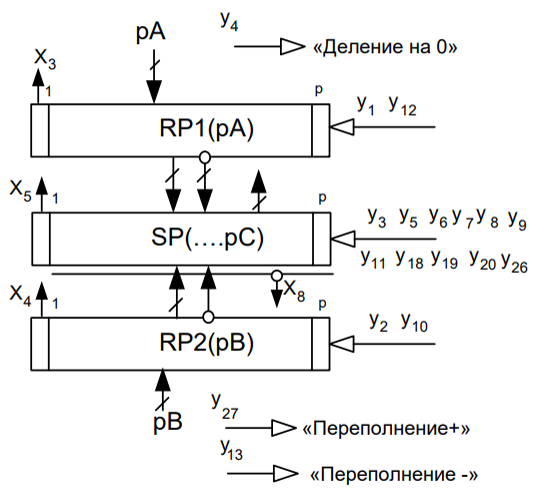

Министерство науки и высшего образования РФФедеральное государственное бюджетное образовательное учреждение высшего образования«ОМСКИЙ ГОСУДАРСТВЕННЫЙ ТЕХНИЧЕСКИЙ УНИВЕРСИТЕТ»Кафедра «Информатика и вычислительная техника»ОТЧЕТ ПО РАСЧЕТНО-ГРАФИЧЕСКОЙ РАБОТЕ по дисциплине:«Арифметические и логические основы вычислительных систем»На тему: «Разработка арифметико-логического устройства»ВыполнилСтудент гр. ИВТ-212______________Плаксин К.С.Проверилдоцент, к.н.______________Червенчук И.В.Омск 2022ОглавлениеВведение 3 Реализация операции деления чисел в прямом коде с неподвижным сумматором, без восстановления остатка 4 Схема алгоритма 6 Операционное устройство 7 Схема устройства 8 Пример выполнения операции 9 Заключение 11 ВведениеОсновной задачей расчетно-графической работы является разработка операционного устройства на структурном уровне, выполняющего заданную арифметическую операцию. Арифметическое устройство (АУ) – одно из основных устройств электронной цифровой вычислительной машины (ЦВМ), в котором непосредственно выполняются арифметические и логические операции над числами. К арифметическим операциям относятся сложение, вычитание, умножение, деление и извлечение корня. Выполнение любой арифметической операции в АУ сводится к последовательному выполнению ряда элементарных операций. В расчетно-графической работе показана работа с системами счисления, двоичной арифметикой, арифметическими операциями над двоичными числами. В работе разобрана операция деления чисел в прямом коде с неподвижным сумматором, без восстановления остатка. Реализация операции деления чисел в прямом коде с неподвижным сумматором, без восстановления остаткаВвод исходных чисел происходит следующим образом: А делимое заносится в сумматор SM, а делитель заносится в регистр RM2. В счетчик CT загружается число разрядов числа без учета знакового – N-1. В триггер T заносится знак результата Зн[A] ⊕ Зн[B], где ⊕ – логическая операция «сложние по модулю два»; Зн(А) – знак А (первый разряд мантиссы mА); Зн(В) – знак В (первый разряд мантиссы mВ). Начинается цикл со счетчиком. Делается сдвиг регистра частного вправо, а регистра частного влево на один разряд и счетчик цикла уменьшается на единицу. Из сумматора вычитается делитель, если N-ая цифра RM1 равна единице, в противном случае производится сложение сумматора и содержимого регистра делителя. Проверяется знак сумматора, если он равен единице, то очередная цифра частного равна нулю. В противном случае следующая цифра частного равна единице. Цикл продолжается пока проверка счетчика на ноль, не даст положительный результат. По окончании указанных действий на RG1 должен находиться результат. Если производилась предварительная проверка и приведение к mА < mВ, результат получается нормализованным. Далее необходимо загрузить из триггера знак результата в первый разряд RG1[1] = T. После этого производится вывод результата. Схема алгоритма  Рисунок 1 – Схема алгоритма Операционное устройство

Схема устройства  Рисунок 2 – Структурная схема устройства деления чисел в прямом коде без восстановления остатка с неподвижным сумматором Пример выполнения операцииmA = 0,11000101; N = 9; pA = 10010; mB = 0,11010111; – B = 1,00101001; pB = 01010; mA < mB T = 0 ⊕ 0 = 0

Ответ: 0, 11101010; 1000. ЗаключениеВ ходе расчетно-графической работы были произведены арифметические операции над двоичными числами, в частности разобрана операция деления чисел в прямом коде с неподвижным сумматором, без восстановления остатка. |

= 0,01101011 | 100

= 0,01101011 | 100 = 1,10010100 | 100

= 1,10010100 | 100 ← = 0,00000001

← = 0,00000001