Синтез конечного автомата, работающего по принципу автомата Мили. КУРСАЧ ВиМТ. Синтез конечного автомата

Скачать 196.39 Kb. Скачать 196.39 Kb.

|

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Таблица переходов 6 | ||||||||

| X | S0 | S1 | S2 | S3 | S4 | S5 | S6 | S7 |

| X=0 | S1 | S5 | S6 | S7 | S0 | S3 | S4 | S2 |

| X=1 | S7 | S0 | S1 | S2 | S3 | S4 | S5 | S6 |

| таблица состояний 1 | ||||||||

| X* | S0 | S1 | S2 | S3 | S4 | S5 | S6 | S7 |

| X=0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 0 |

| X=1 | 0 | 7 | 6 | 5 | 4 | 3 | 2 | 1 |

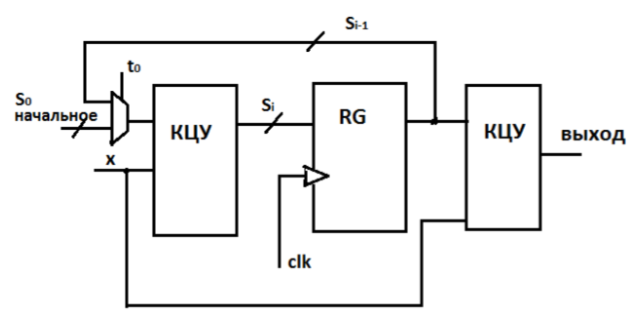

Структура автомата:

Синтез конечного автомата:

Построим схему автомата Мили, имеющего 3 разряда.

Согласно данным из условия, автомат будет совершать следующие переходы:

При х=0

S0-> S1-> S5-> S3-> S7-> S2->S6->S4->S0... или

1->2-> 6-> 4-> 0-> 3->7->5->1…

При х=1:

S0-> S7-> S6-> S5->S4->S3->S2->S1->S0… или

0-> 1-> 2-> 3-> 4-> 5-> 6-> 7-> 0->….

По этим данным запишем таблицу истинности для КЦУ автомата, именуя входы Si-1 - M[2..0], а выходы Si - N[2..0].

| X* | M2 | M1 | M0 | N2 | N1 | N0 |

| 0 | 0 | 0 | 0 | 0 | 1 | 1 |

| 0 | 0 | 0 | 1 | 0 | 1 | 0 |

| 0 | 0 | 1 | 0 | 1 | 1 | 0 |

| 0 | 0 | 1 | 1 | 1 | 1 | 1 |

| 0 | 1 | 0 | 0 | 0 | 0 | 0 |

| 0 | 1 | 0 | 1 | 0 | 0 | 1 |

| 0 | 1 | 1 | 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 0 | 0 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 0 | 1 | 1 |

| 1 | 0 | 1 | 1 | 1 | 0 | 0 |

| 1 | 1 | 0 | 0 | 1 | 0 | 1 |

| 1 | 1 | 0 | 1 | 1 | 1 | 0 |

| 1 | 1 | 1 | 0 | 1 | 1 | 1 |

| 1 | 1 | 1 | 1 | 0 | 0 | 0 |

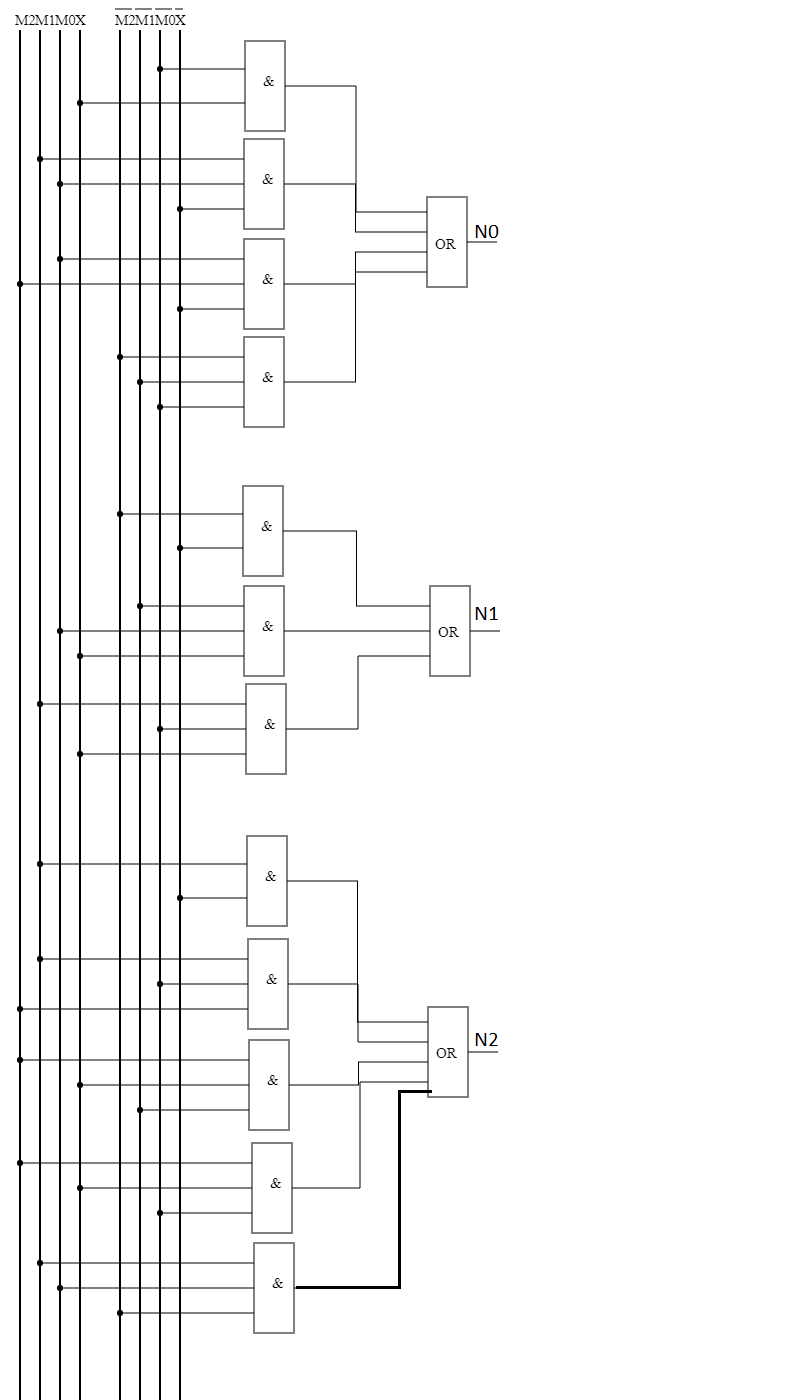

Запишем выражения для выходов используя карты Карно:

| M1M0 X* M2 | 00 | 01 | 11 | 10 |

| 00 | 1 | 0 | 1 | 0 |

| 01 | 0 | 1 | 1 | 0 |

| 11 | 1 | 0 | 0 | 1 |

| 10 | 1 | 0 | 0 | 1 |

Для N0:

N0 = M1M0(-X) or M0M2(-X) or (-M0)X or (-M1)(-M0)(-M2)

| M1M0 X* M2 | 00 | 01 | 11 | 10 |

| 00 | 1 | 1 | 1 | 1 |

| 01 | 0 | 0 | 0 | 0 |

| 11 | 0 | 1 | 0 | 1 |

| 10 | 0 | 1 | 0 | 1 |

Для N1:

N1 = (-M2)(-X) or (-M1)M0X or M1(-M0)X

| M1M0 X* M2 | 00 | 01 | 11 | 10 |

| 00 | 0 | 0 | 1 | 1 |

| 01 | 0 | 0 | 1 | 1 |

| 11 | 1 | 1 | 0 | 1 |

| 10 | 0 | 0 | 1 | 0 |

Для N2:

N2 = M1(-X) or M1(-M0)M2 or M2X(-M1) or M2X(-M0) or M1M0(-M2)

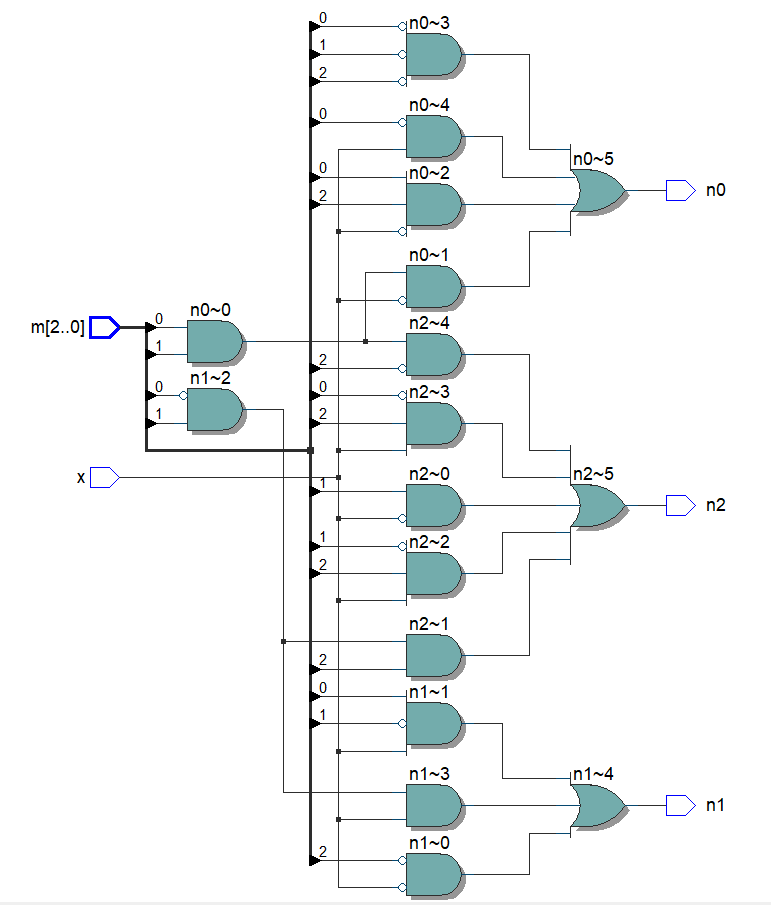

Структурная схема КЦУ

Программа работы устройства будет состоять из двух частей:

программирования переходов в следующее состояние на момент подачи импульса синхронизации,

программирование соответствия состояния определенному числу (второе КЦУ).

Block2

module block2

(input x, input [2:0]m, output n0,n1,n2);

assign n0= m[1]&m[0]&x | x&m[2]&m[0] | m[2]&m[1]&m[0] | x&m[0];

assign n1= m[2]&x | m[1]&m[0]&x | m[1]&m[0]&x;

assign n2= m[1]&x | m[1]&m[0]&m[2] | m[2]&m[1]&x | x&m[2]&m[0] | m[1]&m[0]&m[2];

endmodule

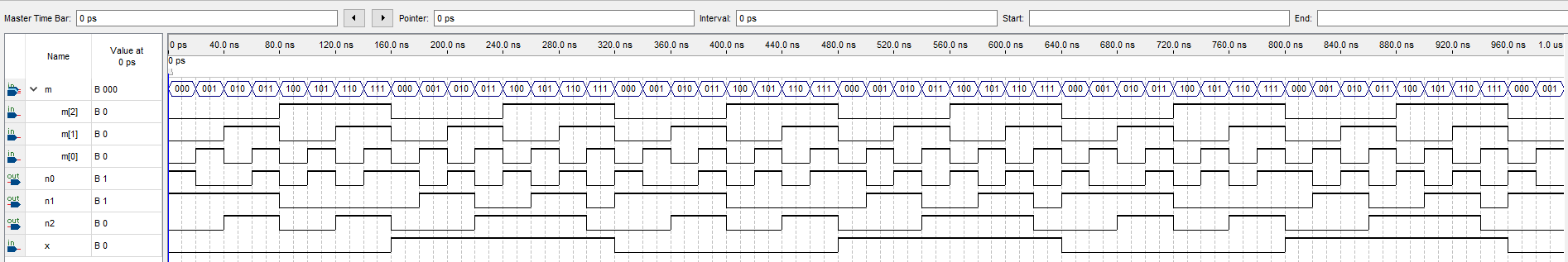

Waveform(block2)

Mealy3

module mealy_3

(input clk,a,b,reset,

output reg[2:0] out);

reg[2:0] state;

assign in1=a&(b)|a;

assign in2=b&(a)|b;

parameter S0=1,S1=2,S2=3,S3=4,S4=5,S5=6,S6=7,S7=0;

always@(posedge clk or posedge reset)

begin

if(reset)

state<=S0;

else

case(state)

S0:

if(in1)

begin

state<=S7;

end

else

begin

state<=S1;

end

S1:

if(in1)

begin

state<=S0;

end

else

begin

state<=S5;

end

S2:

if(in1)

begin

state<=S1;

end

else

begin

state<=S6;

end

S3:

if(in1)

begin

state<=S2;

end

else

begin

state<=S7;

end

S4:

if(in1)

begin

state<=S3;

end

else

begin

state<=S0;

end

S5:

if(in1)

begin

state<=S4;

end

else

begin

state<=S3;

end

S6:

if(in1)

begin

state<=S5;

end

else

begin

state<=S4;

end

S7:

if(in1)

begin

state<=S6;

end

else

begin

state<=S2;

end

endcase

end

always @ (state or in2)

begin

case(state)

S0:

if(in2)

begin

out=3'b000;

end

else

begin

out=3'b001;

end

S1:

if(in2)

begin

out=3'b111;

end

else

begin

out=3'b010;

end

S2:

if(in2)

begin

out=3'b110;

end

else

begin

out=3'b011;

end

S3:

if(in2)

begin

out=3'b101;

end

else

begin

out=3'b100;

end

S4:

if(in2)

begin

out=3'b100;

end

else

begin

out=3'b101;

end

S5:

if(in2)

begin

out=3'b011;

end

else

begin

out=3'b110;

end

S6:

if(in2)

begin

out=3'b010;

end

else

begin

out=3'b111;

end

S7:

if(in2)

begin

out=3'b001;

end

else

begin

out=3'b000;

end

endcase

end

endmodule

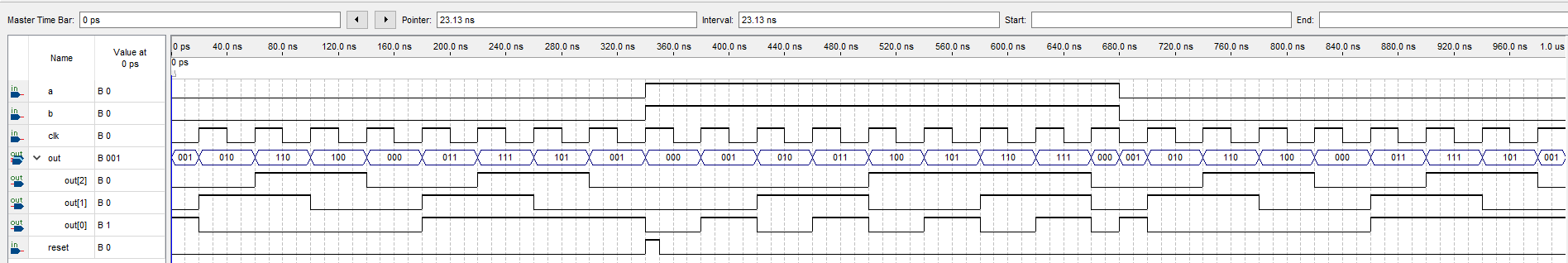

Waveform(mealy3)

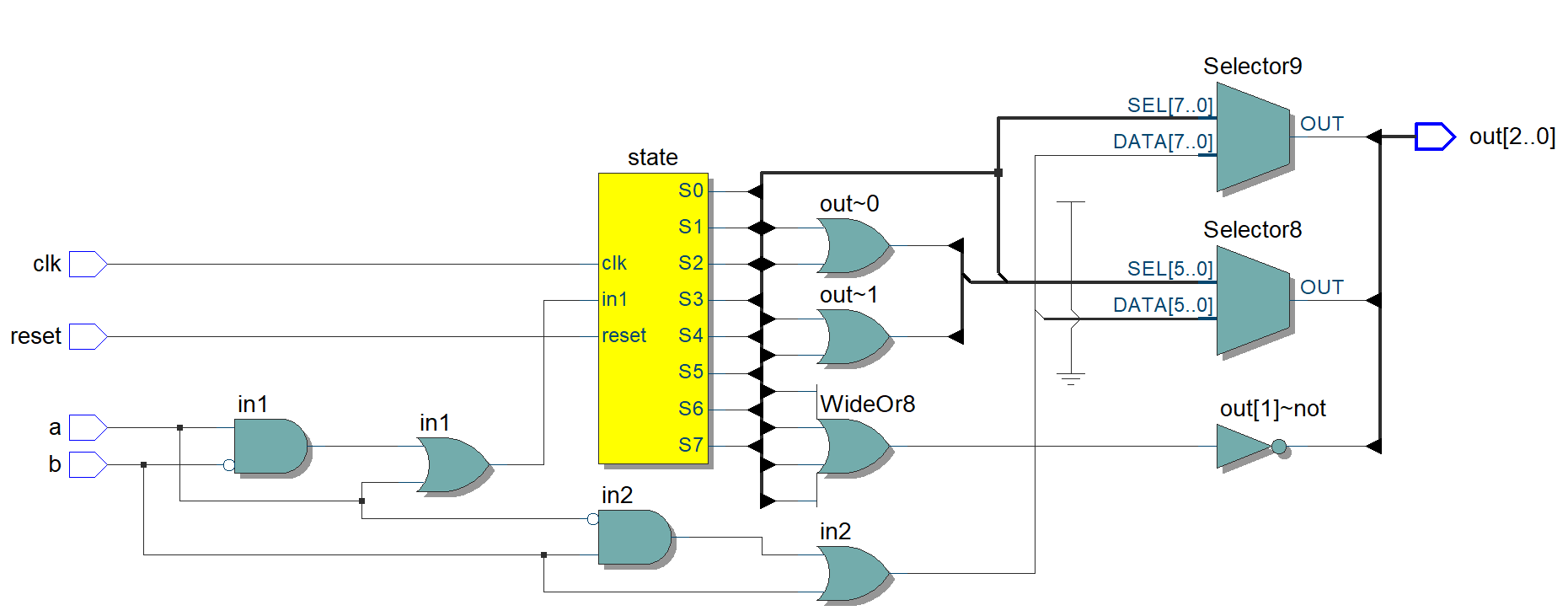

Электрическая схема(RTL Viewer)(mealy_3)

Электрическая схема(RTL Viewer)(block2)