электроника и схемотехника. 1 билет Свойства последовательного соединения элементов rlc. Последовательным

Скачать 1.35 Mb. Скачать 1.35 Mb.

|

|

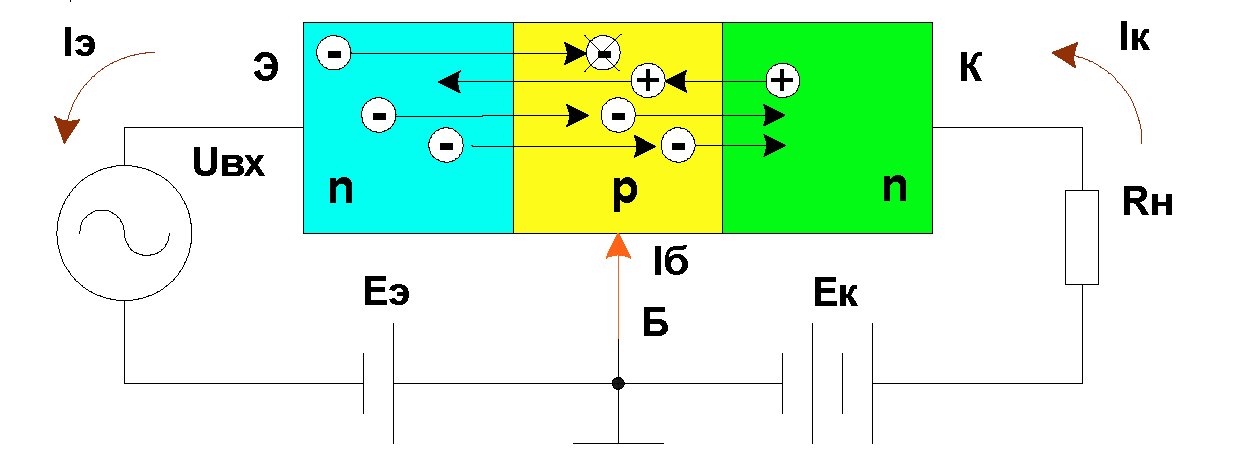

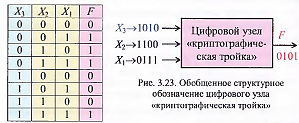

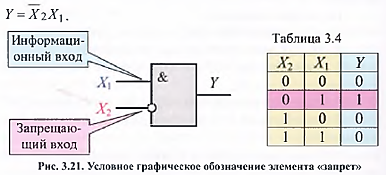

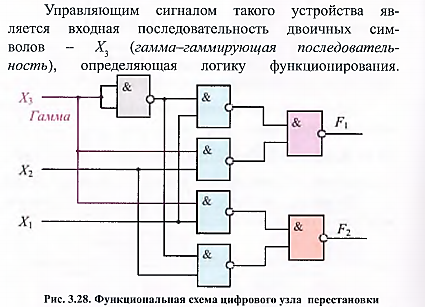

Устройство биполярных транзисторов. Основой биполярного транзистора является кристалл полупроводника p-типа или n-типа проводимости, который также как и вывод от него называется базой. Диффузией примеси или сплавлением с двух сторон от базы образуются области с противоположным типом проводимости, нежели база. О  бласть, имеющая бóльшую площадь p-n перехода, и вывод от неё называют коллектором. Область, имеющая меньшую площадь p-n перехода, и вывод от неё называют эмиттером. p-n переход между коллектором и базой называют коллекторным переходом, а между эмиттером и базой – эмиттерным переходом.Основной особенностью устройства биполярных транзисторов является неравномерность концентрации основных носителей зарядов в эмиттере, базе и коллекторе. В эмиттере концентрация носителей заряда максимальная. В коллекторе – несколько меньше, чем в эмиттере. В базе – во много раз меньше, чем в эмиттере и коллекторе. бласть, имеющая бóльшую площадь p-n перехода, и вывод от неё называют коллектором. Область, имеющая меньшую площадь p-n перехода, и вывод от неё называют эмиттером. p-n переход между коллектором и базой называют коллекторным переходом, а между эмиттером и базой – эмиттерным переходом.Основной особенностью устройства биполярных транзисторов является неравномерность концентрации основных носителей зарядов в эмиттере, базе и коллекторе. В эмиттере концентрация носителей заряда максимальная. В коллекторе – несколько меньше, чем в эмиттере. В базе – во много раз меньше, чем в эмиттере и коллекторе.Принцип действия биполярных транзисторов.При работе транзистора в усилительном режиме эмиттерный переход открыт, а коллекторный – закрыт. Это достигается соответствующим включением источников питания. Т  ак как эмиттерный переход открыт, то через него будет протекать ток эмиттера, вызванный переходом электронов из эмиттера в базу и переходом дырок из базы в эмиттер. Следовательно, ток эмиттера будет иметь две составляющие - электронную и дырочную. Основное соотношение токов в транзисторе: Iэ = Iк + Iбα - коэффициент передачи тока транзистора или коэффициент усиления по току: Iк = α ∙ IэДырки из коллектора как неосновные носители зарядов будут переходить в базу, образуя обратный ток коллектора Iкбо. Iк = α ∙ Iэ + Iкбо ак как эмиттерный переход открыт, то через него будет протекать ток эмиттера, вызванный переходом электронов из эмиттера в базу и переходом дырок из базы в эмиттер. Следовательно, ток эмиттера будет иметь две составляющие - электронную и дырочную. Основное соотношение токов в транзисторе: Iэ = Iк + Iбα - коэффициент передачи тока транзистора или коэффициент усиления по току: Iк = α ∙ IэДырки из коллектора как неосновные носители зарядов будут переходить в базу, образуя обратный ток коллектора Iкбо. Iк = α ∙ Iэ + IкбоИз трёх выводов транзистора на один подаётся входной сигнал, со второго - снимается выходной сигнал, а третий вывод является общим для входной и выходной цепи. 2. Узел <<Криптографическая тройка>> ЗАПРЕТ УЗЛЫ перестановки К  риптротрйока – цифровое устрйоство с тремя входами и одним выходом, реализ. функцию: риптротрйока – цифровое устрйоство с тремя входами и одним выходом, реализ. функцию:   УЗЕЛ ПЕРЕСТАНОВКИ запрет    17 билет: 1. 1 вопрос 16 билета 2. Классификация триггеров. Определение, особенности функционального обозначения входов RS-триггерa RS триггер получил название по названию своих входов. Вход S (Set — установить англ.) позволяет устанавливать выход триггера Q в единичное состояние (записывать единицу). Вход R (Reset — сбросить англ.) позволяет сбрасывать выход триггера Q (Quit — выход англ.) в нулевое состояние (записывать ноль).В простейшем случае RS триггер это два логических элемента "2И-НЕ", соединенные последовательно друг с другом. Его принципиальная схема приведена на рисунке 1. Обратите внимание, что у триггера только один выход. Обозначим его Q. Тогда оставшийся вывод схемы будет инверсным выходом Q Р  исунок 1. Схема простейшего rs триггера на схемах "2И-НЕ". Входы R и S инверсные (активный уровень'0') исунок 1. Схема простейшего rs триггера на схемах "2И-НЕ". Входы R и S инверсные (активный уровень'0')Рассмотрим принцип работы RS триггера, выполненный по изображенной на рисунке 1 схеме подробнее. Пусть на входы R и S подаются единичные потенциалы. Если на выходе верхнего логического элемента "2И-НЕ" Q присутствует логический ноль, то на выходе нижнего логического элемента "2И-НЕ" появится логическая единица. Эта единица подтвердит логический ноль на выходе Q. Если на выходе верхнего логического элемента "2И-НЕ" Q первоначально присутствует логическая единица, то на выходе нижнего логического элемента "2И-НЕ" появится логический ноль. Этот ноль подтвердит логическую единицу на выходе Q. То есть при единичных входных уровнях схема RS триггера работает точно так же как и схема на инверторах. Подадим на вход S нулевой потенциал. Согласно таблице истинности логического элемента "И-НЕ" на выходе Q появится единичный потенциал. Это приведёт к появлению на инверсном выходе триггера нулевого потенциала. Теперь, даже если снять нулевой потенциал с входа S, на выходе триггера останется единичный потенциал. То есть мы записали в триггер логическую единицу.

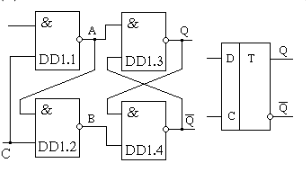

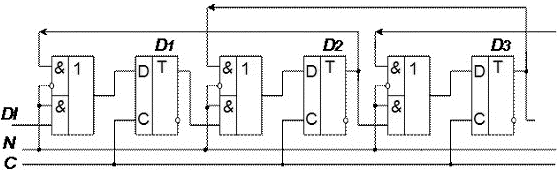

Таблица 1. Таблица истинности RS триггера. RS триггер можно построить и на логических элементах "ИЛИ". Его схема приведена на рисунке 2. Принцип работы RS триггера, собранный на логических элементах "ИЛИ" будет точно таким же, как и рассмотренный ранее. Единственное отличие в работе этой схемы по сравнению с предыдущей схемой RS триггера будет заключаться в том, что сброс и установка триггера будет производиться единичными логическими уровнями. Эти особенности связаны с принципами работы инверсной логики, которые рассматривались ранее. 18 билет: 1.- 2. Классификация триггеров. Определение, особенности функционального обозначения входов D-триггерa D  -триггером называется триггер с одним информационным входом, работающий так, что сигнал на выходе после переключения равен сигналу на входе D до переключения, т. е. Qn+1=Dn Основное назначение D-триггеров - задержка сигнала, поданного на вход D. Он имеет информационный вход D (вход данных) и вход синхронизации С. Вход синхронизации С может быть статическим (потенциальным) и динамическим. У триггеров со статическим входом С информация записывается в течение времени, при котором уровень сигнала C=1. В триггерах с динамическим входом С информация записывается только в течение перепада напряжения на входе С. Динамический вход изображают на схемах треугольником. Если вершина треугольника обращена в сторону микросхемы (прямой динамический вход), то триггер срабатывает по фронту входного импульса, если от нее (инверсный динамический вход) - по срезу импульса. В таком триггере информация на выходе может быть задержана на один такт по отношению к входной информации.D-триггеры могут быть построены по различным схемам -триггером называется триггер с одним информационным входом, работающий так, что сигнал на выходе после переключения равен сигналу на входе D до переключения, т. е. Qn+1=Dn Основное назначение D-триггеров - задержка сигнала, поданного на вход D. Он имеет информационный вход D (вход данных) и вход синхронизации С. Вход синхронизации С может быть статическим (потенциальным) и динамическим. У триггеров со статическим входом С информация записывается в течение времени, при котором уровень сигнала C=1. В триггерах с динамическим входом С информация записывается только в течение перепада напряжения на входе С. Динамический вход изображают на схемах треугольником. Если вершина треугольника обращена в сторону микросхемы (прямой динамический вход), то триггер срабатывает по фронту входного импульса, если от нее (инверсный динамический вход) - по срезу импульса. В таком триггере информация на выходе может быть задержана на один такт по отношению к входной информации.D-триггеры могут быть построены по различным схемамD-триггер возможно получить из синхронного RS-триггера, если ввести дополнительный инвертор DD1.1 между входами S и R (рис. 2.43,в). В таком триггере состояние неопределенности для входов S и R исключается, так как инвертор DD1.1 формирует на входе R сигнал /S. Временные диаграммы записи в D-триггер напряжений высокого и низкого входных уровней и их считывание приведены на рис. 2.43,г. Обязательным условием правильной работы D-триггера является наличие защитного временного интервала после прихода импульса на вход D перед тактовым импульсом (вход С). Этот интервал времени tn+1-tn зависит от справочных данных на D-триггер.Промышленностью выпускаются готовые микросхемы, содержащие динамические триггеры. В качестве примера можно назвать микросхему 1533ТМ2. В этой микросхеме содержится сразу два динамических триггера. Они изменяют своё состояние по переднему (нарастающему) фронту сигнала синхронизации. Внутренняя схема D-триггеров, примененных в микросхеме 1533ТМ2, содержит дополнительные асинхронные входы R и S. Они позволяют принудительно записывать в D-триггер логический ноль или логическую единицу, как в RS-триггере. 19 билет: 1. – 2. Классификация триггеров. Определение, особенности функционального обозначения входов T и JK-триггеров T-триггер — это счетный триггер. У данного триггера имеется только один вход. Принцип работы T-триггера заключается в следующем. После поступления на вход T импульса, состояние триггера меняется на прямо противоположное. Счётным он называется потому, что T триггер как бы подсчитывает количество импульсов, поступивших на его вход. Жаль только, что считать этот триггер умеет только до одного. При поступлении второго импульса T-триггер снова сбрасывается в исходное состояние T-триггеры строятся только на базе двухступенчатых триггеров, подобных рассмотренному ранее D триггеру. Использование двух триггеров позволяет избежать неопределенного состояния схемы при разрешающем потенциале на входе синхронизации "C", так как счетные триггеры строятся при помощи схем с обратной связью.T триггер можно синтезировать из любого двухступенчатого триггера. Т   -триггеры используются при построении схем различных счётчиков, поэтому в составе БИС различного назначения обычно есть готовые модули этих триггеров. Условно-графическое обозначение T триггера приведено на рисунке -триггеры используются при построении схем различных счётчиков, поэтому в составе БИС различного назначения обычно есть готовые модули этих триггеров. Условно-графическое обозначение T триггера приведено на рисункеT-триггеры широко применяются в схемах деления и умножения частоты. Без них было бы невозможна реализация синтезаторов частот, которые применяются в качестве задающих генераторов в передатчиках и гетеродинов в приемниках раций, мобильных телефонов или GSM навигаторов. Не менее важна роль T-триггеров в формировании тактовой частоты цифровых микросхем, таких как центральные процессоры компьютеров, планшетов или цифровых фотоаппаратов. Т  аблица истинности JK триггера практически совпадает с таблицей истинности синхронного RS-триггера. Для того чтобы исключить запрещённое состояние, его схема изменена таким образом, что при подаче двух единиц jk триггер превращается в счётный триггер. Это означает, что при подаче на тактовый вход C импульсов этот триггер изменяет своё состояние на противоположное аблица истинности JK триггера практически совпадает с таблицей истинности синхронного RS-триггера. Для того чтобы исключить запрещённое состояние, его схема изменена таким образом, что при подаче двух единиц jk триггер превращается в счётный триггер. Это означает, что при подаче на тактовый вход C импульсов этот триггер изменяет своё состояние на противоположное Для реализации счетного режима в схеме введена перекрестная обратная связь с выходов второго триггера на входы R и S первого триггера. Благодаря обратной связи на входах R и S первого триггера никогда не может возникнуть запрещенная комбинация, а то, что она перекрестная, вводит новый режим работы — счетный. При подаче на входы j и k логической единицы одновременно JK-триггер переходит в счетный режим, подобно T триггеру. Применение JK триггеров в составе цифровых счетчиков является их основной областью применения. В современной технике цифровые схемы собираются на основе заказных микросхем (ASIC) или микросхем программируемой логихи (FPGA). Их проектирование может вестись в графическом редакторе, точно так же, как это было описано выше, а может применяться язык программирования цифровых микросхем. В качестве примера на листинге 1 приведено описание JK триггера на языке VERILOG. 20 билет: 1. – 2 Регистры сдвига: влево(реверсивный) и вправо  Регистр сдвига – регистр, обеспечивающий помимо хранения информации, сдвиг влево или вправо всех разрядов одновременно на одинаковое число позиций. При этом выдвигаемые за пределы регистра разряды теряются, а в освобождающиеся разряды заносится информация, поступающая по отдельному внешнему входу регистра сдвига. Обычно эти регистры обеспечивают сдвиг кода на одну позицию влево или вправо. Но существуют и универсальные регистры сдвига, которые выполняют сдвиг как влево, так и вправо в зависимости от значения сигнала на специальном управляющем входе или при подаче синхросигналов на разные входы регистра. Регистр сдвига может быть спроектирован и таким образом, чтобы выполнять сдвиг одновременно не на одну, а на несколько позиций. Регистры сдвига строятся на двухступенчатых триггерах. Работа регистра сдвига в каждом периоде сигнала синхронизации разбивается на две фазы: при высоком и при низком значении синхросигнала:При высоком уровне синхросигнала проводится запись значения выхода ( i – 1 )-го разряда регистра в первую ступень i -го разряда. Вторая ступень каждого разряда сохраняет свое прежнее значение. В этой фазе состояние первой ступени i -го триггера повторяет состояние второй ступени ( i – 1 )-го триггера. Вторые ступени каждого триггера, а следовательно, и выходы регистра в целом, остаются неизменными.При низком уровне синхросигнала значение, записанное в первой ступени каждого триггера, перезаписывается в его вторую ступень. Запись в первую ступень триггера запрещена. В этой фазе состояния первой и второй ступеней каждого триггера становятся одинаковыми.Поступление сигнала R = 0 вне зависимости от значения сигнала на входе синхронизации С и сигнала на входе D0 устанавливает все разряды регистра в нулевое состояние. Реверсивные регистры сдвига обеспечивают возможность сдвига информации как вправо, так и влево. Они имеют специальный вход управления направлением сдвига.Поскольку транзисторы и логические элементы способны передавать сигналы только в одном направлении с входа на выход (слева направо), то, для сдвига информации влево, необходимо информацию с выхода последующих триггеров по специально созданным цепям подавать на входы предыдущих триггеров и записывать их следующим тактовым сигналом. Это эквивалентно сдвигу информации влево. Если сигнал на входе направления сдвига N=1, то потенциал на входе «Di» триггера определяется выходом Q триггера, стоящего слева от него. Если N=0, то выходом триггера, стоящего справа. Таким образом, при N=1 тактовые импульсы производят сдвиг информации вправо, а при N=0 –— сдвиг информации влево.  |