1. Магистральный принцип построения микропроцессорных систем

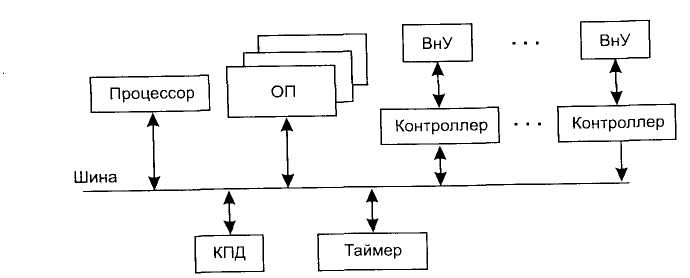

Магистральная архитектура (рис. 1) – процессор (процессоры) и блоки памяти (ОП) взаимодействуют между собой и с ВУ (контроллерами ВУ) через внутренний канал, общий для всех устройств (машины DEC, ПЭВМ IBM PC-совместимые). К этому типу архитектуры относится также архитектура персонального компьютера: функциональные блоки здесь связаны между собой общей шиной, называемой также системной магистралью.

Рис. 1. Магистральная архитектура

Физически магистраль представляет собой многопроводную линию с гнездами для подключения электронных схем. Магистраль – это набор электронных линий, связывающих центральный процессор, основную память и внешние устройства. Однако системная шина, как основная информационная магистраль, не может обеспечить достаточную производительность для внешних устройств. Для решения этой проблемы в компьютере используются локальные шины, которые связывают микропроцессор с периферийными устройствами.

Совокупность проводов магистрали разделяется на отдельные группы: шину адреса, шину данных и шину управления.

Периферийные устройства подключаются к аппаратуре компьютера через специальные контроллеры – устройства управления периферийными устройствами.

Контроллер – устройство, которое связывает периферийное оборудование или каналы связи с центральным процессором, освобождая процессор от непосредственного управления функционированием данного оборудования.

Мы хотим обратить внимание читателя на тот факт, что все перечисленные архитектурные элементы ЭВМ базируются на следующих схемных элементах и базовых узлах:

память обычно использует возможности и свойства триггера или его аналогов;

счетчик (регистр) адреса команд, очевидно, есть схемный узел «счетчик»;

сумматор – или полный сумматор, или полусумматор;

дешифратор (например, команд) тоже здесь присутствует.

Магистральная организация предполагает, как правило, наличие модуля управляющего обменом данными. Основное назначение этого модуля – организация передачи слова между двумя другими модулями.

Шинная (магистральная) организация получила широкое распространение, так как все устройства используют единый протокол сопряжения модулей центральных процессоров и устройств ввода-вывода с помощью трех шин.

2. JTAG-интерфейс и системные функции на его основе

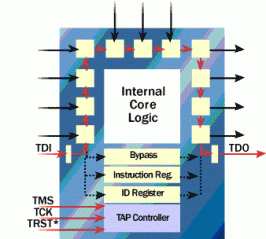

JTAG (Joint Test Action Group) – специализированный аппаратный интерфейс, разработанный для тестирования цифровых процессоров (стандарт IEEE 1149.1). Из-за широкой функциональности JTAG стал повсеместно использоваться для отладки и программирования.

На данный момент JTAG-интерфейс применяется при периферийном сканировании (рис. 2). Этот термин относится к тестированию печатных плат, с установленными на них процессорами, ПЛИС, флэш-микросхемами, на наличие в электроцепях коротких замыканий, непропаек, западаний на 0 или 1. Управление JTAG-интерфейсом описывается в так называемом BSDL-файле, который предоставляет разработчик.

Порт тестирования (Test Access Port) представляет собой четыре или пять выделенных выводов микросхемы: ТСК, TMS, TDI, TDO, TRST (опционально).

Рис. 2. JTAG-порт микросхемы и ячейки периферийного сканирования

Функциональное назначение этих линий:

TDI (вход тестовых данных) – вход последовательных данных периферийного сканирования. Команды и данные вдвигаются в микросхему с этого вывода по переднему фронту сигнала TCK;

TDO (выход тестовых данных) – выход последовательных данных. Команды и данные выдвигаются из микросхемы с этого вывода по заднему фронту сигнала TCK;

TCK (вход тестового тактирования) – тактирует работу встроенного автомата управления периферийным сканированием. Максимальная частота сканирования периферийных ячеек зависит от используемой аппаратной части и на данный момент ограничена 25 – 40 МГц;

TMS (вход управления тестированием) – обеспечивает выбор режима тестирования.

В некоторых случаях к перечисленным сигналам добавляется сигнал TRST для инициализации порта тестирования, что необязательно, так как инициализация возможна путем подачи соответствующей последовательности сигналов на вход TMS.

Работа средств обеспечения интерфейса JTAG подчиняется сигналам автомата управления, встроенного в микросхему. Состояния автомата определяются сигналами TDI и TMS порта тестирования. Определенное сочетание сигналов TMS и TCK обеспечивает ввод команды для автомата и ее исполнение

Если на плате установлено несколько устройств, поддерживающих JTAG, они могут быть объединены в общую цепочку. Уникальной особенностью JTAG является возможность программирования не только самого микроконтроллера (или ПЛИС), но и подключенной к его выводам микросхемы флэш-памяти. Причем существует два способа программирования флэш-памяти с использованием JTAG: через загрузчик с последующим обменом данными через память процессора, и через прямое управление ножками микросхемы.

Литература

Максимов Н.В., Партыка Т.Л., Попов И.И. Архитектура ЭВМ и вычислительных систем: Учебник. – М.: ФОРУМ: ИНФРА-М, 2005. – 512с.

Новиков Ю.В., Скоробогатов П.К. Основы микропроцессорной техники. Курс лекций: Учебное пособие. – М.: ИНТУИТ.РУ, 2004. – 440с.

Микропроцессоры: Учеб. для втузов/ Под редакцией Преснухина Л.Н. В 3-х кн. – М.: Высш. шк., 1986.

|

Скачать 93.5 Kb.

Скачать 93.5 Kb.