КП. Синтез конечного автомата, работающего по принципу автомата Мили

Скачать 221.56 Kb. Скачать 221.56 Kb.

|

|

ФЕДЕРАЛЬНОЕ АГЕНТСТВО СВЯЗИ Федеральное государственное образовательное бюджетное учреждение высшего образования «Санкт-Петербургский государственный университет телекоммуникаций им. проф. М.А. Бонч-Бруевича» ___________________________________________________________________________ Кафедра программной инженерии и вычислительной техники «Вычислительная и микропроцессорная техника» Курсовая работа на тему: «Синтез конечного автомата, работающего по принципу автомата Мили» № зачетной книжки 1504167 Выполнил: студентка группы ИКТ-517 Пугачёва А. А Принял Неелова О. Л Оценка: __________ (подпись) Санкт-Петербург 2017г ОглавлениеЗАДАНИЕ 2 ТАБЛИЦА ИСТИННОСТИ 3 ВЫРАЖЕНИЯ ДЛЯ ВЫХОДОВ КЦУ 4 ПРОГРАММА ДЛЯ ПРОВЕРКИ ПРАВИЛЬНОСТИ УРАВНЕНИЙ N0, N1, N2 6 СТРУКТУРНАЯ СХЕМА КЦУ: 7 ПРОГРАММА РАБОТЫ УСТРОЙСТВА 8 ДИАГРАММА ПЕРЕХОДОВ 13 ВРЕМЕННАЯ ДИАГРАММА 14 ЗАДАНИЕВариант 67. Синтезировать конечный автомат, работающий по принципу автомата Мили. В синтез входит построение схемы КЦУ автомата, временные диаграммы его работы, программа на VHDL для реализации автомата на макете в FPGA CycloneV и диаграмма переходов автомата. Условие для “x=1” – равнозначность входных сигналов “a” и “b”.

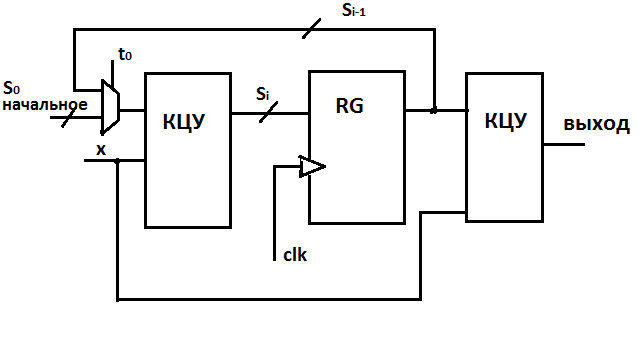

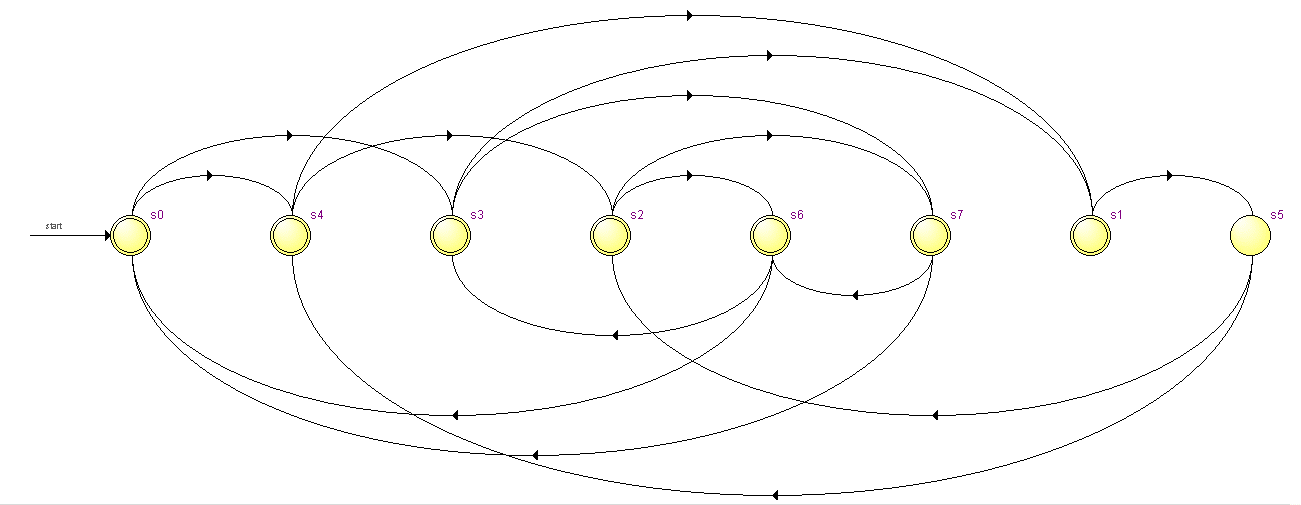

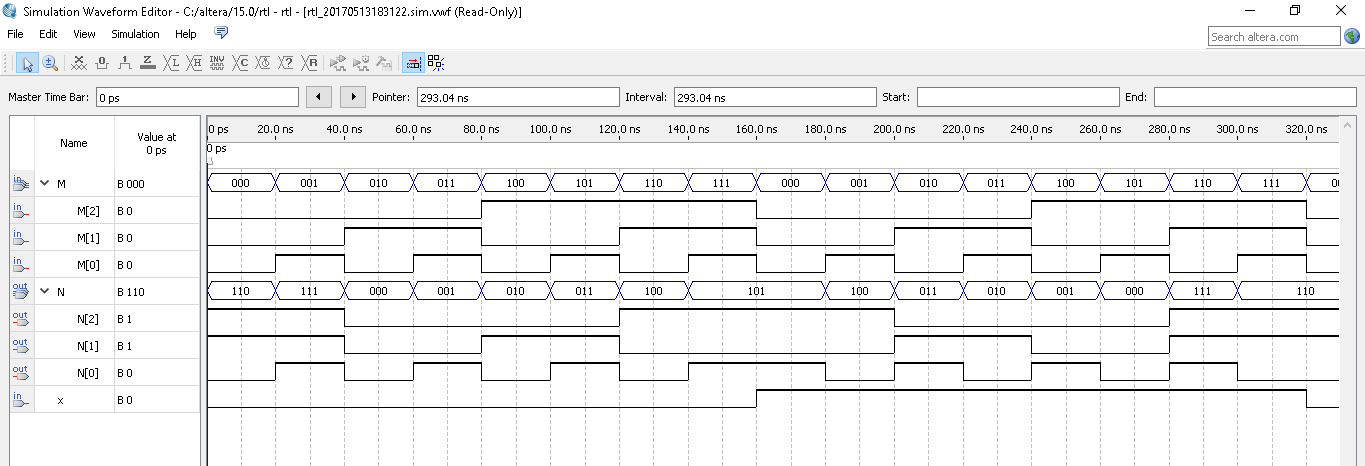

Структура автомата может быть представлена следующим образом :  ТАБЛИЦА ИСТИННОСТИПо таблицам состояний и переходов, можно записать, что при x = 0 автомат будет совершать переходы: S0->S3 ->S1->S5->S4->S2->S7->S6->S0->… или 6 -> 1 -> 7 -> 3 -> 2 -> 0 -> 5 -> 4 -> 6 ->… , а при x = 1 S0->S4->S1->S5->S2->S6->S3->S7->S0->… или 5-> 1-> 4-> 0-> 3-> 7-> 2-> 6-> 5->… По этим данным запишем таблицу истинности для КЦУ автомата, именуя входы Si-1 - M[2..0], а выходы Si - N[2..0].

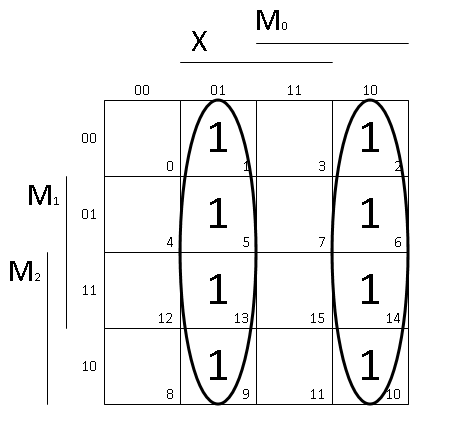

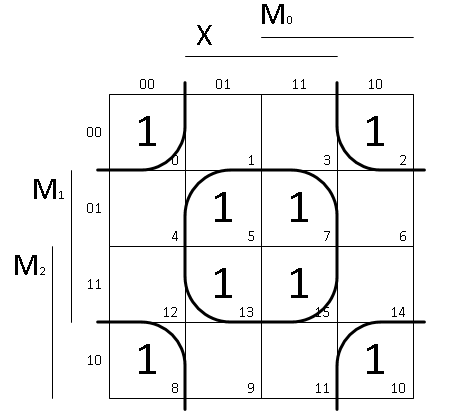

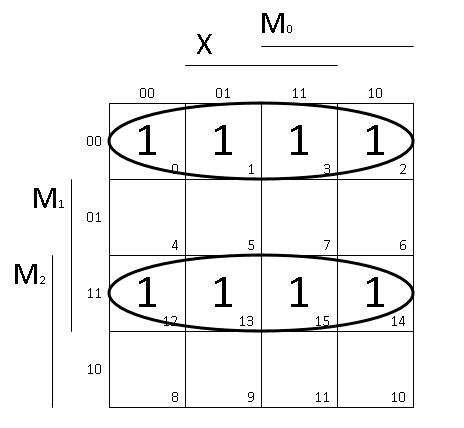

ВЫРАЖЕНИЯ ДЛЯ ВЫХОДОВ КЦУЗапишем выражения для выходов, используя карты Карно. Для N0:  N0 = ((M(0))and(not(x))) or ((x)and(not(M(0)))) Для N1:  N1 = ((M(1))and(x)) or ((not(x))and(not(M(1)))) Для N2:  N2 = ((not(M(1)))and(not(M(2)))) or ((M(1))and(M(2))) ПРОГРАММА ДЛЯ ПРОВЕРКИ ПРАВИЛЬНОСТИ УРАВНЕНИЙ N0, N1, N2Текст программы: library ieee; use ieee.std_logic_1164.all; entity kkarno is port(x: in std_logic; M: in std_logic_vector(2 downto 0); N: out std_logic_vector(2 downto 0)); end kkarno; architecture BBB of kkarno is begin process(M,x) begin N(0)<=((M(0))and(not(x)))or((x)and(not(M(0)))); N(1)<=((M(1))and(x))or((not(x))and(not(M(1)))); N(2)<=((not(M(1)))and(not(M(2))))or((M(1))and(M(2))); end process; end; СТРУКТУРНАЯ СХЕМА КЦУ: ПРОГРАММА РАБОТЫ УСТРОЙСТВАПрограмма работы устройства будет состоять из двух частей: программирования переходов в следующее состояние на момент подачи импульса синхронизации, и программирование соответствия состояния определенному числу (второе КЦУ). Текст программы: library ieee; use ieee.std_logic_1164.all; entity m is port (clk: in std_logic; a,b : in std_logic; start : in std_logic; ind : out std_logic_vector(6 downto 0)); end entity; architecture rtl of m is type state_type is (s0, s1, s2, s3, s4, s5, s6, s7); signal state : state_type; signal input: std_logic; signal output: std_logic_vector(2 downto 0); begin input<=(a)xnor(b); process (clk, start) begin if start = '1' then state <= s0; elsif (rising_edge(clk)) then case state is when s0=> if input = '1' then state <= s4; else state <= s3; end if; when s1=> if input = '1' then state <= s5; else state <= s5; end if; when s2=> if input = '1' then state <= s6; else state <= s7; end if; when s3=> if input = '1' then state <= s7; else state <= s1; end if; when s4=> if input = '1' then state <= s1; else state <= s2; end if; when s5=> if input = '1' then state <= s2; else state <= s4; end if; when s6=> if input = '1' then state <= s3; else state <= s0; end if; when s7=> if input = '1' then state <= s0; else state <= s6; end if; end case; end if; end process; process (state, input) begin case state is when s0=> if input = '1' then output <= "101"; else output <= "110"; end if; when s1=> if input = '1' then output <= "100"; else output <= "111"; end if; when s2=> if input = '1' then output <= "011"; else output <= "000"; end if; when s3=> if input = '1' then output <= "010"; else output <= "001"; end if; when s4=> if input = '1' then output <= "001"; else output <= "010"; end if; when s5=> if input = '1' then output <= "000"; else output <= "011"; end if; when s6=> if input = '1' then output <= "111"; else output <= "100"; end if; when s7=> if input = '1' then output <= "110"; else output <= "101"; end if; end case; end process; process(output) begin case output is when "000"=>ind<="1000000"; when "001"=>ind<="1111001"; when "010"=>ind<="0100100"; when "011"=>ind<="0110000"; when "100"=>ind<="0011001"; when "101"=>ind<="0010010"; when "110"=>ind<="0000010"; when "111"=>ind<="1111000"; end case; end process; end rtl; ДИАГРАММА ПЕРЕХОДОВ ВРЕМЕННАЯ ДИАГРАММА | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||