1 Общий раздел. Электронные импульсные устройства с устойчивыми состояниями. Триггеры

Триггеры — это устройства с двумя состояниями. Они предназначены для запоминания двоичной информации. Использование триггеров позволяет реализовывать устройства оперативной памяти (то есть памяти, информация в которой хранится только на время вычислений). Однако это не единственная их область применения. Триггеры широко используются для построения цифровых устройств с памятью, таких как счётчики, преобразователи последовательного кода в параллельный, последовательные порты или цифровые линии задержки, применяемые в составе цифровых фильтров.

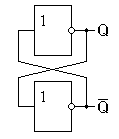

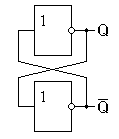

Простейшая схема триггера, позволяющая запоминать двоичную информацию, может быть построена на двух логических инверторах, охваченных положительной обратной связью. Она приведена на рисунке 1.

Рисунок 1 Схема простейшего триггера, построенного на инверторах

В схеме любого триггера может быть только два состояния — на выходе Q присутствует логическая единица и на выходе Q присутствует логический ноль. Если логическая единица присутствует на выходе Q, то на инверсном выходе триггера будет присутствовать логический ноль, который после очередного инвертирования подтверждает уровень логической единицы на выходе Q. И наоборот, если на выходе триггера Q присутствует логический ноль, то на инверсном выходе будет присутствовать логическая единица.

Описанная ситуация на выводах триггера будет сохраняться до тех пор пока включено питание. Но вот вопрос — а как записывать в простейший триггер необходимую нам информацию? Для этого в схеме потребуются входы записи нуля и записи единицы.

1.2. RS-триггеры

RS-триггер получил название по названию своих входов. Вход S (Set — установить англ.) позволяет устанавливать выход Q в единичное состояние. (Устанавливать означает записывать логическую единицу). Вход R (Reset — сбросить англ.) позволяет сбрасывать выход Q (Quit — выход англ.) в нулевое состояние.

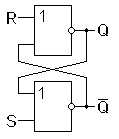

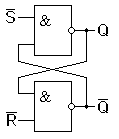

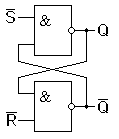

Для реализации RS-триггера воспользуемся логическими элементами "2И-НЕ". Его принципиальная схема, реализованная на логических элементах "2И-НЕ", приведена на рисунке 2.

Рисунок 2 Схема RS-триггера на логических элементах "2И-НЕ". Входы R и S инверсные (активный уровень'0')

Рассмотрим работу изображенной на рисунке 2 схемы триггера подробнее. Пусть на входы R и S подаются единичные потенциалы. Если на выходе верхнего логического элемента "2И-НЕ" Q присутствует логический ноль, то на выходе нижнего логического элемента "2И-НЕ" появится логическая единица. Эта единица подтвердит логический ноль на выходе триггера Q. Если на выходе верхнего логического элемента "2И-НЕ" Q первоначально присутствует логическая единица, то на выходе нижнего логического элемента "2И-НЕ" появится логический ноль. Этот ноль подтвердит логическую единицу на выходе Q. То есть, при единичных уровнях на входах R и S, схема RS-триггера работает точно так же, как и схема триггера на инверторах.

Подадим на вход S триггера нулевой потенциал. Согласно таблице истинности логического элемента "2И-НЕ" на выходе Q появится единичный потенциал. Это приведёт к появлению на инверсном выходе триггера нулевого потенциала. Теперь, даже если снять нулевой потенциал с входа S, на выходе триггера останется единичный потенциал. То есть мы записали в триггер логическую единицу.

Точно так же можно записать в триггер и логический ноль. Для этого следует воспользоваться входом R. Так как активный уровень на входах триггера оказался нулевым, то эти входы — инверсные. Составим таблицу истинности RS-триггера. Входы R и S в этой таблице будем использовать прямые, то есть запись нуля, и запись единицы будут осуществляться единичными потенциалами (таблица 1).

Таблица 1 Таблица истинности RS-триггера.

R

|

S

|

Q(t)

|

Q(t+1)

|

Пояснения

|

0

|

0

|

0

|

0

|

Режим хранения информации (триггером) R=S=0

|

0

|

0

|

1

|

1

|

0

|

1

|

0

|

1

|

Режим установки триггера в единичное состояние S=1

|

0

|

1

|

1

|

1

|

1

|

0

|

0

|

0

|

Режим записи нуля в триггер R=1

|

1

|

0

|

1

|

0

|

1

|

1

|

0

|

*

|

R=S=1 запрещенная комбинация

|

1

|

1

|

1

|

*

|

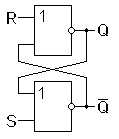

RS-триггер можно построить и на логических элементах "2ИЛИ-НЕ". Схема RS-триггера, построенного на логических элементах "2ИЛИ-НЕ" приведена на рисунке 3. Единственное отличие в работе этой схемы триггера будет заключаться в том, что его сброс и установка будет производиться единичными логическими уровнями.

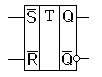

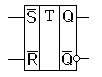

Так как RS-триггер при построении его на логических элементах "2И-НЕ" и "2ИЛИ-НЕ" работает одинаково, то его условно-графическое изображение на принципиальных схемах тоже одинаково. Условно-графическое изображение RS-триггера на принципиальных схемах приведено на рисунке 4.

Рисунок 3 Схема простейшего RS триггера на логических элементах "2ИЛИ-НЕ". Входы R и S прямые (активный уровень '1')

Рисунок 4 - Условно-графическое обозначение RS-триггера

Для измерения логических уровней на выходе триггера чаще всего применяются логические пробники, в качестве которых в простейшем случае можно использовать светодиод с токоограничивающим резистором. В качестве источника логического сигнала можно применить механические тумблеры.

|

Скачать 1.75 Mb.

Скачать 1.75 Mb.