КР по Микропроцессорным системам. МПС. 1. Расставьте числа в порядке возрастания и объясните свой выбор

Скачать 0.96 Mb. Скачать 0.96 Mb.

|

|

1. Расставьте числа в порядке возрастания и объясните свой выбор; 18210 ВС16 1558, 11010112. Для сравнения числа необходимо представить в одной системе счисления. В случае 16-ричной и 8-ричной систем перевод в двоичное представление простой – с использованием тетрад и триад соответственно: ВС16 = 1011 11002 = 101111002 1558 = 001 101 1012 = 11011012 18210 = 101101102 Далее сравнение производим следующим образом. Начиная со старшего разряда, ищем первый несовпадающий. У какого числа значение этого разряда больше – то и больше.

2. Выполните арифметические операции над двоичными числами, используя обратный код: Вычитание в обратном коде эквивалентно сложению с обратным кодом отрицательного числа. а) 10001012 – 11010012. Числа в обратном коде: 10001012 : 0.1000101 11010012 : 1.0010110

Отрицательное число, прямой код результата: 0100100 = 36 В десятичном коде: 69 – 105 = – 36 Ответ верный. б) 11110012 –10111102. Числа в обратном коде: 11110012 : 0.1111001 10111102 : 1.1000001

Перенос из знакового разряда добавим в младший: 0.0011010 + 0.0000001 = 0.0011011 = 27 В десятичном коде: 121 – 94 = 27 3. По таблице работы логического устройства запишите СДНФ:

3а. Получите минимальную форму (МДНФ) методом диаграмм Вейча. Минимизация булевой функции методом диаграммы Вейча y  : :

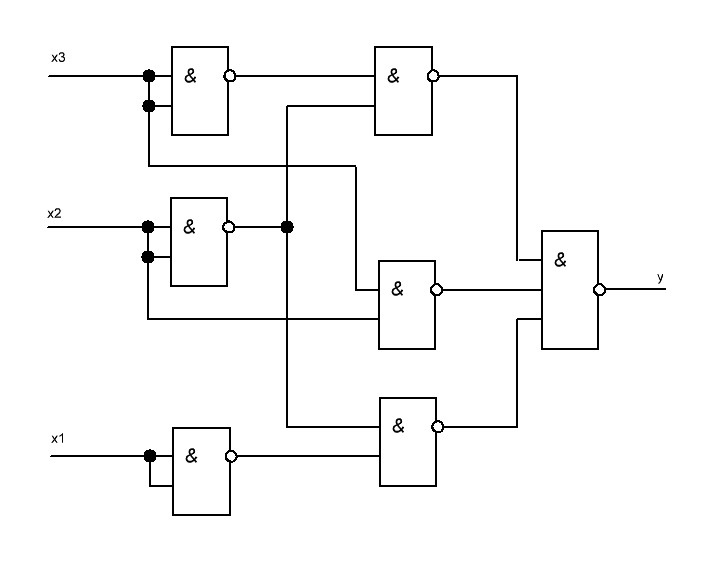

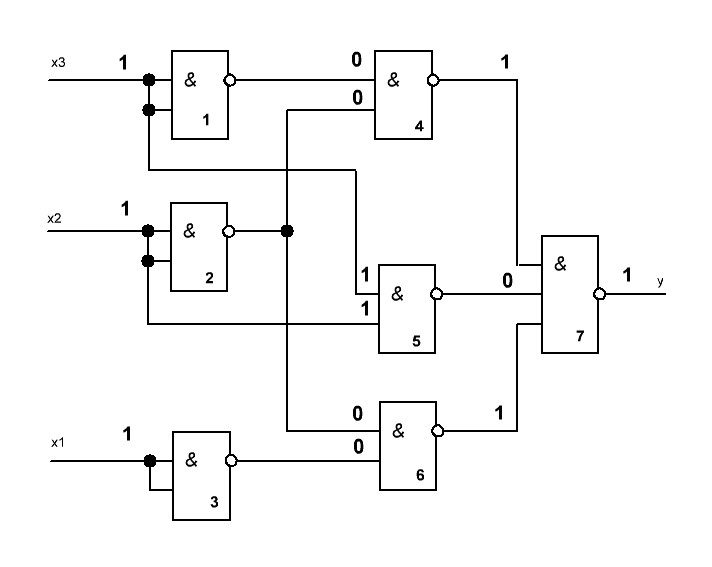

3б. Постройте логическую схему устройства в базисе И-НЕ. Для реализации схемы устройства в базисе И-НЕ преобразуем полученное выражение, используя законы де Моргана. Для реализации схемы потребуется три элемента 2И-НЕ и один 3И-НЕ, а также три инвертора (элементы 2И-НЕ с объединенными входами).  Зв. Проведите анализ работы полученной схемы при х1=1, х2=1, х3=1. По таблице истинности Проверим правильность реализации схемы, подав на ее входы соответствующую комбинацию.  Как видно из рисунка, схема работает правильно. На выходах инверторов (ЛЭ 1-3) – уровни логического нуля, поэтому на входах 4 и 6 ЛЭ – низкие уровни, соответственно на выходах – высокие (уровни логической 1). На обоих входах ЛЭ 5 – уровни логической 1, поэтому на его выходе уровень логического нуля. Этот уровень и обусловливает уровень логической 1 на выходе ЛЭ 7 и, соответственно, на выходе у схемы. 4. Нарисуйте символическое изображение и таблицу работы двухступенчатого RS - триггера. В какое состояние перейдет триггер, если на его входы последовательно подавать сигналы:

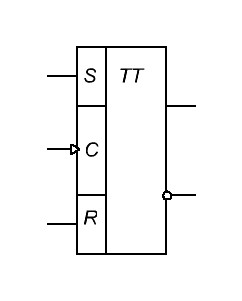

Условное графическое изображение триггера приведено на следующем рисунке.  Таблица работы двухступенчатого RS – триггера

В соответствии с логикой работы двухступенчатого RS – триггера, описанной в таблице, триггер будет последовательно, при подаче приведенных в таблице уровней входных сигналов, принимать следующие состояния:

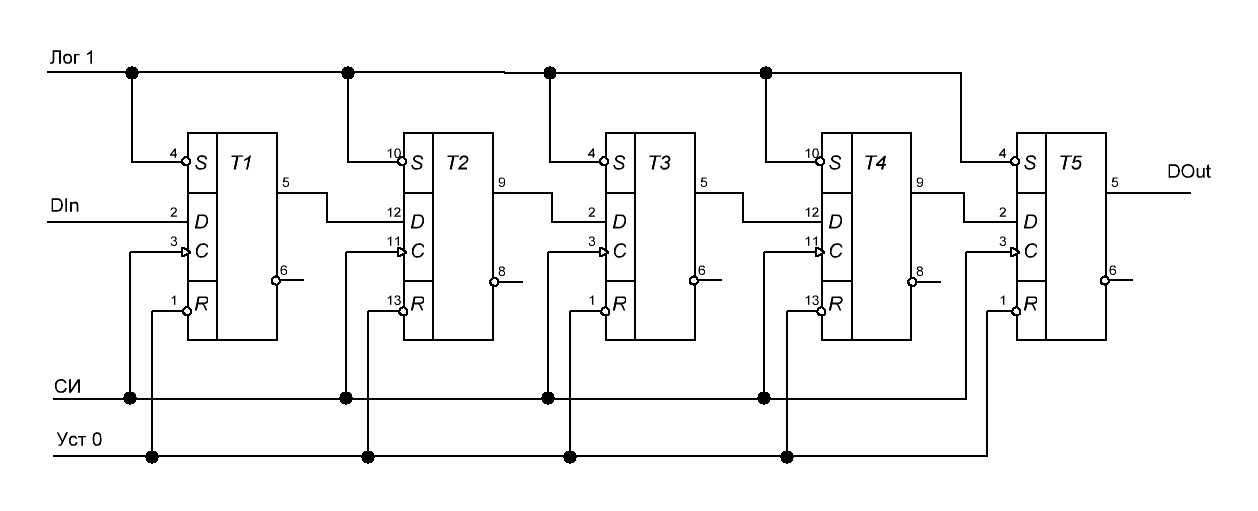

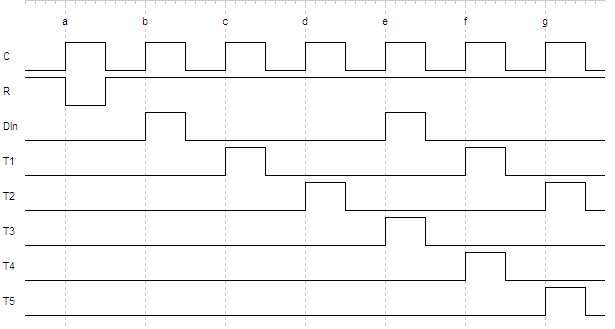

Конечным состоянием триггера будет 0. 5. Постройте схему регистра из D - триггеров для записи числа 1810, начиная с цифры младшего разряда. Составьте таблицу состояний его триггеров, показывающую запись отдельных цифр. Число 1810 = 100102, то есть содержит 5 разрядов. Регистр должен содержать соответствующее число триггеров. Будем располагать старший разряд слева, младший справа, соответственно это будет регистр со сдвигом вправо. Записываемое в регистр число для схемы несущественно, и функциональная схема регистра имеет вид, показанный на рисунке ниже.  Изменение состояний триггеров регистра показано в табл.5.1. Таблица 5.1.

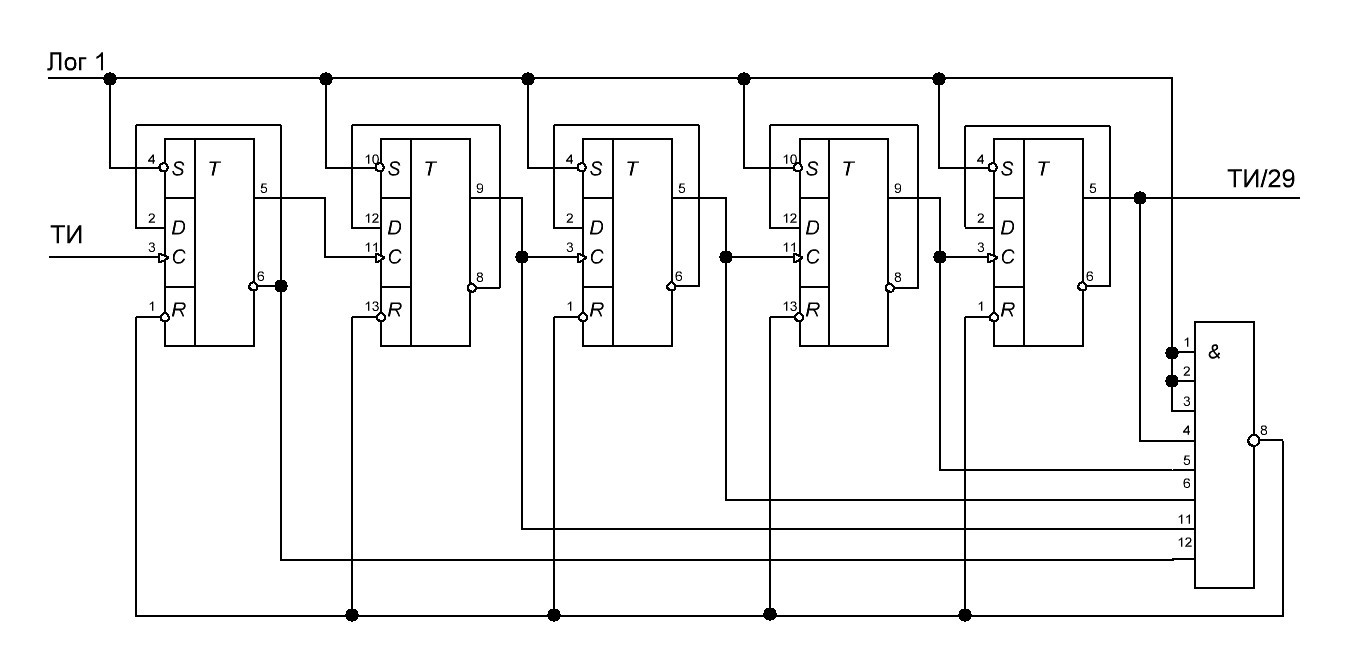

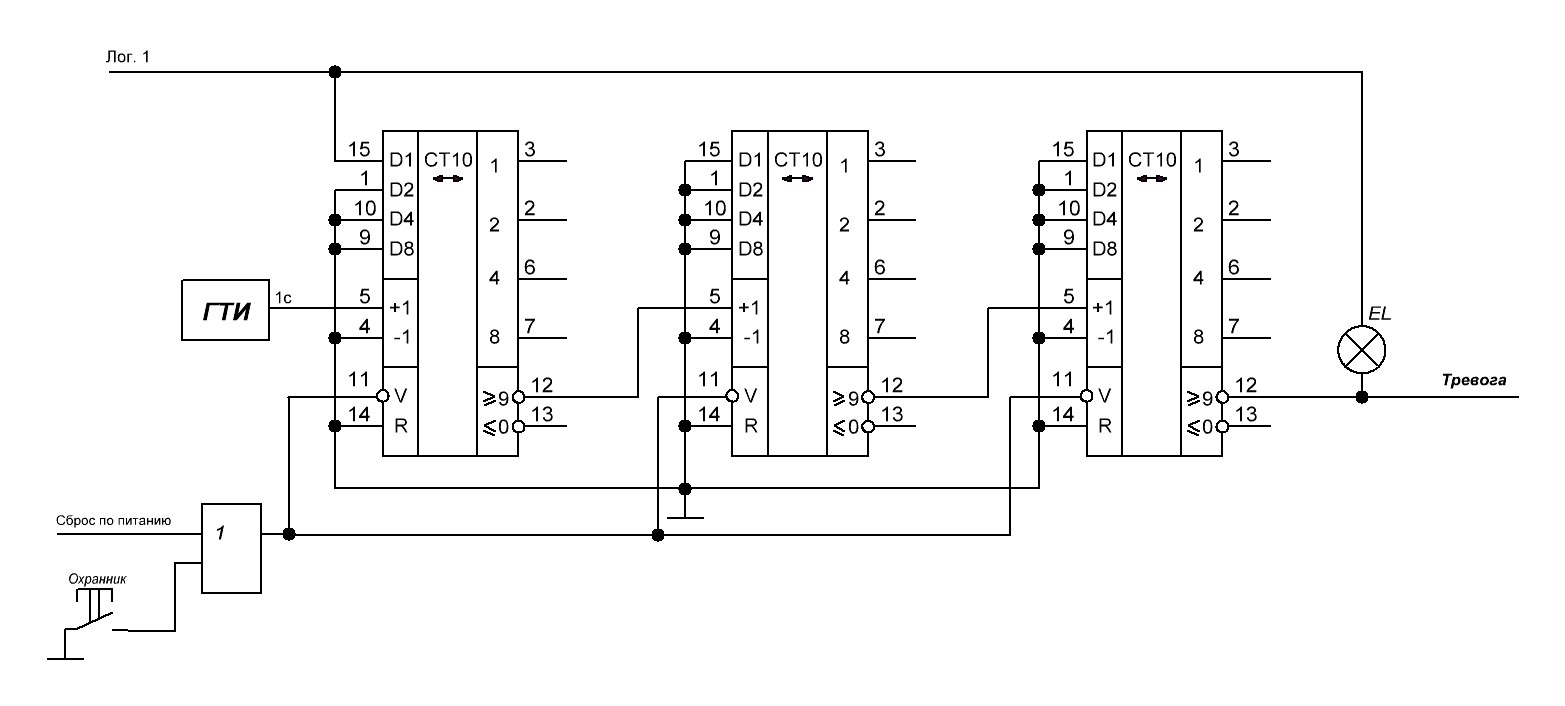

Временная диаграмма работы регистра при записи числа 18 показана на следующем рисунке.  6. Постройте схему суммирующего счетчика из Т-триггеров емкостью 29. Возможны, по меньшей мере, два варианта построения счетчика. Первый – составить таблицу переходов из состояний от 0 до 28, и синтезировать схемы возбуждения входов триггеров. Это длинный и довольно громоздкий путь. Второй – выделить с помощью логической схемы состояние, следующее за последним разрешенным, и выходным сигналом этой схемы сбрасывать триггеры счетчика в 0 (начальное состояние). При втором подходе возникает кратковременное «лишнее» состояние – на время формирования сигнала сброса и установки триггеров в 0. В нашем случае выделяемое состояние 30 = 111102. Таким образом, для реализации счетчика из Т-триггеров емкостью 29 необходимо 5 Т-триггеров и один 5-входовый элемент И (И-НЕ – в зависимости от полярности сигнала сброса триггеров).  7. Разработайте логическую схему устройства контроля бдительности охранника. Если в течение 15 минут охранник не нажал на кнопку - дается сигнал тревоги. Указание: При нажатии на кнопку происходит обнуление счетчика, который подсчитывает секундные импульсы с генератора и запрограммирован до требуемого времени. Схема представляет собой счетчик до 15х60=900 (секунд), переполнение которого вызывает подачу сигнала тревоги. Сброс счетчика в исходное состояние производится нажатием кнопки охранником. В качестве счетного устройства возможно использование двоично-десятичного счетчика 555ИЕ6. Соединение трех разрядов последовательно позволяет получит требуемый коэффициент пересчета. ИМС 555ИЕ6 представляет собой реверсивный двоично-десятичный счетчик (один разряд). Требуемая функциональность может быть получена как в режиме прямого, так и обратного счета. В первом случае начальное состояние должно быть равно 100, во втором – 900. Реализация схемы устройства контроля бдительности охранника в режиме прямого счета приведена на следующем рисунке.  8. Найдите по справочнику микросхему К555ИД4. Нарисуйте се условное изображение и выпишите параметры (с учетом обозначения). Справочные данные на микросхему 555ИД4. | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||