14. 05 Цифровой ключ на полевом транзисторе

Скачать 0.5 Mb. Скачать 0.5 Mb.

|

|

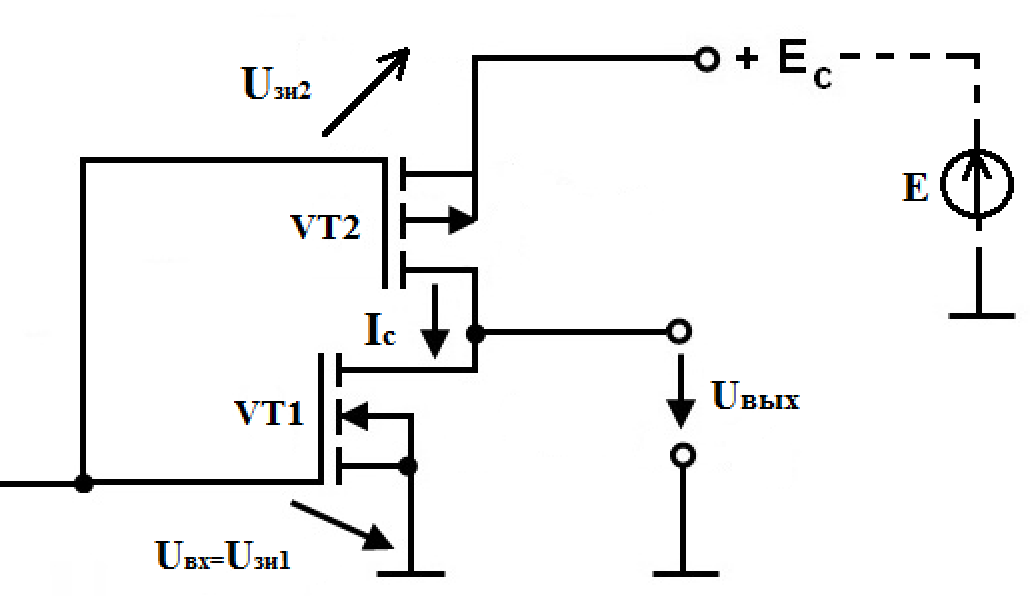

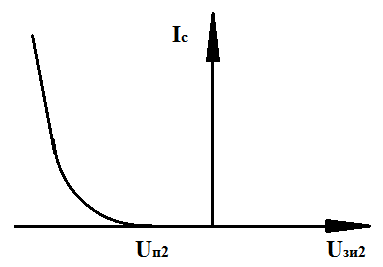

14.05 Цифровой ключ на полевом транзисторе Полевой транзистор, как и биполярный транзистор широко используется в полевых схемах. В цифровом ключе обычно используют МОП транзисторы с индуцированным каналом. Ключ на МОП транзисторах с динамической нагрузкой Ключ на МОП транзисторах можно выполнить с резистивной нагрузкой, подобно ключу на биполярном транзисторе. Если ключи на полевых транзисторах выполняются по интегральной технологии то технологически целесообразнее применять так называемую динамическую нагрузку. В качестве нагрузки ключевого МОП транзистора оказывается более выгодно второй МОП транзистор канал которого всегда открыт, а сопротивление канала остаётся почти постоянным.  Сток-затворная характеристика  При использовании в цифровых устройствах ключа на МОП транзисторах реализуют функцию инвертора логического элемента НЕ. Вольт-амперная характеристика      Ключ на комплементарных МОП- транзисторах КМОП. Комплементарный/ дополняющий/ подобный - ключ с минимальным потреблением энергии от источника питания, строится на комплементарной паре ПТ ( дополняющей дуг друга паре ПТ). Используется два МОП транзистора с одинаковыми характеристиками, но с различным типом проводимости канала. Схема оказывается симметричной, и когда один из транзисторов выполняет роль замкнутого ключа, другой – размокнут и выполняет роль нагрузочного сопротивления и наоброт.    Уравнение по второму закону Кирхгофа. Uзи2 - Uзи1 = - Е Uзи2 = Uзи1 - Е – связь между Uзи2 и Uзи1

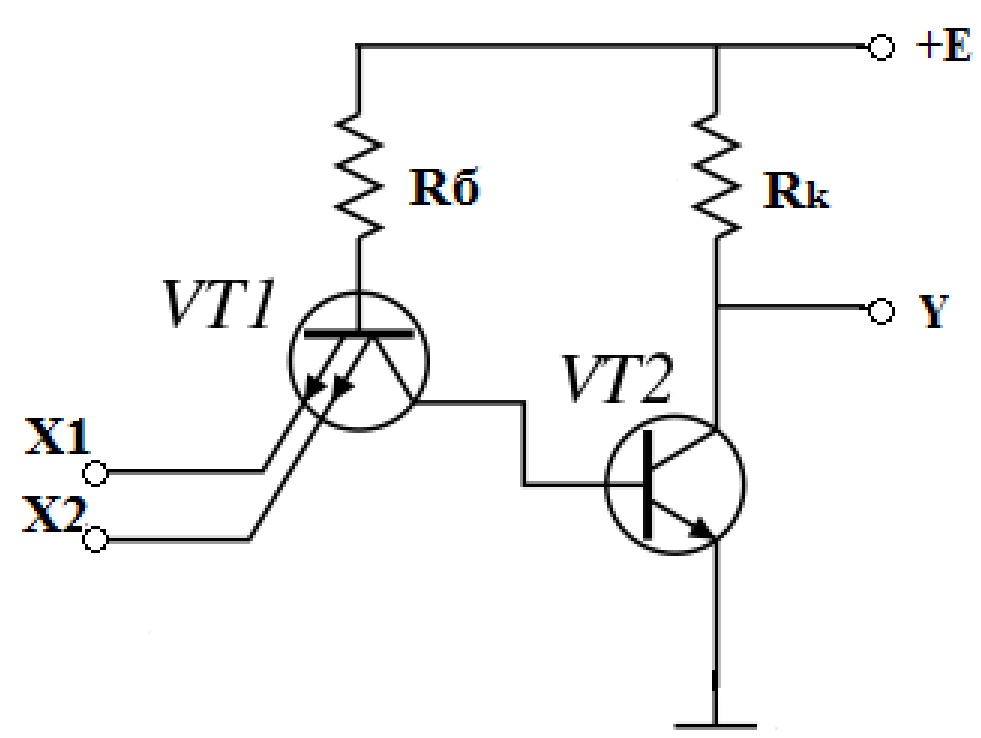

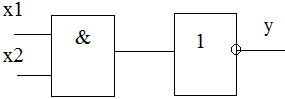

Таким образом, ключ КМОП выполняет роль инвертора, размах логического сигнала U питания, но при любом логическом логическом состоянии ток через этот ключ равен 0, так как один из транзисторов всегда закрыт. В статическом состоянии (любом) схема не потребляет энергии от источника питания( - это особенность КМОП – большое достоинство перед другими) Недостатки: во время переключения через транзисторы протекает ток, обусловленный перезарядом собственных емкостей транзисторов и емкостью нагрузки , поэтому с ростом частоты переключения потребление энергии схемы увеличивается. Эти ёмкости относительно велики, и недостатком таких ключей – сравнительно низкая частота переключения. Ключи на инверторных МОП транзисторах с каналами n, p типа и на комплементарных транзисторах лежат в основе интегральных полевых технологий, соответственно обозначаемых n-МОП, p-МОП и КМОП технологии. Схемотехника базовых логических элементов Логические элементы И, ИЛИ, НЕ – представляют собой основные базовые логические элементы. И-НЕ, ИЛИ-НЕ (ещё базисы). Из таких элементов можно собирать устройства, выполняющие сколь угодно сложные функции. Для современной цифровой схемотехники характерно широкое использование двух базисов – И-НЕ, ИЛИ-НЕ. Для их реализации логические элементы строят так, состоящими как бы из двух схемных частей: 1 часть схемы выполняет операцию И или ИЛИ, эта часть схемы входная логика; 2 часть схемы – инвертор, выполняющий операцию НЕ. Входная логика может быть выполнена на различных элементах, полупроводниковых элементах (диодах, БТ и ПТ). В зависимости от вида полупроводниковых элементов, применяемых для изготовления входной логики и инверторов различают следующие виды: ДТЛ – диодно-транзисторная логика ТТЛ – транзисторно- транзисторная логика ТТЛШ – транзисторно-транзисторная логика с диодами Шоттки ЭМЛ – эмиттерно-связанная логика ИИЛ – интегрально-инжекционная логика (И2Л) n-МОП p-МОП КМОП - комплементарная структура металл-оксид-полупроводник Логический элемент ТТЛ (И-НЕ) Простейший логический элемент транзистоно-транзстороной логики строится на базе многоэмиттерного транзистора, выполняющего функцию И и транзисторного ключа, выполняющего функцию НЕ. Упрощенная схема такого элемента.  Если х1=1 и х2=1 – высокий уровень U, то эмиттерные выходы транзистора VT1 закрыты, открывается базо-коллеторный переход транзистора VT1, и его ток I открывает и насыщает ключевой транзистор VT2, при этом на выходе формируется низкий уровень U. х1=х2=1 Y=0 х1=0, х2=1 Y=1 При низком уровне сигнала на любом из входов, I будет перетекать через советующий эмиттер, то есть переключится в выходную цепь выходного сигнала. Базовый ток VT2 соответственно его Ik окажется равным 0, VT2 будет закрыт, при этом на выходе высокий уровень U. Можно составить таблицу истинности и проследить, что двувходовой элемент – 2 И-НЕ элемент. Для повышения экономичности и быстродействия выходной транзистор выполняют на базе более сложной схеме инвертора. Особенности выходов микросхем: Под выходами интегральных микросхем понимается их выходы, на которых реализована какая- либо логическая функция входных переменных, либо присутствуют считываемые данные или адреса, либо выражаются сигналы протокола обмена с другими ИМС в сложных системах. Количество выходов определяется назначением и сложностью ИМС. В любой данный момент состояние выходов является либо логическим 0, либо логической единицей, либо может находиться в так называемом импедансном состоянии. Рассмотрим эти особенности на основе ТТЛ микросхем. Различают следующие выходы в соответствии с их особенностями: -стандартный -выход с повышенной нагрузочной способностью -выход с открытым эмиттером -выход с открытым коллектором -выход с высокоимпедансным состоянием Стандартный выход: В цифровых устройствах выходы одной ИМС подключаются к другим ИМС. Одним из важных параметров ИМС является коэффициент разветвления. Коэффициент разветвления равен числу ИМС той же серии, входы которых можно подключить к выходу данной ИМС, не нарушая ее нормального функционирования. Этот параметр определяет нагрузочную способность ИМС. Для обычных он равен ИМС от от 2 до 200. Для стандартного логического элемента ТТЛ 155 серии коэффициент разветвления равен 10. Объясняется это следующим образом- при логическом нуле на выходе транзистор открыт, I0вых=16 мА, I0вх=1,6 мА. Выход с повышенной нагрузочной способностью (ПНС): Некоторые микросхемы выпускают с ПНС выходов, это буферные логические элементы. Микросхемы 155 серии с ПНС обеспечивают I0вх=48 мА, Кразв=30. Элемент 2 И-НЕ:   Элемент с ПНС:  18.05 Т-триггер. Т-триггер, также называемый счетным, имеет только один вход – тактовый вход Т – и меняет свое состояние на противоположное по фронту или срезу каждого нового импульса. Условное графическое обозначение Т-триггера:  Таблица состояний:

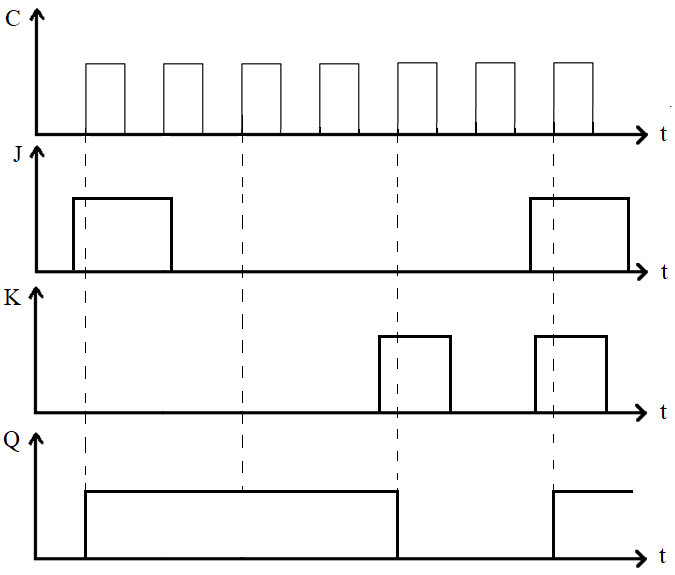

Qn+1= Q̅nT+ QnT̅ Qn+1=Qn⊕T Т-триггер может быть реализован на D-триггере с динамическим управлением и RS-триггере с динамическим управлением. D-триггер:   Каждый раз по фронту или по срезу тактового сигнала Т изменяется напряжение на выходе Q, частота изменения в 2 раза ниже частоты на входе. Это свойство используется при построении двоичных счетчиков. RS-триггер:  JK-триггер. JK-триггер является наиболее универсальным из триггеров. Он строится на базе RS-триггера с динамическим тактовым входом. В отличие от RS-триггера в JK-триггере устранено запрещенное состояние J=K=1. Вход J является аналогом S входом RS-триггера (служит для установления логической единицы), K – аналог R входа RS-триггера (служит для установления логического нуля). При совпадении логических единиц на информационных входах J и K данный триггер работает как счетный триггер (режим переключения), меняет свое состояние на противоположное при каждом новом такте. Логическая единица на входе J при наличии тактирующего импульса устанавливает триггер в состояние 1 (режим установки состояния 1), логическая единица на входе К переводит триггер в состояние 0 при новом тактирующем импульсе (режим записи 0 или сброс). При наличии логических нулей на входах J и K тактирующий импульс не меняет состояние триггера (режим хранения).   Условное графическое обозначение:  Таблица состояний:

Qn+1=Q̅nJ+QnK̅ На основе универсального JK-триггера могут быть построены другие триггеры. Для использования в качестве RS-триггера вход S принимается за вход J, вход R – за вход K. При этом дополняется запрещенное состояние R=S=1. Для использования в качестве Т-триггера на входах J и K устанавливаются логические единицы, входы присоединяются к шине питания. Для использования в качестве D-триггера вход D устанавливается как D=J=K̅.  Счетчики. Счетчик – последовательное цифровое устройство, предназначенное для счета входных импульсов и фиксации их числа в двоичном коде. Счетчики строятся на основе n однотипных, связанных между собою схем. Каждая схема в общем случае состоит из триггера и некоторой комбинационной схемы. Комбинационная схема предназначена для формирования сигналов управления триггера. Практически каждая цифровая система содержит несколько счетчиков. Основной параметр счетчика – модуль счета (М), называемый также коэффициентом счета импульса (КСИ). Модуль счета – максимальное число импульсов, которое может быть сосчитано счетчиком. Результат счета в счетчике записывается в двоичном коде. Максимальное число, которое может быть записано в счетчике равняется 2N-1, где N – число разрядов. М – максимальное число импульсов, которое можно сосчитать, М=2N. Счетчики классифицируются по различным признакам:

Асинхронные двоичные счетчики представляют собой цепочку из счетных триггеров, у которых выход предыдущего триггера соединен с входом последующего. В синхронном двоичном счетчике счетный импульс воздействует одновременно на все триггеры счетчика. Асинхронные счетчики. Асинхронные счетчики – это суммирующие счетчики с последовательным переносом. Наиболее просто схемы счетчиков реализуются на базе синхронных Т-триггеров. Рассмотрим схему трехразрядного счетчика на Т-триггерах, являющихся суммирующими.  Временные диаграммы:  Таблица состояний:

В данном случае триггеры осуществляют счет импульсов от 0 до 7. Они различны по коду. Число подсчитанных импульсов может быть увеличено при подключении к входу счетчиков дополнительных разрядов. Первый триггер соответствует младшему разряду. Его входной сигнал поступает на вход следующего по старшинству разряда и т.д. Производится предварительная установка всех триггеров в состояние логического нуля. Состояние разрядов соответствует записи числа поступивших импульсов в двоичном коде. После записи максимального числа счетчик обнуляется и начинается дальнейший цикл счетов. Таким образом, счетчик реализует суммирование. Каждый триггер делит частоту импульса на 2, что используется в делителях частоты. Аналогичная схема на JK триггерах:  Асинхронный счетчик с последовательным переносом, по модулю 10 В ряде случаев возникает необходимость возврата счетчика в состояние логического нуля (исходное состояние). Q1 = Q2 = Q3 = 0/ После записи в счетчике числа меньшего чем 2N -1, M < 2N -1. Для осуществления используется метод управляемого сброса. Для этого формируется сигнал сброса триггеров состояния логического нуля с появлением на выходе счетчика кода, совпадающего с требуемым модулем счета. Вводится цепь обратной связи. Для примера рассмотрим асинхронный счетчик по модулю 10. 2N > M; 24 > M; 24=16>10 => 4 триггера.

Вычитающий счётчик с последовательным переносом. В ряде случаев становится необходимым считать от больших чисел к меньшим. С этим справляются вычитающие счётчики или счётчики обратного действия. Вычитающий счётчик с последовательным переносом строится аналогично суммирующему на основе Т триггеров.  Временная диаграмма  Таблица истинности

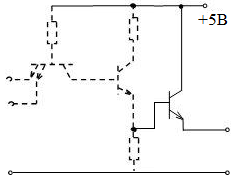

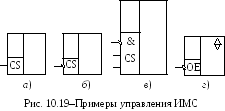

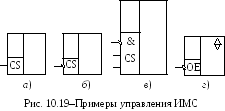

28.05 Особенности стандартных выходов Выход с открытым коллектором Рассматриваем на ТТЛ логике  УГО  Свободный коллектор выхода транзистора является выходом интегральной микросхемы и подключен к источнику питания через нагрузку.     Логический элемент с открытым коллектором позволяет осуществить непосредственное соединение (пайку) выходов нескольких микросхем между собою, при этом обеспечивается реализация дополнительных логических функций. Логическая функция реализуется путем внешних соединений нескольких выходных отдельных микросхем называется монтажной логикой. Логическая единица на выходе F появится только тогда когда закрыты все выходы транзисторных элементов, свободные коллекторы которых подключены к резистору R. С объединением выходов микросхем реализуется логическая операция умножения - монтажное И.  Выход с открытым эмиттером  УГО   Нагрузка включается между свободным эмиттером и корпусом. Для получения монтажной логики используются дополнительный резистор. Если мы имеем единицу на каком-либо входе:  Выход с третьим состоянием В связи с развитием информационной техники мы имеем интегральные микросхемы с тремя состояниями. У них в дополнение к обычным состоянием логического нуля и логической единицы на выходе может быть третье состояние - z состояние или высокоимпедансное состояние. Посредством дополнительных транзисторов микросхема в z состоянии своим выходом оказывается полностью отключенной от нагрузки. При использовании логических элементов с тремя состояниями их выходы можно объединить вместе. Управление работой микросхем организуется так, чтобы в любой момент времени все микросхемы кроме одной находились в высоко импедансом состоянии. То есть удается по одной шине передавать в разных направлениях информацию от нескольких источников, следовательно уменьшается количество линий связи между устройствам. Управление состоянием по входу EZ/OE. УГО  Управление микросхемами Сложные по выполняемым функциям интегральные микросхемы. Часто снабжаются функциями управления по входу и по выходу. Управление входами представляет собой включение или выключение интегральных микросхем или стробирования. Управление сигналами - CS(cristall select)/IE(input enable). Различают прямое управление:  и управление с инверсией:  При прямом управлении: CS=1 IE=1 то работает CS=0 IE=0 то выходы отключены При инверсном управлении: CS=0 IE=0 то работает CS=1 IE=1 то выходы отключены В включенном состоянии на выход может имеет либо высокий либо низкий уровень. Управление выходами интегральных микросхем - управление состоянием z осуществляется с подачей на вход управляющих сигналов EZ(enable z) и OE(output enable).  При прямом управлении: EZ=0 OE=1 при обычном режиме EZ=1 OE=0 при высокоимпедансном режиме При инверсном управлении: EZ=1 OE=0 при обычном режиме EZ=0 OE=1 при высокоимпедансном режиме Основные параметры цифровых интегральных микросхем. 1)Напряжение источника питания. 2)Уровни напряжений соответствующие состояниям логического нуля и логической единицы. 3)Помехоустойчивость (приводится к наименьшему значению). 4)Величины входных и выходных токов для уровней логическим нулём и логической единицей. Характеризуют нагрузочную способность интегральных микросхем. 5) Потребляемая мощность, потребляемый ток. 6) Время задержки распространения сигнала. Характеризует быстродействие. 1) U0 - логический ноль   U1 - логическая единица    - входной ток логического нуля - входной ток логического нуля  - входной ток логической единицы - входной ток логической единицы - выходной ток логического нуля - выходной ток логического нуля  - выходной ток логической единицы - выходной ток логической единицы2) Напряжения логического нуля и логической единицы приводятся для случая предельной нагрузки на интегральной микросхеме при максимальном коэффициенте развертывания. Величины входных и выходных токов уровней логического нуля и логической единицы определяют нагрузочную способность интегральной микросхемы. Для количественной характеристики используют два коэффициента: 1)коэффициент объединения по входу Kоб Он равен максимальному числу выходов однотипных логических элементов, которые могут быть одновременно подключены к входу данного логического элемента. 2)коэффициент развертывания по выходу Kразв Он равен максимальному числу входов однотипных логических элементов, которые могут быть одновременно подключены к выходу данного логического элемента. При типовых задачах для ТТЛ элементов Kоб  2-8 2-8Kразв  4-10 4-10При повышенной нагрузочной способности Kразв  20-30 20-303)Помехоустойчивость характеризует способность правильно функционировать при наличии помех. Количественно определяется максимально допустимым напряжением помехи. 5) Потребляемая мощность определяется как среднее арифметическое мощностей потребляемых логическими элементами в состоянии логического нуля и логической единицы:  В сложном цифровом устройстве половина логических элементов находится в состоянии логического нуля, половина в состоянии логической единице. Потребляемая мощность зависит от частоты переключений. Необходимо учитывать потребляемую мощность при максимальной частоте. Одними из параметров определяющих себестоимость различных микросхем являются полярность и величина напряжения источника питания. Например микросхемы на ТТЛ и МОП логике совместимы при одном напряжении питания Uпит=+5В. 6)Важнейшим данным параметром микросхем является время задержки распространения сигнала tзад. Это время принято оценивать как среднее значение задержки фронта и времени задержки среза при отсчете на уровне половины размаха сигнала.   Размерность времени задержки обычно единицы наносекунд. В справочнике указывается максимальное время задержки распространения информации от входа до выхода. Для сравнения между собою используют интегральный параметр – энергию переключения. Wпер=Pперtзад пДж=мВт*нсек |