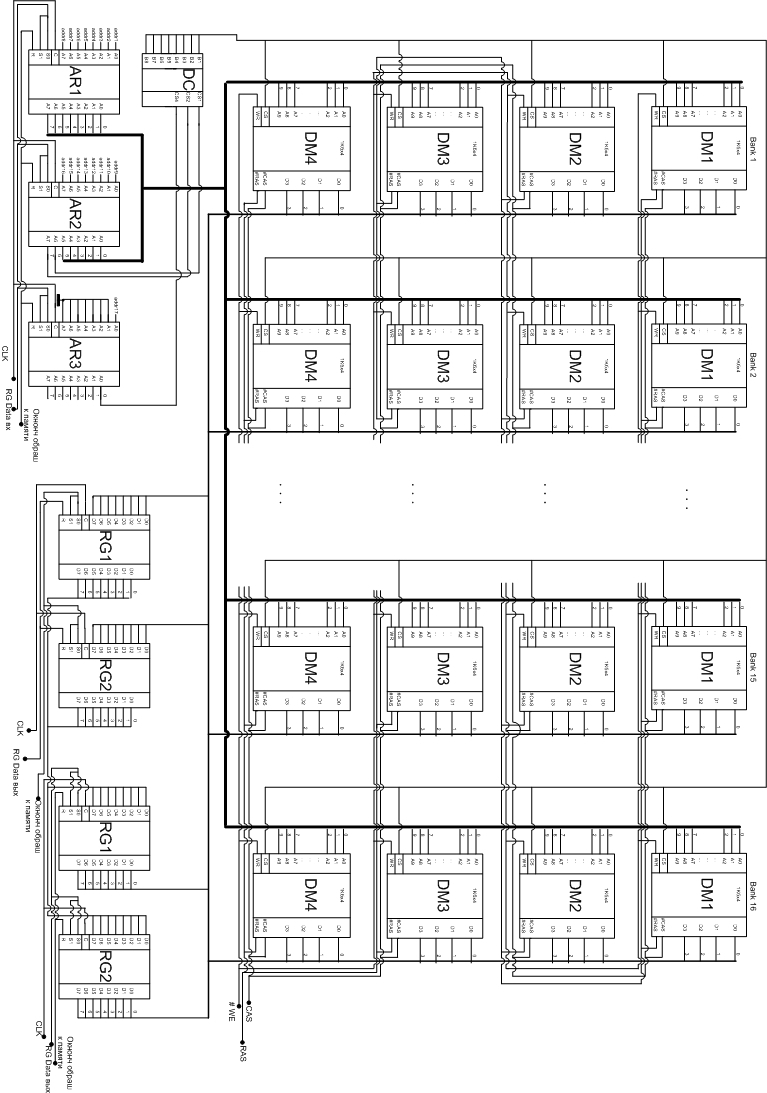

Структурная схема запоминающего устройства. 16 Кб разрядность шины данных 16 бита

Скачать 1.23 Mb. Скачать 1.23 Mb.

|

|

Режим записи: В этом режиме на шину адреса выставляется адрес, а на шину данных выставляется данные и подаётся управляющий сигнал записи ЗАП. По переднему фронту сигнала ЗАП устанавливается триггер записи ТЗАП. По сигналу #ЗАП в RG Data вх происходит запись в регистр модуля RgD вх, по сигналу #ЗАП в RG Add вх происходит запись в регистр модуля RgA вх. По переднему фронту сигнала ЗАП устанавливается в «1» триггер Т1. Единичное состояние триггера Т1 устанавливает и поддерживает в единичном состоянии триггер Т2 до окончания режима обращения к памяти. Единичное состояние триггера Т2 и синхроимпульсы CLK обеспечивают работу счётчика CT. Переключение счётчика CT задаёт комбинацию на входе дешифратора DC. Дешифратор при наличии определённой комбинации сигналов на входе выдаёт единичное состояние на одном из выходов. Выходы дешифратора DC являются тактами работы нашего модуля T1-T6. При единичном состоянии триггера ТЗАП и наличии сигнала Т1 триггер WE устанавиливается в рабочее состояние. По единичному фронту сигнала Т2 устанавливается сигнал RAS – сигнал разрешения выбора строки. RAS сбрасывается по окончании записи в матрицу при единичном значении сигнала T4. При наличии сигнала T3 устанавливается сигнал CAS, и сбрасывается по окончании этого сигнала. Сигнал CAS разрешает выборку столбца. Режим обращения к памяти длится 5 тактов, а в начале шестого такта по сигналу T6 вырабатывается сигнал окончания обращения к памяти. Режим чтения: В этом режиме чтения на шину адреса выставляется адрес и подаётся управляющий сигнал чтения ЧТ. Триггер записи ТЗАП в этом режиме находится в «0». По сигналу #ЗАП в RG Add вх происходит запись в регистр RgA. По переднему фронту сигнала ЧТ устанавливается в «1» триггер Т1. Единичное состояние триггера Т1 устанавливает и поддерживает в единичном состоянии триггер Т2 до окончания режима обращения к памяти. Единичное состояние триггера Т2 и синхроимпульсы CLK обеспечивают работу счётчика CT. Переключение счётчика CT задаёт комбинацию на входе дешифратора DC. Дешифратор при наличии определённой комбинации сигналов на входе выдаёт единичное состояние на одном из выходов. Выходы дешифратора DC являются тактами работы нашего модуля T1-T6. В режиме чтения триггер записи ТЗАП находится в нуле, его нулевое состояние блокирует установку триггера WE, поэтому сигнал #WE равен единице. По единичному фронту сигнала Т2 устанавливается сигнал RAS, сбрасывается по окончании записи в матрицу при единичном значении сигнала T4. При наличии сигнала T3 устанавливается сигнал CAS, и сбрасывается по окончании этого сигнала. При наличии сигнала T3 и сигнала #ТЗАП, равном единице, на схеме И-НЕ вырабатывается запись в RgD вых, разрешающий запись считанных из матрицы данных в выходной регистр данных. Режим обращения к памяти длится 5 тактов, а в начале шестого такта по сигналу T6 вырабатывается сигнал окончания обращения к памяти. Временная диаграмма управления памятью ЗАПИСЬ ЧТЕНИЕ

Функциональная схема блока управления памятью    | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||