Архитектура вычислительных систем. Архитектура вычислительных систем Способы ускорения традиционных архитектур вс

Скачать 1.55 Mb. Скачать 1.55 Mb.

|

|

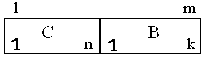

Содержание Введение Архитектура вычислительных систем Способы ускорения традиционных архитектур ВС Операционные конвейеры Расслоение памяти Кэш-память Типовая структура кэш-памяти Способы размещения данных в кэш-памяти Мультипоточность данных Сокращенные системы команд Литература Введение Вычислительная система – это совокупность аппаратных (hardware) и представленных в определенном формате математических средств (software), реализующих процесс решения задач. Другими словами, это вычислительная среда, на которую отображаются (в которой моделируются) задачи реального мира. Для моделирования реальных задач можно использовать два подхода, определяющих архитектуру вычислительной среды. Первый подход, так называемый фундаментальный, базируется на классической математике, как средстве описания «идейной» сути объекта исследования. Это аналитический подход, предполагающий декомпозицию моделируемого объекта на элементарные явления, описываемые простыми уравнениями, имеющими ясную физическую интерпретацию, и дальнейшее объединение этих уравнений в единую математическую модель в соответствии с законами, присущими данной предметной области. Построение и исследование таких моделей может выполняться в среде цифровой микропроцессорной системы, основанной на принципах архитектуры фон Неймана. Последовательный цифровой принцип вычислений, базирующийся на формальном аппарате алгебры логики, отличается универсальностью, обеспечивает необходимую точность вычислений и как пути повышения их эффективности использует: -увеличение тактовой частоты процессоров; -конвейеризацию выполнения инструкций; -распараллеливание вычислительных структур на уровне команд и на уровне алгоритмов, а также ряд других архитектурных усовершенствований, способствующих повышению эффективности вычислительного процесса. Второй подход, эмпирический, исключает, как базовые, фазу анализа и аналитическое представление модели. Это синтетический подход, при котором объект (задача) моделируется сразу целиком (как «черный ящик») в реальных условиях без выделения идеальных элементарных явлений и проникновения в математическую суть исследуемой задачи. Вычислительной средой, реализующей данный подход, могут быть искусственные нейронные сети (ИНС), лежащие в основе «существенно параллельных» вычислительных систем – нейрокомпьютеров. В идеальной реализации это аналоговый подход с присущей ему высокой скоростью вычислений, но вместе с тем предоставляющий возможность достижения приемлемой точности путем: -повышения мощности нейронной сети (увеличения числа нейронов, количества слоев); -совершенствования ее архитектуры; -применения эффективных процедур обучения; -сочетания с элементами цифровой вычислительной техники. Архитектура вычислительной системы С середины 60-х годов очень сильно изменился подход к созданию вычислительных машин. Вместо разработки аппаратуры и средств математического обеспечения стала проектироваться система, состоящая из синтеза аппаратных (hardware) и программных (software) средств. При этом на главный план выдвинулась концепция взаимодействия. Так возникло новое понятие — архитектура вычислительной системы (ВС). Под архитектурой ВС принято понимать совокупность общих принципов организации аппаратно-программных средств и их основных характеристик, определяющая функциональные возможности вычислительной машины при решении соответствующих типов задач. Архитектура ВС охватывает значительный круг проблем, связанных с созданием комплекса аппаратных и программных средств и учитывающих большое количество определяющих факторов. Среди этих факторов основными являются: стоимость, сфера применения, функциональные возможности, удобство в эксплуатации, а одним из основных компонентов архитектуры считаются аппаратные средства. Архитектуру вычислительного средства необходимо отличать от структуры ВС. Структура вычислительного средства определяет его текущий состав на определенном уровне детализации и описывает связи внутри средства. Архитектура же определяет основные правила взаимодействия составных элементов вычислительного средства, описание которых выполняется в той мере, в какой необходимо для формирования правил взаимодействия. Она устанавливает не все связи, а только наиболее необходимые, которые должны быть известны для более грамотного использования применяемого средства. Так, пользователю ЭВМ не важно, на каких элементах выполнены электронные схемы, схемно или программно исполняются команды и тому подобное. Архитектура ВС действительно отражает круг проблем, которые относятся к общему проектированию и построению вычислительных машин и их ПО. Архитектура ВС включает в себя как структуру, отражающую состав ПК, так и программно – математическое обеспечение. Структура ВС - совокупность элементов и связей между ними. Основным принципом построения всех современных ВС является программное управление. Основы учения об архитектуре вычислительных машин были заложены Джоном фон Нейманом. Совокупность этих принципов породила классическую (фон-неймановскую) архитектуру ВС. Фон Нейман не только выдвинул основополагающие принципы логического устройства ВС, но и предложил ее структуру, представленную на рисунке 1. Внешнее запоминающее устройство    Процессор Арифметико- Управляющее логическое устройство устройство Устройство вывода Устройство ввода        Оперативное запоминающее устройство Рисунок 1. Положения фон Неймана: Компьютер состоит из нескольких основных устройств (арифметико-логическое устройство, управляющее устройство, память, внешняя память, устройства ввода и вывода) Арифметико-логическое устройство – выполняет логические и арифметические действия, необходимые для переработки информации, хранящейся в памяти. Управляющее устройство – обеспечивает управление и контроль всех устройств компьютера (управляющие сигналы указаны пунктирными стрелками). Данные, которые хранятся в запоминающем устройстве, представлены в двоичной форме. Программа, которая задает работу компьютера, и данные хранятся в одном и том же запоминающем устройстве. Для ввода и вывода информации используются устройства ввода и вывода. Современную архитектуру компьютера определяют следующие принципы: Принцип программного управления. Обеспечивает автоматизацию процесса вычислений на ЭВМ. Согласно этому принципу, для решения каждой задачи составляется программа, которая определяет последовательность действий компьютера. Эффективность программного управления будет выше при решении задачи этой же программой много раз (хотя и с разными начальными данными). Принцип программы, сохраняемой в памяти. Согласно этому принципу, команды программы подаются, как и данные, в виде чисел и обрабатываются так же, как и числа, а сама программа перед выполнением загружается в оперативную память, что ускоряет процесс ее выполнения. Принцип произвольного доступа к памяти. В соответствии с этим принципом, элементы программ и данных могут записываться в произвольное место оперативной памяти, что позволяет обратиться по любому заданному адресу (к конкретному участку памяти) без просмотра предыдущих. На основании этих принципов можно утверждать, что современный компьютер - техническое устройство, которое после ввода в память начальных данных в виде цифровых кодов и программы их обработки, выраженной тоже цифровыми кодами, способно автоматически осуществить вычислительный процесс, заданный программой, и выдать готовые результаты решения задачи в форме, пригодной для восприятия человеком. Реальная структура компьютера значительно сложнее, чем рассмотренная выше (ее можно назвать логической структурой). В современных компьютерах, в частности персональных, все чаще происходит отход от традиционной архитектуры фон Неймана, обусловленный стремлением разработчиков и пользователей к повышению качества и производительности компьютеров. Качество ВС характеризуется многими показателями. Это и набор команд, которые компьютер способный понимать, и скорость работы (быстродействие) центрального процессора, количество периферийных устройств ввода-вывода, присоединяемых к компьютеру одновременно и т.д. Главным показателем является быстродействие - количество операций, какую процессор способен выполнить за единицу времени. На практике пользователя больше интересует производительность компьютера - показатель его эффективного быстродействия, то есть способности не просто быстро функционировать, а быстро решать конкретные поставленные задачи. Как результат, все эти и прочие факторы способствуют принципиальному и конструктивному усовершенствованию элементной базы компьютеров, то есть созданию новых, более быстрых, надежных и удобных в работе процессоров, запоминающих устройств, устройств ввода-вывода и т.д. Тем не менее, следует учитывать, что скорость работы элементов невозможно увеличивать беспредельно (существуют современные технологические ограничения и ограничения, обусловленные физическими законами). Поэтому разработчики компьютерной техники ищут решения этой проблемы усовершенствованием архитектуры ВС. Так, появились компьютеры с многопроцессорной архитектурой, в которой несколько процессоров работают одновременно, а это означает, что производительность такого компьютера равняется сумме производительностей процессоров. В мощных компьютерах, предназначенных для сложных инженерных расчетов и систем автоматизированного проектирования (САПР), часто устанавливают два или четыре процессора. В сверхмощных ЭВМ (такие машины могут, например, моделировать ядерные реакции в режиме реального времени, прогнозировать погоду в глобальном масштабе) количество процессоров достигает нескольких десятков. Скорость работы компьютера существенным образом зависит от быстродействия оперативной памяти. Поэтому, постоянно ведутся поиски элементов для оперативной памяти, затрачивающих меньше времени на операции чтения-записи. Но вместе с быстродействием возрастает стоимость элементов памяти, поэтому наращивание быстродействующей оперативной памяти нужной емкости не всегда приемлемо экономически. Проблема решается построением многоуровневой памяти. Оперативная память состоит из двух-трех частей: основная часть большей емкости строится на относительно медленных (более дешевых) элементах, а дополнительная (так называемая кэш-память) состоит из быстродействующих элементов. Данные, к которым чаще всего обращается процессор находятся в кэш-памяти, а больший объем оперативной информации хранится в основной памяти. Раньше работой устройств ввода-вывода руководил центральный процессор, что занимало немало времени. Архитектура современных компьютеров предусматривает наличие каналов прямого доступа к оперативной памяти для обмена данными с устройствами ввода-вывода без участия центрального процессора, а также передачу большинства функций управления периферийными устройствами специализированным процессорам, разгружающим центральный процессор и повышающим его производительность. Рассмотрим несколько способов ускорения традиционных архитектур вычислительных систем. Способы ускорения традиционных архитектур вычислительных систем Операционные конвейеры. Разработчики архитектуры компьютеров издавна прибегали к методам проектирования, известным под общим названием "совмещение операций", при котором аппаратура компьютера в любой момент времени выполняет одновременно более одной базовой операции. Этот общий метод включает два понятия: параллелизм и конвейеризацию. Хотя у них много общего и их зачастую трудно различать на практике, эти термины отражают два совершенно различных подхода. При параллелизме совмещение операций достигается путем воспроизведения в нескольких копиях аппаратной структуры. Высокая производительность достигается за счет одновременной работы всех элементов структур, осуществляющих решение различных частей задачи. Конвейеризация (или конвейерная обработка) в общем случае основана на разделении подлежащей исполнению функции на более мелкие части, называемые ступенями, и выделении для каждой из них отдельного блока аппаратуры. Так обработку любой машинной команды можно разделить на несколько этапов (несколько ступеней), организовав передачу данных от одного этапа к следующему. При этом конвейерную обработку можно использовать для совмещения этапов выполнения разных команд. Производительность при этом возрастает благодаря тому, что одновременно на различных ступенях конвейера выполняются несколько команд. Конвейерная обработка такого рода широко применяется во всех современных быстродействующих процессорах. Конвейеризация увеличивает пропускную способность процессора (количество команд, завершающихся в единицу времени), но она не сокращает время выполнения отдельной команды. В действительности, она даже несколько увеличивает время выполнения каждой команды из-за накладных расходов, связанных с управлением регистровыми станциями. Однако увеличение пропускной способности означает, что программа будет выполняться быстрее по сравнению с простой неконвейерной схемой. Тот факт, что время выполнения каждой команды в конвейере не уменьшается, накладывает некоторые ограничения на практическую длину конвейера. Кроме ограничений, связанных с задержкой конвейера, имеются также ограничения, возникающие в результате несбалансированности задержки на каждой его ступени и из-за накладных расходов на конвейеризацию. Частота синхронизации не может быть выше, а, следовательно, такт синхронизации не может быть меньше, чем время, необходимое для работы наиболее медленной ступени конвейера. Накладные расходы на организацию конвейера возникают из-за задержки сигналов в конвейерных регистрах (защелках) и из-за перекосов сигналов синхронизации. Конвейерные регистры к длительности такта добавляют время установки и задержку распространения сигналов. В предельном случае длительность такта можно уменьшить до суммы накладных расходов и перекоса сигналов синхронизации, однако при этом в такте не останется времени для выполнения полезной работы по преобразованию информации. При реализации конвейерной обработки возникают ситуации, которые препятствуют выполнению очередной команды из потока команд в предназначенном для нее такте. Такие ситуации называются конфликтами. Конфликты снижают реальную производительность конвейера Существуют три класса конфликтов: 1. Структурные конфликты, которые возникают из-за конфликтов по ресурсам, когда аппаратные средства не могут поддерживать все возможные комбинации команд в режиме одновременного выполнения с совмещением. 2. Конфликты по данным, возникающие в случае, когда выполнение одной команды зависит от результата выполнения предыдущей команды. 3. Конфликты по управлению, которые возникают при конвейеризации команд переходов и других команд, которые изменяют значение счетчика команд. Конфликты в конвейере приводят к необходимости приостановки выполнения команд (pipeline stall). Обычно в простейших конвейерах, если приостанавливается какая-либо команда, то все следующие за ней команды также приостанавливаются. Команды, предшествующие приостановленной, могут продолжать выполняться, но во время приостановки не выбирается ни одна новая команда. Расслоение памяти. Другой способ повышения пропускной способности оперативной памяти связан с построением памяти, состоящей на физическом уровне из нескольких модулей (банков) с автономными схемами адресации, записи и чтения. При этом на логическом уровне управления памятью организуются последовательные обращения к различным физическим модулям. Обращения к различным модулям могут перекрываться, и т.о. образуется своеобразный конвейер. Эта процедура носит название расслоения памяти. Целью данного метода является увеличение скорости доступа к памяти посредством совмещения фаз обращений ко многим модулям памяти. Существуют несколько вариантов организации расслоения. Наиболее часто используемый способ – расслоение обращений за счет расслоения адресов. Этот способ основывается на свойстве локальности программ и данных, предполагающем, что адрес следующей команды на 1 больше адреса предыдущей (иными словами, линейность программы нарушается только командами перехода). Аналогичная последовательность адресов генерируется процессором при чтении слов данных. Т.о., типичный случай распределения адресов – последовательность вида а, а+1, а+2, а+3 и т.д. (для слов данных – увеличение на 1 – условно, на самом деле 1 – число байт в машинном слове). Из этого следует, что расслоение обращений возможно, если ячейки с адресами а, а+1, а+2, а+3 и т.д будут размещаться в блоках 0,1,2… Такое распределение ячеек по модулям (банкам) обеспечивается за счет использования адресов вида (см. рис. 2). Здесь В – k–разрядный адрес модуля (младшая часть m–разрядного адреса), С – n–разрядный адрес ячейки в модуле В (старшая часть адреса).  Рис. 2. Формат адреса при организации расслоении обращений к памяти за счет расслоения адресов. Принцип расслоения адресов иллюстрирован на рис 3. (а). |