мдк 03.01 Бистабильные схемы и триггеры. Бистабильные схемы и триггеры

Скачать 90.57 Kb. Скачать 90.57 Kb.

|

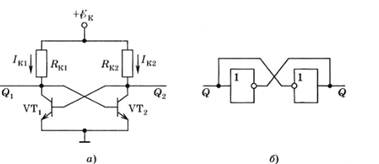

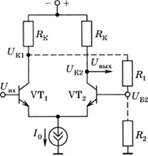

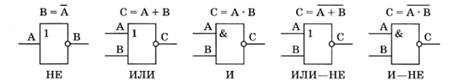

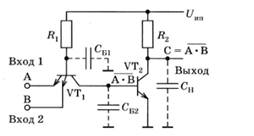

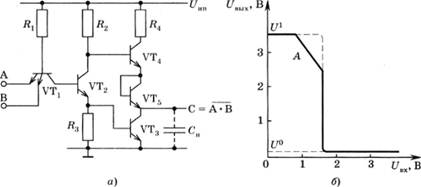

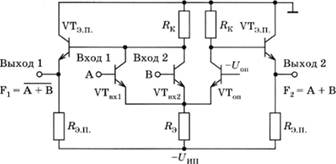

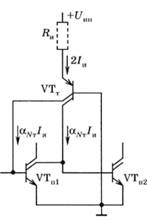

0,03...0,05 пДж в режиме малых токов инжектора. Элементы И2Л отличаются от других элементов на биполярных транзисторах малой потребляемой мощностью и малой занимаемой площадью на кристалле при большой средней задержке и плохой помехоустойчивости.Бистабильные схемы и триггеры Бистабильные схемы и триггеры строятся на основе цепочек ключей, у которых присутствуют не только прямые связи между ключами, но и положительные обратные связи. В качестве элемента памяти наиболее часто используются бистабильные ячейки, которые имеют два устойчивых состояния, соответствующих логическому 0 или логической 1. Если в последовательной цепочке ключей выделить пару соседних ключей, изолировав рассматриваемую пару от предыдущих и последующих звеньев цепочки и соединив выход последующего (второго) ключа (?2 со входом предыдущего (первого) и, наоборот, выход первого со входом второго (рис. 9.9, а), мы получим схему, которая называется бистабильной ячейкой (БЯ) (условное обозначение БЯ дано на рис. 9.9, б). Бистабильная ячейка вместе с цепью управления составляют схему любого триггера. Хотя схеме бистабильной ячейки соответствует симметричная конфигурация, электрически она является асимметричной, поскольку один из ключей заперт, а второй открыт и насыщен. Цель управления бистабильной ячейкой состоит в том, чтобы с помощью внешних сигналов задавать то или иное из двух устойчивых состояний.  Рис. 9.9 Процессы переключения, т. е. переход транзистора из одного в другое состояние, рассмотрим на примере одной из распространенных схем триггера — триггера Шмитта (рис. 9.10). В основе триггера Шмитта лежит схема переключателя тока, рассмотренная ранее в п. 9.2, в которую включен делитель напряжения (Яр #2). Предположим, что в исходном состоянии транзистор УТ1 заперт, т. е. иК1 = £к, а УТ2 находится в активном режиме, т. е. иК2 = £К- /0Дк >иБ2 = - £кЯ2/(#1 + #2). Пусть в какой-то момент входной сигнал С/вх превышает напряжение отпирания на некоторую малую величину, тогда появляется некое малое приращение тока Д/К1, которое вызывает следующие приращения потенциалов: Д£/К1 = —Д/К1НК, ДС/Б2 = Я2 Д?7К1/(Л1 + /?2), = ^^Б2* Изменение ДС/Э приведет к дополнительному приращению коллекторного тока первого транзистора Д/вд > Д/К1, т. е. в схеме развивается лавинообразный процесс, в результате которого ток /0 переходит в транзистор УТ1 и он открывается, а УТ2 — закрывается. Входное напряжение £/вх, которое вызывает скачкообразное переключение УТ1 и УТ2 называют напряжением (порогом) срабатывания триггера. Чтобы вернуть триггер в исходное состояние, нужно уменьшить входной потенциал до значения, близкого к первоначальному значению (УБ2, при котором начинает отпираться УТ2. Входное напряжение С7ВХ, при котором происходит скачкообразное переключение тока из УТ^ в УТ2, называется напряжением (порогом) отпускания триггера. Анализ показывает, что напряжение отпускания меньше напряжения срабатывания. Выходной сигнал в рассматриваемом триггере снимается с коллектора УТ2, который не охвачен обратной связью. Кроме того, УТ2 работает в активном (ненасыщенном) режиме. В результате длительность переходных процессов из-за практического от-  Рис. 9.10 сутствия накопления и рассасывания носителей существенно меньше, чем у бистабильной ячейки, где транзисторы работают в режиме насыщения. Логические элементы на биполярных транзисторах Электронные схемы, выполняющие простейшие логические операции, называются логическими элементами (ЛЭ). Логические элементы используются в большинстве цифровых микросхем и во многом определяют их параметры. Логические функции представляют собой операции над логическими переменными (величинами) А, В, С и т. д. Логические переменные характеризуются двумя взаимоисключающимися значениями: включено и выключено, истинно и ложно, есть и нет и т. д. Для операций с такими логическими величинами используется двоичный код, в котором величина А = 1, а А = 0 (через А обозначено "не А"), т. е. каждая логическая переменная принимает только одно значение: 1 или О. Все логические функции с любым числом логических переменных можно получить с помощью трех основных операций: 1) логического отрицания (инверсии, т. е. операции НЕ), которое записывается в виде В = А; 2) логического сложения (дизъюнкции, т. е. операции ИЛИ), которое записывается для двух переменных в форме С = А 4- В, причем С = 1 при А = 1 или В = 1, или же при А = В = 1; 3) логического умножения (конъюнкции, т. е. операции И), которая для двух переменных представляется как С = - А • В, т. е. С = 1, когда А = В = 1. Комбинация логических операций НЕ и ИЛИ дает более сложную функцию ИЛИ—НЕ, записываемую как С = А + В. Здесь значения С, противоположны ее значениям для операции ИЛИ. Сочетание операций НЕ и И образует функцию И—НЕ и записывается как С = А • В. Схемные ЛЭ реализуют обычно одну или несколько функций: НЕ, И, ИЛИ, И—НЕ, ИЛИ—НЕ, условные обозначения которых представлены на рис. 9.11. Соединяя соответствующим образом эти схемные ЛЭ, построенные в основном на рассматриваемых выше ключах (инверторах), можно получить микросхему, выполняющую любую более сложную  Рис. 9.11 операцию. В ЛЭ логические 0 и 1 представляются напряжением или уровнем нуля и0 и напряжением или уровнем единицы и1. Разность уровней единицы и нуля называют логическим перепадом ил - и1 - и0. ЛЭ подразделяются по режиму работы на статические и динамические. Статические ЛЭ могут работать в статическом и импульсном режимах, а динамические ЛЭ работают только в импульсном режиме. Статические ЛЭ наиболее широко используются в современных ИС. Наибольшее распространение получили ЛЭ на биполярных и МДП-транзисторах. Схемные элементы интегральных логических элементов называют транзисторными логиками. Наиболее распространенными транзисторными логиками на биполярных транзисторах являются: транзисторно-транзисторная логика, эмиттерно-связанная логика, интегральная инжекционная логика. Отличительным признаком ЛЭ транзисторно-транзисторной логики (ТТЛ) является многоэмиттерный транзистор (МЭТ) (см. гл. 7) УТР включенный во входную цепь ЛЭ (рис. 9.12). В базовой цепи УТ1 включен резистор и выходной инвертор (ключ) на УТ2 с резистором /?2 в коллекторной цепи. Простейший элемент ТТЛ, приведенный на рис. 9.12, выполняет логическую функцию И—НЕ (С = А • В), при этом МЭТ УТ, выполняет логическую операцию И над переменными А и В. Такие элементы используются в больших интегральных схемах (БИС). Однако схема, приведенная на рис. 9.12, не нашла широкого применения вследствие низкой помехоустойчивости, малой нагрузочной способности, низкого быстродействия при работе на емкостную нагрузку и жестких требований к параметрам элементов.  Рис. 9.12  Рис. 9.13 Базовым элементом для микросхем малой и средней интеграции, а также в выходных каскадах БИС стал элемент со сложным инвертором (рис. 9.13, а). Этот элемент, как и предыдущий, реализует логическую функцию И—НЕ. Здесь УТ1 и Я выполняют ту же роль, что и в схеме на рис. 9.12. Остальная часть схемы представляет собой сложный инвертор, где УТ2 и Я2> Я3 — промежуточный каскад, а УТ3, УТ4, УТ5 и резистор #4 — выходной каскад. Транзистор УТ5 используется в диодном включении (иБК = 0). С коллектора и эмиттера УТ2 на базы УТ4 и УТ3 подаются управляющие сигналы, которые обеспечивают противофазное переключение этих транзисторов, т. е. если один из них включен, то другой выключен. Рассмотрим процессы в этой схеме. Предположим, на одном или нескольких входах ивх = и° = 0, т. е. подан логический 0. Тогда соответствующие эмиттеры МЭТ УТ, находятся под нулевым напряжением, их эмиттерные переходы смещены в прямом направлении. Анализ показывает, что в такой схеме коллекторный переход находится в насыщении. При этом ток в коллекторной цепи и напряжение на коллекторе и, следовательно, на базе транзистора УТ2 близки к нулю. Напряжение £/ко при /к = 0 равно £/кэ = = Ф7.1п (1 + 1/Р7) (где Р7 — инверсный коэффициент передачи тока) и обычно не превышает (2...3)фг, поэтому транзистор УТ2 закрыт, УТ3 также закрыт, а УТ4 — открыт, поскольку в его базу втекает ток, задаваемый резистором Я2. Поскольку УТ2 закрыт, то напряжение на выходе соответствует напряжению высокого уровня, которое можно оценить по формуле где 21/^з — падение напряжения на эмиттерных переходах транзисторов УТ4 и УТ5 (величина £/^э обычно порядка 0,45...0,5 В). Через эти переходы протекает выходной ток, который является входным током последующих нагрузочных элементов. При подаче и1 на все входы МТ1 транзистор УТ2 открывается коллекторным током входного транзистора УТ1 и переходит в режим насыщения. Напряжение на его коллекторе понижается и транзистор УТ4 закрывается, а УТ3 открывается эмиттерным током УТ2 и насыщается. Выходное напряжение С/вых = £/° определяется напряжением насыщения УТ3. Назначение транзистора УТ5 заключается в том, чтобы поддерживать закрытое состояние УТ4 при понижении выходного напряжения. Через резистор Д3 протекает базовый ток УТ3 во время процесса рассасывания. Резистор Я4 служит для ограничения импульсного тока УТ4 при переключении из состояния £/нмх = С/° в состояние (7ВЫХ — и1. Нагрузочная способность элемента ТТЛ со сложным инвертором в состоянии (УВЬ1Х = и за счет УТ4 больше примерно в р4 раз по сравнению с простейшим элементом ТТЛ на рис. 9.12. Выходная характеристика элемента ТТЛ со сложным инвертером (рис. 9.13, б сплошная линия) подобна по форме выходным характеристикам обычных инверторов (ключей), но идет выше, поскольку в этом случае £/ВЬ1Х больше из-за более высокого напряжения источника питания (Уип. Однако эта характеристика идет более полого при некоторых значениях С/вх (участок А на рис. 9.13, б). Пологий участок А выходной (передаточной) характеристики можно скорректировать за счет замены резистора Я3 более сложной корректирующей цепью, включающей, помимо резисторов, также и добавочный транзистор. В результате выходная характеристика на рис. 9.13, б примет на участке А форму, соответствующую пунктирной кривой. Логический элемент со сложным инвертором занимает большую площадь на кристалле, чем элемент на рис. 9.12, и потребля-  Рис. 9.14 ет большую мощность, поэтому его применение ограничено цифровыми ИС малой и средней степени интеграции. Для повышения быстродействия элементов ТТЛ в них используют транзисторы с диодом Шоттки или ЛЭ эмиттерно-связанной логики (ЭСЛ), отличительной особенностью которых является использование переключателя тока (см. гл. 8) с транзисторами, работающими в активном режиме, что исключает режим насыщения и связанное с ним рассасывание носителей, уменьшает временную задержку и повышает быстродействие. Простейшими элементами ЭСЛ являются элементы малосигнальной эмитгерно-связанной логики (МЭСЛ) (рис. 9.14), которые используются во внутренних цепях средних интегральных схем (СИС) или БИС. Приведенная схема содержит два входных транзистора УТвх1 и УТвх2 (в действительности их может быть больше) и генератор тока в форме токозадающего резистора Дэ. Эмиттеры всех транзисторов соединены (связаны), что и определяет название логики ЭСЛ. Особенностью применения МЭСЛ является использование отрицательного напряжения питания -С/ип, что ослабляет влияние его изменения на уровни 17° и С/1. В схеме рис. 9.14 на инверторном выходе 1 реализуется логическая функция ИЛИ—НЕ -* = А + В, а на прямом выходе 2 — функция или —■> ¥2 = А + В. Опорное напряжение £/оп, входные и выходные напряжения имеют отрицательную полярность из-за отрицательной полярности напряжения источника питания £/ип. При С/вх = и0 < —иоп транзисторы УТвх1 и УТвх2 закрыты, а УТоп — открыт. Напряжение на инверсном выходе 1 равно и1 и определяется падением напряжения на резисторе в коллекторной цепи опорного транзистора при протекании выходного тока /„ых в нагрузке, т. е. и1 = -/'ЫХДК = л/0Лк/(Р + 1) (Р — ко- эффициент передачи тока последнего ЛЭ). Это напряжение снижается с ростом числа нагрузок (д), что ограничивает нагрузочную способность этого элемента ЭСЛ в состоянии (/вых = Vх. В коллекторной цени открытого опорного транзистора УТоп про- текает ток /к " /э = -(С/ип - £/оп - С/£э)/Яэ, следовательно, напряжение на прямом выходе 2 равно Если £/вх — I/1, то соответствующие входные транзисторы, куда подано это напряжение, открываются, а УТоп закрывается, тогда Из (9.6) видно, что напряжение низкого уровня £/£Ь|х1 (логический 0) на инверсном выходе уменьшается при росте входного напряжения из-за роста тока /э, при этом на прямом выходе Логический перепад ил для МЭСЛ составляет всего 0,3...0,5 В. Из-за такого малого логического перепада элементы МЭСЛ имеют сравнительно низкую помехоустойчивость. Потребляемая мощность практически одинакова для обоих состояний ЛЭ, поскольку ток /э мало изменяется при переключении. Для повышения быстродействия элементов МЭСЛ необходимо уменьшать емкости р—л переходов, паразитные емкости проводников, сопротивление базы, ограничивать число нагрузок и увеличивать граничную частоту транзисторов. В случае повышенной емкости нагрузки (Сн >10 пФ) и большом числе нагрузок (> 10) в быстродействующих ИС применяют более сложные элементы ЭСЛ (рис. 9.15). Схема на рис. 9.15 по сравнению с рассмотренной ранее содержит дополнительно  Рис. 9.15 два выходных эмиттерных повторителя УТЭ п с резисторами Яд п. Принцип работы этой схемы такой же, как и ранее рассмотренной, однако их основные свойства могут сильно различаться. Из-за большего напряжения питания элементы этой ЭСЛ по сравнению с рассмотренными в МЭСЛ имеют больший логический перепад, лучшие помехоустойчивость и нагрузочную способность, большие допустимую емкость нагрузки, потребляемую мощность и занимаемую на кристалле площадь. Элементы ЭСЛ с эмиттерными повторителями применяются в сверхбыстродействующих цифровых микросхемах малой и средней степеней интеграции. Многих из перечисленных недостатков лишены логические элементы, построенные на основе интегральной инжекционной логики (И2Л)У которые не имеют аналогов в дискретных транзисторных схемах и выполняются только в интегральном исполнении. Характерной особенностью схем И2Л является индивидуальное питание базы каждого транзистора от индивидуального генератора тока. В конструкциях БИС с инжекционным питанием используются сложные биполярные структуры, в которых совмещаются области многоколлекторных транзисторов типов п—р—п и р—п—р (см. гл. 7). В силу такого совмещения и переплетения большого количества элементов ИС для ЛЭ И2Л не существуют (не используются) принципиальные электрические схемы. Как правило, их работа описывается с помощью эквивалентных схем. Индивидуальные генераторы тока реализуются чаще всего с помощью МКТ, включенных по схеме с ОБ. На рис. 9.16 изображена эквивалентная схема двух последовательно включенных ЛЭ [6], где VTT двухколлекторный токозадающий транзистор р—п—р, подсоединенный через токозадающий резистор RH к цепи питания, являющейся общей для всего кристалла БИС. Токозадающий транзистор обычно является многоколлекторным с числом коллекторов л, доходящим до нескольких сотен. Транзистор VTT задает постоянные токи оСд^л в базы п—р—л-транзисторов VTnl и VTn2, где /и — ток инжектора, приходящийся на один логический эле-  Рис. 9.16 мент. Транзисторы УТп1 и УТп2 называются переключательными и включены по схеме с ОЭ, а токозадающий УТт — по схеме с ОБ. Термин "инспекционное питание" означает, что питающие токи образуются за счет инжекции неравновесных дырок в эмиттерную область инжектора через инжекторный р—л-переход, напряжение на котором составляет 0,7...0,8 В (при Т° = 25 °С); токи питания /п одинаковы и равны Если на вход УТп1 подано напряжение £/„х1 = и0 |