Битва за кавказскую нефть. ЭВМ ОТВЕТЫ НА ВОПРОСЫ. Эвм ответы на вопросы

Скачать 1.4 Mb. Скачать 1.4 Mb.

|

|

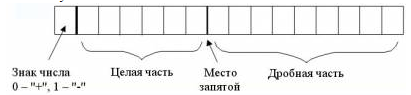

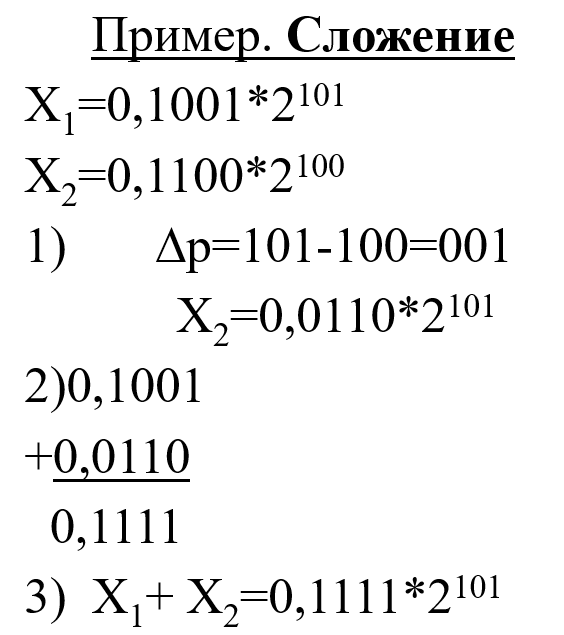

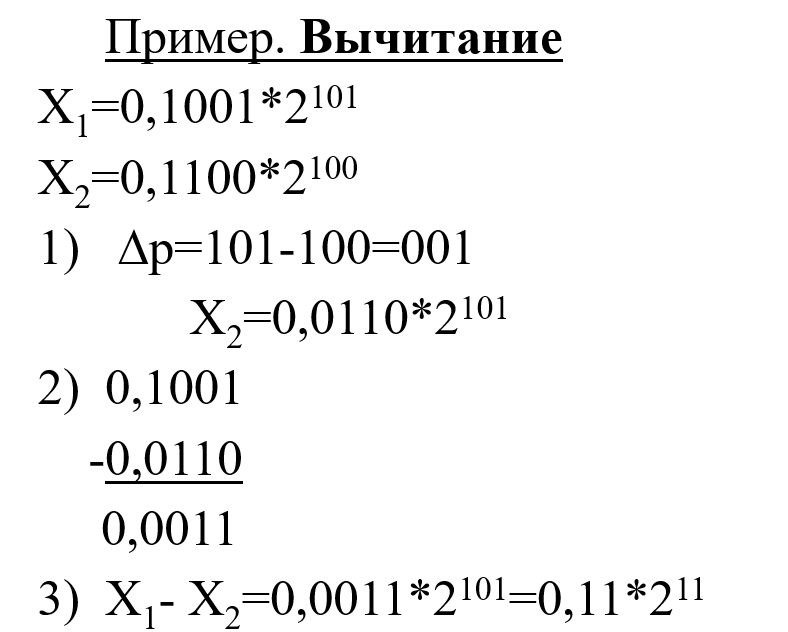

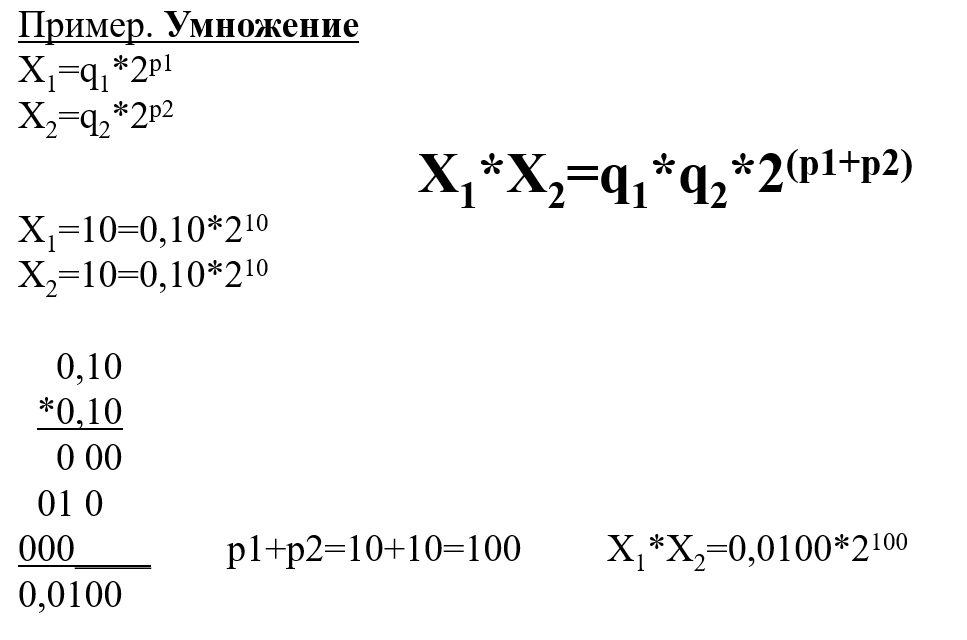

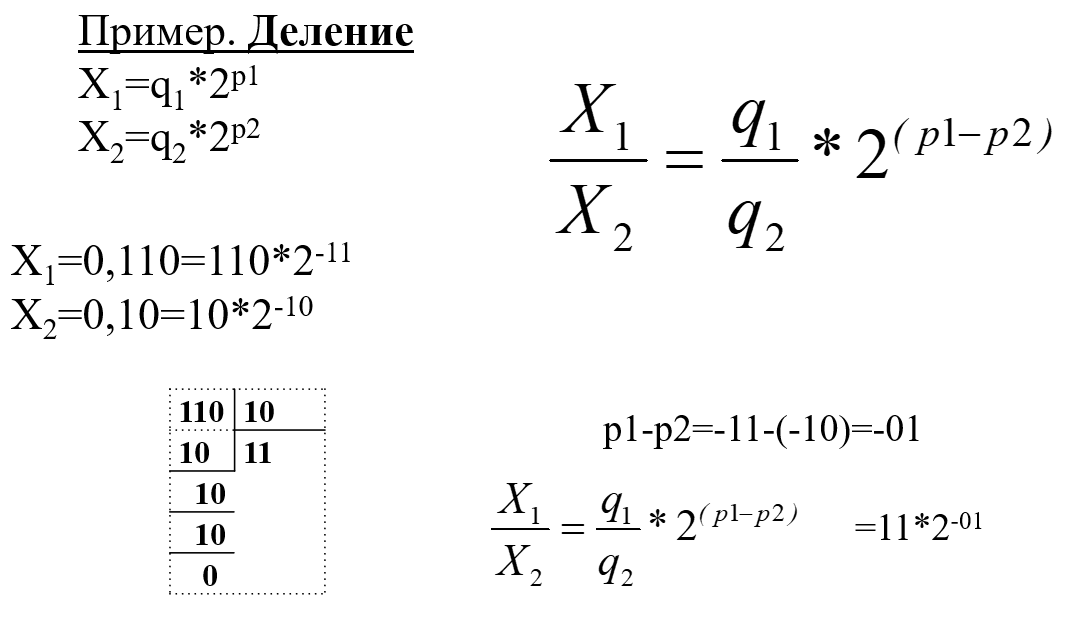

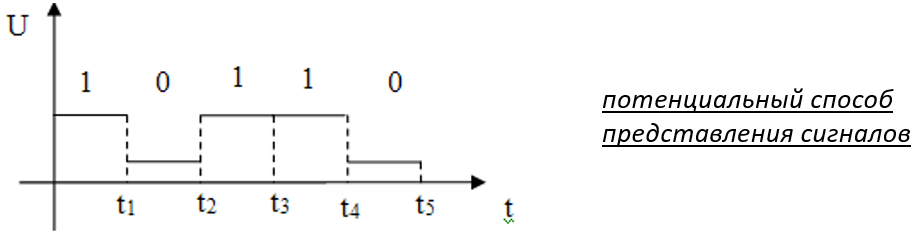

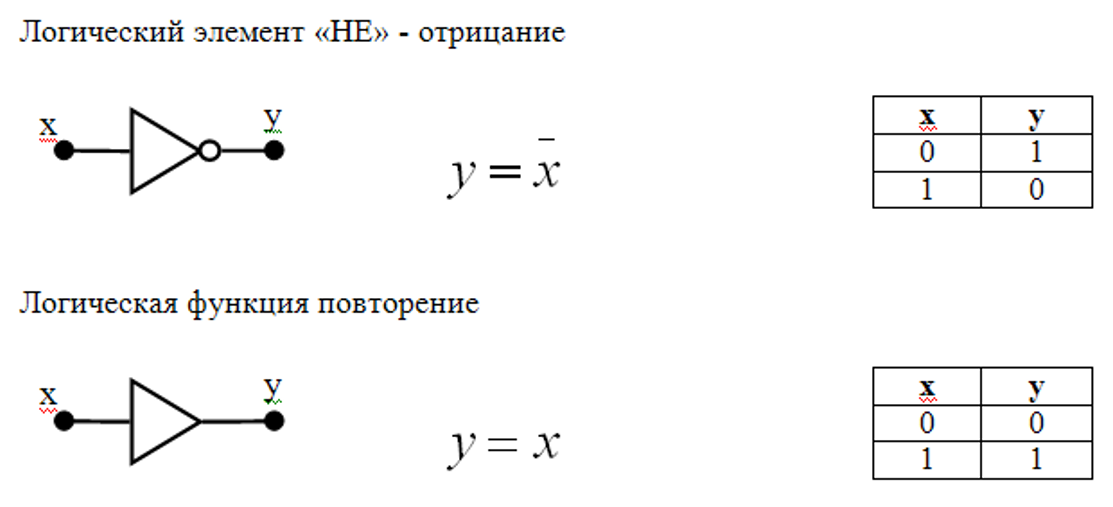

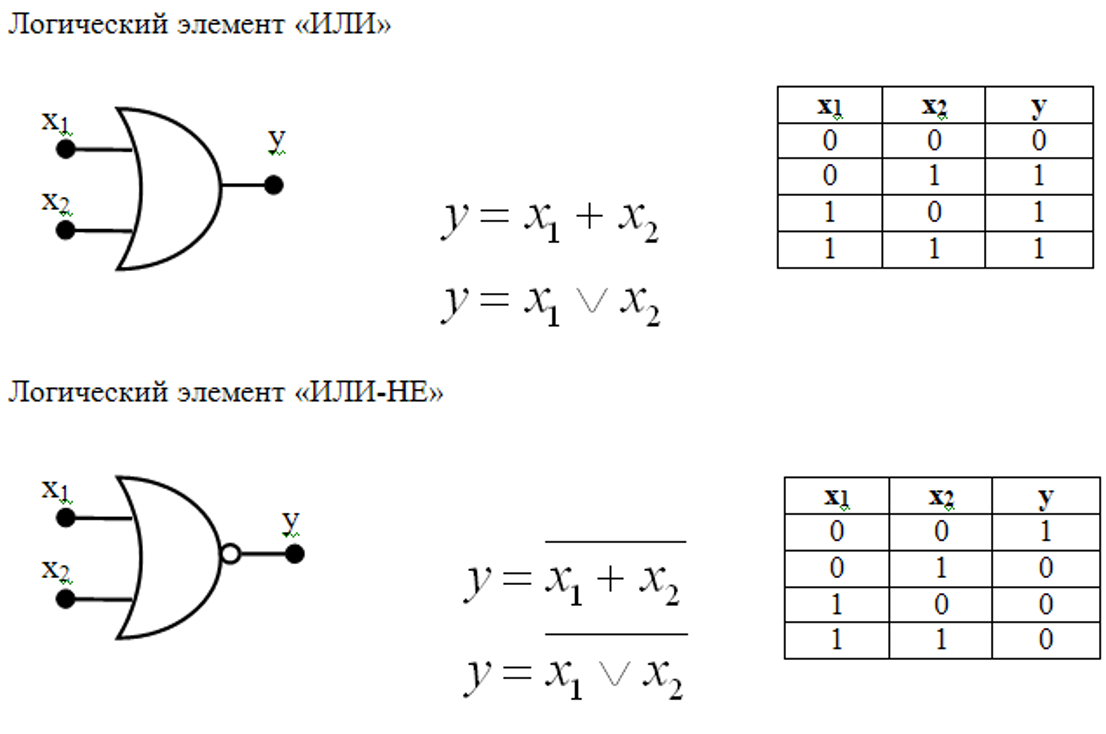

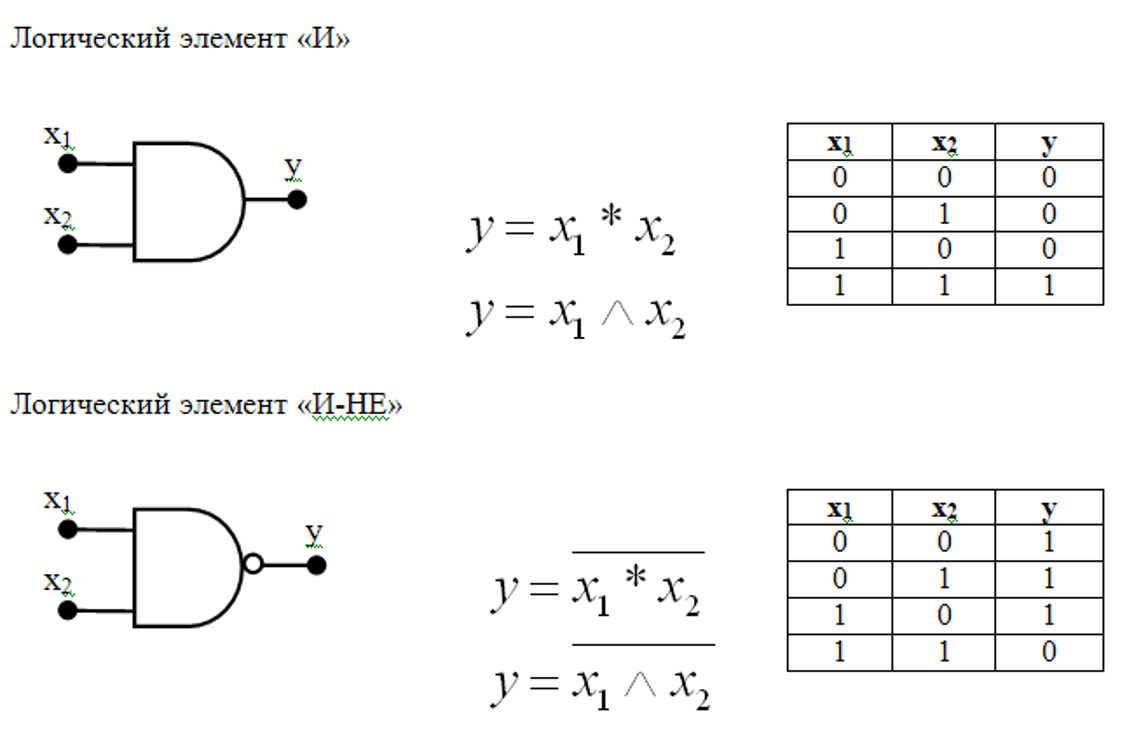

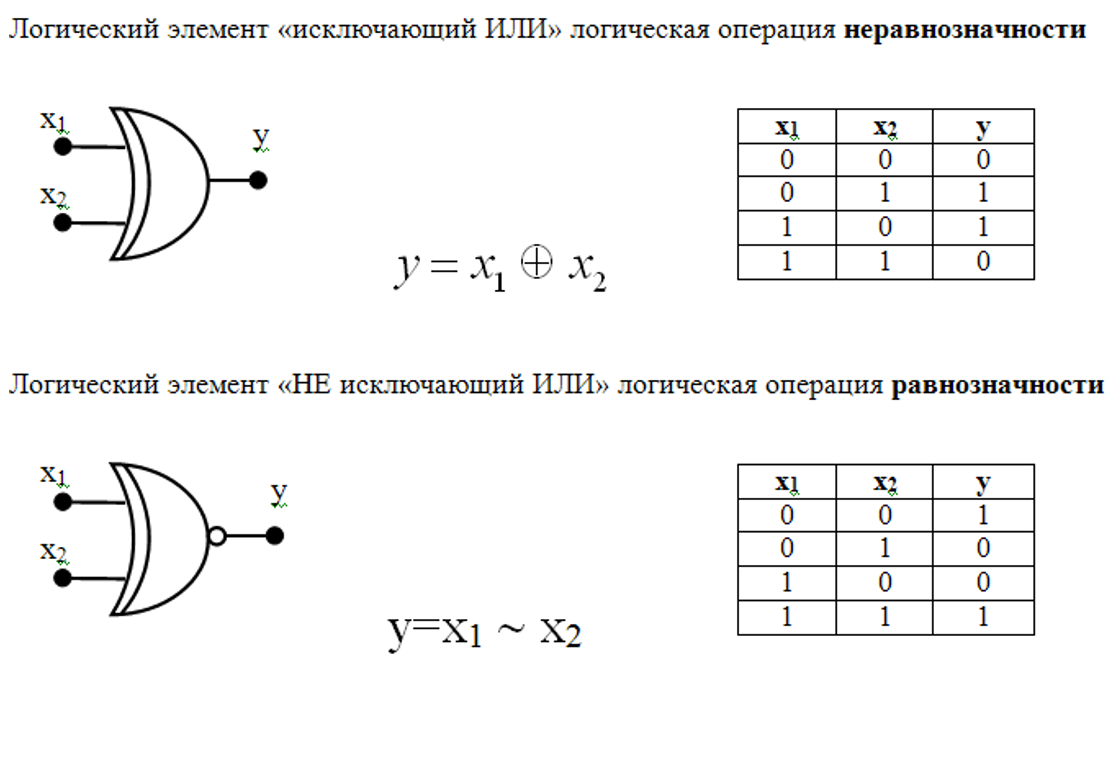

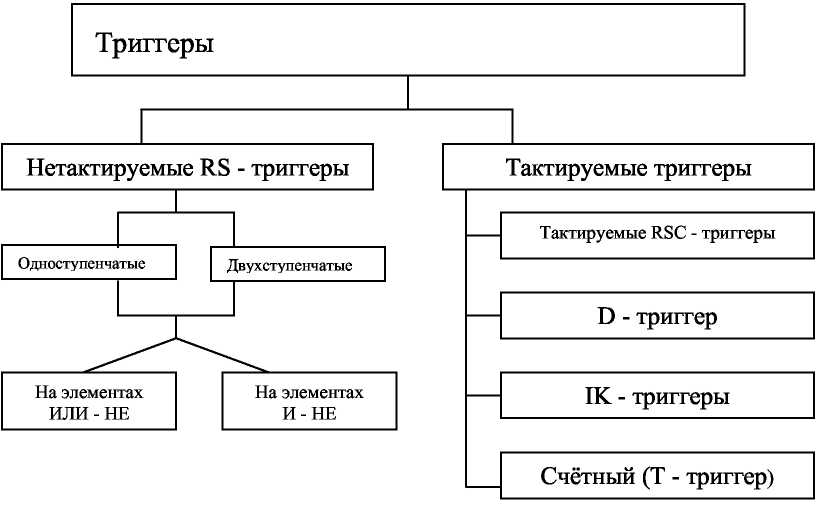

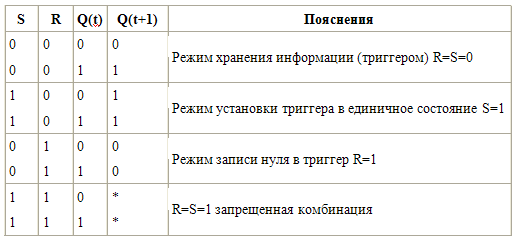

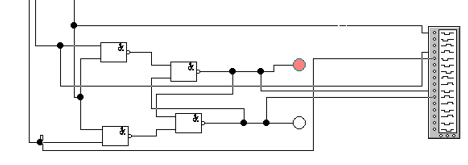

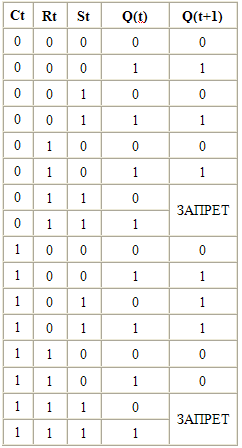

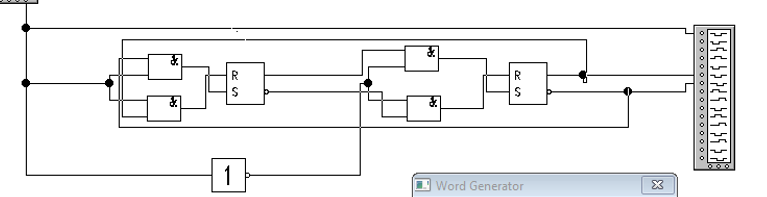

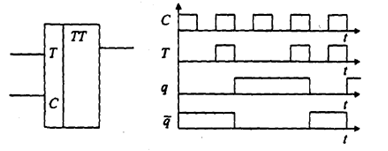

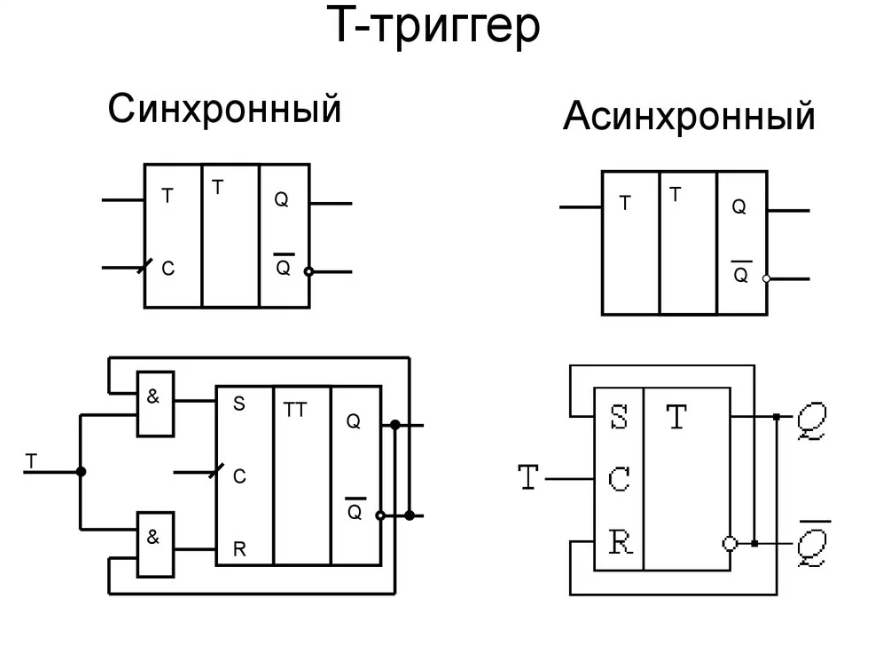

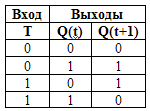

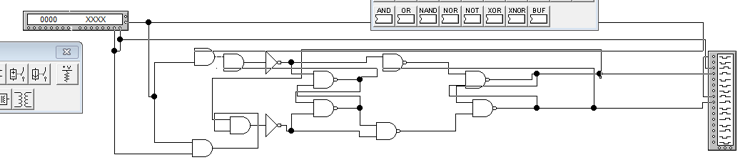

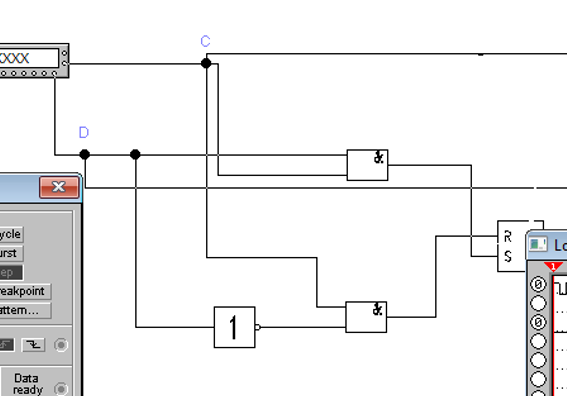

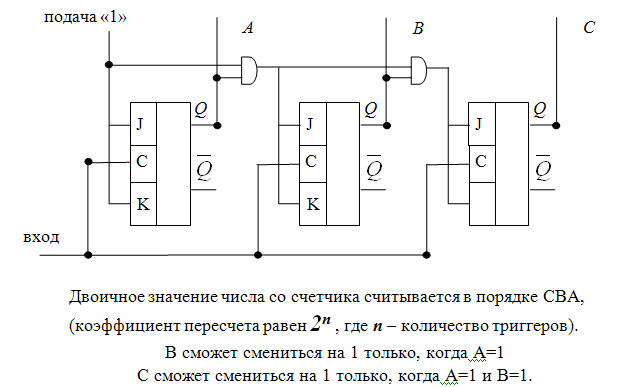

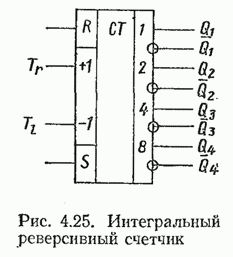

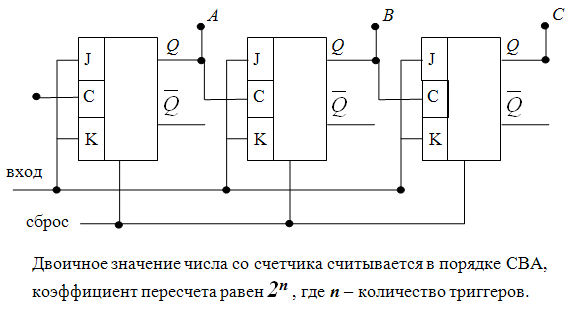

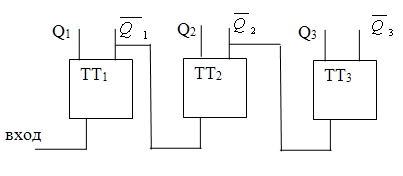

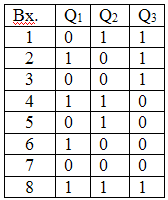

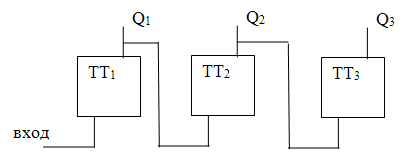

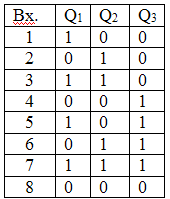

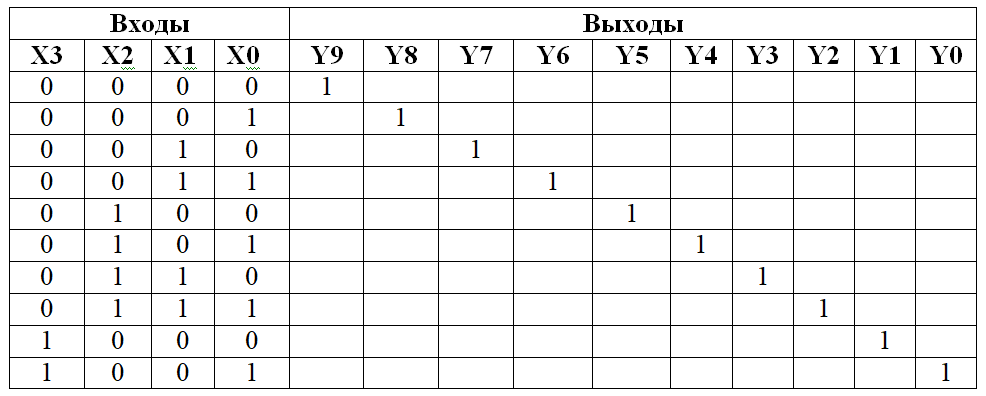

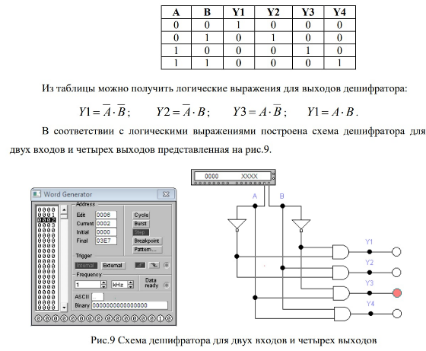

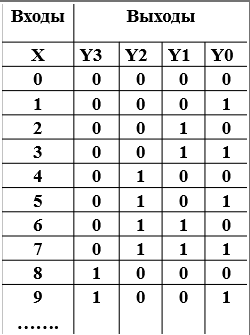

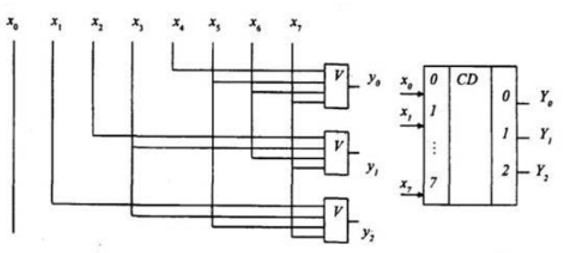

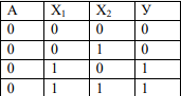

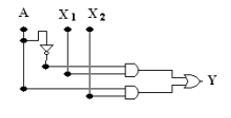

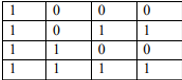

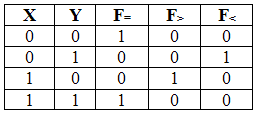

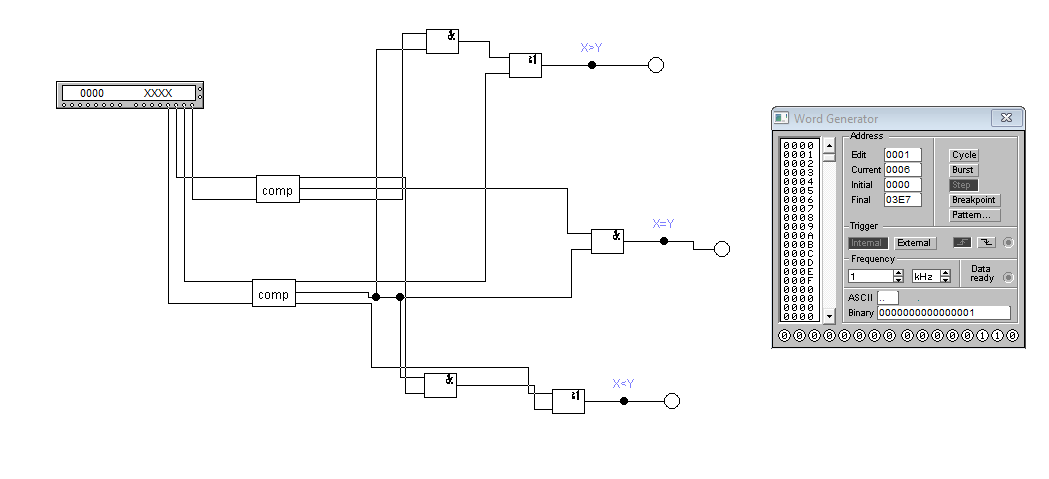

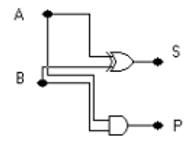

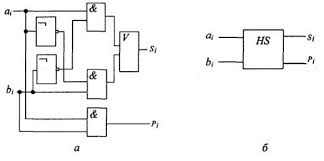

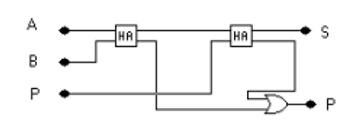

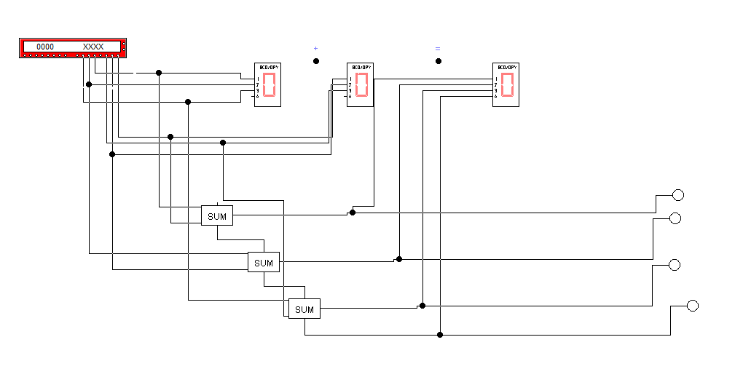

ЭВМ ОТВЕТЫ НА ВОПРОСЫ Система счисления это способ представления чисел с помощью некоторого алфавита символов, называемых цифрами и имеющими определенные количественные значения. Разряд - это положение цифры в числе Основание системы счисления – это количество цифр, необходимых для записи числа в системе. Основание системы записывается справа числа в нижнем индексе. позиционные (123, 453, 50) Непозиционные (CCXXXII=232, IX =9) Формы представления чисел в ЭВМ: - с фиксированной точкой (запятой) – естественная форма числа; с плавающей точкой (запятой) – нормализованная форма числа. У чисел с фиксированной точкой в двоичном формате предполагается строго определенное место точки (запятой).   Мантисса – Мантисса (лат. mantissa прибавка) мантисса дробная часть логарифма числа; значащая часть числа в формате с плавающей запятой. Порядок числа – это степень, в которую возводится основание системы счисления, в которой записано число.     О  Передавать многоразрядный двоичный код в ЭВМ можно последовательно, параллельно и смешанно. ТИПЫ СИНХРОНИЗАЦИИ ДАННЫХ: Синхронизация данных - согласование различных процессов во времени. Асинхронный способ характеризуется тем, что сигналы передаются с произвольными промежутками времени. Синхронный способ характеризуется тем, что сигналы передаются строго периодично во времени. Смешанный способ характеризуется тем, что байты передаются асинхронно, а биты внутри байтов синхронно.     Триггер — класс электронных устройств, обладающих способностью длительно находиться в одном из двух устойчивых состояний и чередовать их под воздействием внешних сигналов. Каждое состояние триггера легко распознаётся по значению выходного напряжения. По характеру действия триггеры относятся к импульсным устройствам — их активные элементы (транзисторы, лампы) работают в ключевом режиме, а смена состояний длится очень короткое время. Отличительной особенностью триггера как функционального устройства является свойство запоминания двоичной информации. Под памятью триггера подразумевают способность оставаться в одном из двух состояний и после прекращения действия переключающего сигнала. Приняв одно из состояний за «1», а другое за «0», можно считать, что триггер хранит (помнит) один разряд числа, записанного в двоичном коде.  Асинхронный RS-триггер оснащён двумя входами – R и S, и двумя выходами – прямым и инверсным. Если на вход S подать значение 1, то пойдет запись информации, то есть Q=1, Q’=0, затем при следующей подаче на вход S значения 0, при R=0, ничего не произойдет. Подача на вход R значения 1 вызывает сброс информации, то есть Q=0, Q’=1, при следующей подаче на вход R значения 0, при S=0, ничего не произойдет. Комбинация S=1, R=1 для асинхронного RS-триггера запрещена.   Однотактный синхронный RS-триггер на каждом информационном входе имеет дополнительные схемы совпадения, первые входы которых объединены. На них подаются синхронизирующие сигналы. Вторые входы схем совпадения являются информационными. Наличие схем совпадения приводит к тому, что триггер будет срабатывать от сигналов R и S только при наличии синхросигнала. Если синхросигнал отсутствует, триггер работает в режиме хранения информации.   Т-триггер считает количество поданных на него сигналов. Триггер имеет один вход – T – и переходит в противоположное состояние в результате воздействия на его вход последующего сигнала. При входном сигнале T=0 триггер устанавливает на выходах T-2 и T-1 равные состояния, а при T=1 – разные.     JK-триггер сочетает в себе два триггера - RS-триггер при комбинациях входных сигналов 0-1, 1-0, 0-0 и счётный триггер при комбинации 1-1. Таким образом, JK-триггер – более совершенная версия RS-триггера, так как он не имеет запрещённых сигналов.  D-триггер имеет два входа – D (информационный) и C (синхросигнал). При состоянии С=0 триггер устойчив, сигнал на его выходе не зависит от сигналов, поступающих на вход D, и показывает его предыдущее «защелкнутое/сохраненное» состояние. При С=1 на прямом выходе информация будет точно повторять ту информацию, которая подается на вход D.  Регистр — последовательное или параллельное логическое устройство (узел), используемое для хранения n-разрядных двоичных чисел и выполнения преобразований над ними. Регистры применяются так же для: - для сдвига кода числа (слова) на определенное число разрядов влево или вправо, - для преобразования последовательного кода числа в параллельный и наоборот. Регистры представляют собой совокупность триггеров, число которых соответствует числу разрядов в слове, и вспомогательных схем, обеспечивающих выполнение различных операций над словом по способу ввода/вывода информации: параллельные (регистры хранения) – информация вводится и выводится одновременно по всем разрядам; последовательные (регистры сдвига) – информация бит за битом «проталкивается» через регистр и выводится также последовательно; комбинированные – параллельный ввод и последовательный вывод (и наоборот). по способу представления информации: однофазные – информация представляется в прямом или обратном (инверсном) виде; парафазные – информация представляется и в прямом, и в обратном виде. по способу тактирования регистры подразделяют на: однотактные, управляемые одной управляющей последовательностью импульсов; многотактные, управляемые несколькими управляющими последовательностями импульсов. Двоичный синхронный счётчик  Синхронный счётчик позволяет вести подсчёт в двоичной системе счисления. От асинхронного синхронный счётчик отличается тем, что за счёт использования схем совпадений достигается одновременное переключение всех триггеров. Реверсивный счетчик – предназначен для организации поочередного сложения и вычитания поступивших импульсов. Реверсивные счетчики имеют два управляющих входа «+1» и «-1» и при подаче импульса на соответствующих управляющий вход, код, записанный в счетчике, либо увеличивается, либо уменьшается на 1.  Двоичный асинхронный счётчик  Схема асинхронного двоичного счётчика состоит из четырёх последовательно подключенных Т-триггеров, выполненных на основе универсальных JK-триггеров. За старший разряд отвечает последний JK-триггер, а за младший – первый, поэтому значение в счётчике считается справа налево. Вычитающий счетчик – предназначен для организации обратного отсчета импульсов (предварительно все триггеры в единичном состоянии)   Суммирующий счетчик – предназначен для суммирования входных импульсов (предварительно все триггеры в нулевом состоянии)   Дешифратором, или декодером называется комбинационное логическое устройство для преобразования чисел из двоичной системы счисления в десятичную. Если число адресных входов дешифратораnсвязана с числом его выходовmсоотношениемm=2n, то дешифратор называютполным. В противном случае, т.е. еслиm<2n, дешифратор называютнеполным.   Шифратор (кодер) преобразует единичный сигнал на одном из входов в n-разрядный двоичный код. Наибольшее применение он находит в устройствах ввода информации (пультах управления) для преобразования десятичных чисел и команд в двоичную систему счисления. Число входов и выходов в полном шифраторе связано соотношением n= 2m, где n— число входов, m— число выходов.   Mультипле́ксор — устройство, имеющее несколько сигнальных входов, один или более управляющих входов и один выход. Мультиплексор позволяет передавать сигнал с одного из входов на выход; при этом выбор желаемого входа осуществляется подачей соответствующей комбинации управляющих сигналов. Связан зависимостью n = 2k – полный, если n < 2k – неполный.    компаратором называется комбинационное логическое устройство, предназначенное для сравнения чисел, представленных в виде двоичных кодов. Число входов компаратора определяется разрядностью сравниваемых кодов. ОДНОРАЗРЯДНЫЙ КОМПАРАТОР:   ДВУРАЗРЯДНЫЙ КОМПАРАТОР:  Сумматор - логический операционный узел, выполняющий арифметическое сложение кодов двух чисел. Разделяют на полусумматор и полный сумматор. Полусумматор – предназначен для сложения одноразрядных двоичных чисел без учета переноса из предыдущего разряда.    Полный сумматор – предназначен для сложения одноразрядных двоичных чисел с учетом переноса из предыдущего разряда.   Параллельный n разрядный сумматор предназначен для суммирования n разрядных чисел. На основе одноразрядных строят многоразрядные сумматоры. Наибольшее распространение получили сумматоры параллельного действия. В параллельном сумматоре все разряды чисел обоих слагаемых одновременно подаются на входы одноразрядных сумматоров, в которых образуются разрядные суммы и переносы. В данной схеме бит переноса из старшего разряда сумматора становится старшим разрядом суммы. Его схема составляется из n полных сумматоров, соединенных между собой  |