5fan_ru_Изучение команд пересылки данных МК МС 68HC908GP32. Изучение команд пересылки данных мк мс 68HC908GP32

Скачать 1.63 Mb. Скачать 1.63 Mb.

|

|

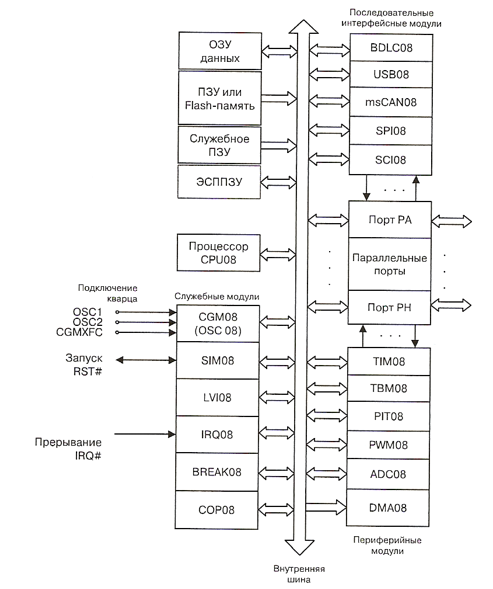

Дисциплина: « Микропроцессоры и микропроцессорные системы» Практическая работа № 4 Тема: «Изучение команд пересылки данных МК МС 68HC908GP32». Цель: Практически изучить команды пересылки данных МК МС 68HC908GP32 Время: 2 часа Оборудование: ПК, ПО. Методические материалы и литература: Методические указания по выполнению практических работ; Иллюстративный материал: «команды управления на языке ASM для МП». Методические указания по выполнению практической работы: Последовательность выполнения работы: Изучить основные теоретические положения по теме, используя описание работы; Выполнить практическую часть лабораторной работы. При этом использовать описание работы, лабораторный блок ПК, иллюстрационный материал; В практической части отработать следующие подразделы: Рассмотреть и изучить способы адресации и системы команд Выполнить: материал практической части, исполнить рис.1, 2,3 Проанализировать полученные результаты Ответить на контрольные вопросы. Сделать выводы. Подготовить отчёт по установленной форме. Представить отчёт для защиты преподавателю. 1. Основные теоретические положения Семейство 8-разрядных микроконтроллеров 68НС08/908 Семейство 8-разрядных микроконтроллеров 68НС08/908 является дальнейшим развитием семейства 68НС05/705. Микроконтроллеры (МК) этого семейства предназначены для замены семейства 68НС05/705 в новых разработках. Сохраняя архитектуру семейства 68НС05/705, МК 68НС08/908 позволяют обеспечить более высокие технико-экономические характеристики устройств, реализуемых на их основе. В составе семейства преобладают модели, содержащие FLASH -памятъ (подсемейство 68НС908), что обеспечивает возможность их широкого использования в изделиях малой серийности. Следует отметить программную совместимость «снизу-вверх» процес-соров семейств 68НС05/705 и 68НС08/908, что позволяет использовать в МК 68НС08/708 программы, ранее созданные для 68НС05/705. Основные преимущества семейства 68НС08/908 по сравнению с МК 68НС05/705: процессор СРU08 работает на более высокой тактовой частоте (8 МГц), реализует ряд дополнительных способов адресации и имеет расширенный набор выполняемых команд. В результате достигается повышение производительности от 4 до 6 раз по сравнению с МК 68НС05; применение FLASH -памяти обеспечивает возможность программирования МК подсемейства 68НС908 непосредственно в составе реализуемой системы с помощью персонального компьютера; модульная структура МК b наличие большой библиотеки интерфейсных и периферийных модулей с улучшенными характеристиками позволяет реализовать различные модели с расширенными функциональными возможностями; существенно расширены возможности отладки программ благодаря введению монитора отладки и реализации останова в контрольной точке. Таким образом, обеспечивается возможность эффективной отладки без применения дорогостоящих схемных эмуляторов. В настоящее время семейство 68НС08/908 является основным промыш-ленным стандартом компании Моtorola в сфере 8-разрядных МК и насчитывает около 40 моделей, рекомендованных для применения. Все МК семейства 68НС08/908 содержат: процессорное ядро СРU 08, внутреннюю память программ — масочно-программируемое ПЗУ емкостью до 32 Кбайт или FLASH -память емкостью до 60 Кбайт, ОЗУ данных емкостью от 128 байт до 2 Кбайт. Используемая в МК FLASH -память допускает выполнение до 10 тыс. циклов стирания-программирования. В ряде моделей имеется также ЕЕРRОМ емкостью 512 байт или 1 Кбайт. Большинство МК семейства работают при напряжении питания 5 В, при максимальной тактовой частоте Ft = 8 МГц. Многие модели работают при пониженном напряжении питания — 3,3; 3,0; 2,0 и 1,8 В, Основной диапазон рабочих температур —40...85°С. Во многие серии (например АВ. АZ, ,JК, JL КХ, QТ, ОY) включены модели, работающие в расширенном температурном диапазоне -40...105oС или —-40...125o C.. МК семейства 68НС08/908 делятся на ряд серий, буквенные символы которых указываются после имени семейства (например, 68НС08А232 — серия АZ модель 32). Серии отличаются, в основном, составом периферийных модулей и областями применения. Все модели содержат 16-разрядные таймеры, имеющие два, четыре или шесть комбинированных входа/выхода захвата/совпадения. Большинство моделей содержит 8-пли 10-разрядные АЦП. В состав серий АВ. АS, АZ . входят МК общего назначения, которые обеспечивают расширенные возможности интерфейса с внешними устройствами благодаря наличию шести параллельных и двух последовательных портов (SСI, SРI). Модели серий ВD, SR и GР имеют четыре параллельных порта. Ряд серий имеет специализированные последовательные порты, используемые для организации микроконтроллерных сетей. Это серия АS , обеспечивающая передачу данных по мультиплексной шине J1850, серия JВ, имеющая интерфейс с последовательной шиной USB, серия АZ , содержащая контроллер сети САN, серия ВD , реализующая интерфейс РС. МК этих серий широко используются в промышленной автоматике, измерительной аппаратуре, системах автомобильной электроники, вычислительной технике. Специализированные МК серии МК содержат 12-разрядные ШИМ-модули с шестью выходными каналами. Они используются в системах управления электроприводом. МК серии MR содержат модуль радиопередающего устройства и ориентированы на применение в системах радиотелефонной связи. Модели серии RК предназначены для использования в устройствах бесконтактной идентификации. Серии JВ, JК,JL, КХ выпускаются в дешевых корпусах, имеющих от 16 до 28 выводов. МК этих серий имеют от 13 до 23 линий параллельного ввода/вывода данных. Они предназначены для использования в бытовой аппаратуре и изделиях массового применения, где невысокая стоимость — один из первостепенных факторов. В сериях QТ, QY представлены модели, ориентированные на применение в малобюджетных проектах. Эти МК отличаются низкой стоимостью и выпускаются в компактных корпусах с малым числом выводов (8 или 16). Они имеют встроенный генератор, обеспечивающий формирование тактовой частоты с точностью 5%. Наличие FLASH -памяти емкостью до 4 Кбайт, 8-разрядного АЦП с четырьмя аналоговыми входами и двухканального 16-разрядного таймера делают эти модели перспективными для построения несложных контроллеров, используемых в распределенных системах мониторинга и управления. Структура и функционирование МК 68НС08/908 МК семейства 68НС08/908 имеют модульную структуру, где каждая модель формируется из библиотеки стандартных модулей, взаимодействующих посредством внутренней шипы. Путем объединения на кристалле процессорного модуля СРU 088, модулей памяти (ОЗУ, масочное ПЗУ, FLASH , ЕЕРRОМ) и ряда служебных, интерфейсных и периферийных модулей реализуются различные модели МК этого семейства На рисунке 1 показана типовая структура МК семейства 68НС08/908.  Рис.1 Общая структура МК семейства 68НС08/908 Процессорный модуль СРU08 является модифицированным вариантом процессора СРU05, используемого в семействе 68НС05/705. Он имеет значительно расширенный набор команд (90 команд вместо 65) и способов адресации (9 вместо 6). При этом СРU08 реализует весь набор команд и способов адресации процессора СРU05, обеспечивая с ним полную программную совместимость. Модуль СРU08 содержит 8-разрядные аккумулятор А и регистр признаков ССR., 16-разрядные индексный регистр Н:Х. указатель стека SР и программ-мный счетчик РС. Регистровая модель СРU08 (см. рис. 2) аналогична модели процессора СРU05, отличаясь от неё увеличенной разрядностью индексного регистра, РС и SР.  Рис.2 Регистровая модель МК семейства 68НС08/908 Расширение их разрядности обеспечивает увеличение объема адресуемой памяти до 64 Кбайт (адреса 0x0000...ОхFFFF). Для совместимости с семейством 68НС05/705 индексный регистр состоит из двух 8-разрядных частей: Н (старший байт) и X (младший байт). Регистр ССR. содержит значения признаков переноса (С), переполнения (V), нуля (Z), отрицательного результата N) и переноса между тетрадами (Н). устанавливаемых по результатам выполнения операции. Также ССR.. содержит бит маскирования прерываний I, при установке которого запрещается обслуживание маскируемых прерываний. При запуске МК (процедура RЕSЕТ) в РС автоматически загружается адрес первой команды выполняемой программы (вектор начального запуска) из двух последних ячеек адресуемой памяти с адресами ОхFFFE, ОхFFFF , а в SР автоматически загружается значение ОхООFF, обеспечивая возможность использования в качестве стека ячеек ОЗУ и регистров, имеющих адреса в диапазоне ОхОООО... ОхООFF . Различные модели МК отличаются распределением памяти и составом адресуемых регистров. Типовая структура карты памяти приведена на рисунке 3.  Рис.3 Типовая структура карты памяти для семейства МК 68НС08/908 Младшие адреса служат для обращения к регистрам периферийных модулей и регистрам конфигурации. Состав и количество этих регистров зависит от состава модулей, используемых в данной модели. В адресном пространстве ОЗУ располагаются ячейки стека, которые адресуются при помощи указателя стека SР. В процессе выполнения программы можно установить любое значение указателя с помощью команды ТХS, которая загружает в SР содержимое индексного регистра Н:Х. уменьшенное на 1. Часть адресного пространства занята ячейками служебного ПЗУ, в котором содержится программа-монитор, реализующая необходимые процедуры при работе МК в режиме отладки, обеспечивая возможность контроля его внутреннего состояния. Это масочно-программируемое ПЗУ, содержимое которого записы-вается в процессе изготовления МК. В старших позициях адресного пространства располагаются векторы начального запуска и прерываний. При переходе к обслуживанию прерываний в стеке автоматически сохраняется содержимое регистров РС, X, А, ССR, которое восстанавливается при возврате из подпрограммы обслуживания по команде RTI. Потребление мощности зависит от напряжения питания, рабочей частоты и состава периферийных модулей в данной модели МК. В старших моделях (серии АS, АZ), содержащих значительное количество периферийных модулей, потребляемая мощность составляет 175 мВт при Еп — 5,0 В и частоте Ft = 8 МГц. Модели для массового применения (серии GP, JK, JL потребляют около 15 мВт при Еп = 3,0 В и частоте Ft = 4 МГц, а модели серий QТ, QY при тех же условиях — 8 мВт. Значительное снижение потребляемой мощности обеспечивается в энергосберегающих режимах. Режим ожидания реализуется после поступления команды WAIT. При этом прекращается работа процессора, но все остальные модули продолжают функционировать. Потребление мощности в этом режиме снижается в несколько раз. Режим останова реализуется после поступления команды SТОР. В этом случае прекращается работа процессора и большинства других модулей МК. Потребляемый ток в режиме останова снижается до единиц микроампер. Возврат из режимов ожидания и останова в рабочий режим происходит по сигналу запуска или запросу прерывания. Реализация режима отладки, который существенно упрощает процесс разработки различных устройств на базе этих МК, является характерной особенностью семейства. 68НС08/908. В режиме отладки МК выполняет команды чтения и записи содержимого любой ячейки адресуемой памяти или регистра, посылаемые персональным компьютером. Эти команды позволяют контролировать и модифицировать текущее состояние МК, производить стирание и запись содержимого внутренней FLASH -памяти и ЕЕРRОМ. Данный режим обеспечивает выполнение основных операций, реализуемых в процессе отладки программ, без использования дорогостоящих схемных эмуляторов. Кроме того, можно выполнить программирование МК, работающего непосредственно в составе системы управления (ISP — In-System Program-ming). При этом запись или модификация рабочей программы производится при помощи персонального компьютера без использования специальных программаторов и не требует отключения МК (демонтажа) от реализованной системы управления. Основные понятия о данных. Сложные структуры данных Процесс разработки программы на ассемблере традиционно осложняется тем, что в этом языке ограничены средства описания данных, привычные для языков программирования высокого уровня средства, которые поддерживает ассемблер для работы с данными. Но это деление весьма условно и не дает представления о том, как реализуется общая концепция понятий: «данное», «тип данных» и «структура данных» в контексте программирования на языке ассемблера. Это обстоятельство существенно влияет на эффективность изучения и использования языка ассемблера. Проблема представления и организации эффективной работы с данными возникла одновременно с идеей разработки первой вычислительной машины. Вычислительная машина функционирует согласно некоторому алгоритму. А если есть алгоритм, то должны быть и данные, с которыми он работает. Что же представляют собой понятия «данное», «тип данного», «структура данных»? Данное — набор байт, рассматриваемый безотносительно к заложенному в них смыслу. Понятие «обработка данных» характерно для процессора как исполнительного устройства. При этом «данное» рассматривается как совокупность двоичных разрядов, которыми манипулирует определенная машинная команда. Для человека подобную интерпретацию вряд ли можно считать удобной. Для него более естественной является логическая интерпретация данных, которая базируется на понятии «типа данных». C точки зрения типа данные были разделены на две группы — простые и сложные. Данными простого типа считаются элементарные, неструктурированные данные, которые могут быть описаны с помощью одной из директив резервирования и инициализации памяти. Примером таких данных являются целые и вещественные числа различной размерности. В языках высокого уровня в качестве простых данных используются еще и данные символьного, логического, указательного типов. Данные простого типа называют упорядоченными (или скалярными), так как теоретически можно перечислить все значения, которые они могут принять. Отличительная особенность данных простого типа — их не структурированность. Между некоторыми простыми данными могут существовать определенные отношения и связи, что позволяет рассматривать их как определенным образом организованные совокупности. Обобщенное название таких совокупностей — структуры данных. Язык ассемблера — язык уровня архитектуры конкретного компьютера. Память компьютеров с архитектурой Intel представляет собой упорядоченный набор непосредственно адресуемых машинных ячеек (байтов). Исходя из этого номенклатура структур хранения данных архитектурно ограничена следующим набором: скаляр, вектор, список, сеть. 2 Практическая часть Рассмотрел и изучил способы адресации и системы команд Способы адресации и системы команд МК работает с операндами, размещенными в регистрах А, X и памяти. Команды имеют длину от 1 до 3 байт: первый байт содержит код операции, второй и третий байты адресуют операнд. Для выборки операнда может использоваться широкий набор способов адресации: регистровая (операнд располагается в регистре А или X); индексная (адресом операнда служит содержимое регистра Н:Х); индексная со смещением (адрес операнда образуется путем сложения содержимого регистра Н:Х и 8- или 16-разрядного смещения); по указателю стека со смещением (адрес операнда образуется путем сложения содержимого регистра SР и 8- или 16-разрядного смещения); прямая (8- или 16-разрядный адрес операнда задается в команде); непосредственная (операнд является вторым байтом команды); относительная (используется только в командах ветвления — адрес команды образуется путем сложения текущего содержимого РС и 8-раз рядного смещения, которое является числом со знаком). Кроме того, в командах пересылки МОV и сравнения с ветвлением СВЕQ может использоваться индексная адресация с пост-инкрементом или индексная со смещением и пост-инкрементом. Процессор СРU08 выполняет достаточно большой набор команд пересылки, арифметических и логических операций, сдвигов, битовых операций, управления программой и процессором. Группа команд пересылки включает в себя команды загрузки и сохранения содержимого, команды обмена данными между различными регистрами, а также команды, выполняющие сохранение содержимого регистров А, Н и X в стеке и загрузку этих регистров из стека. Команда МОV позволяет осуществлять пересылку 8-разрядпых данных из памяти в память. Команды арифметических операций позволяют выполнять: сложение и вычитание содержимого регистра А и ячейки памяти, производить коррекцию результата сложения двоично-десятичных чисел, выполнять умножение 8-разрядных операндов и деление 16/8. Кроме того, имеются команды 16-разрядного сложения индексного регистра Н:Х или SР с константой. Команды сравнения выполняют установку признаков N, Z, V, C в регистре ССR в соответствии с результатом вычитания двух операндов, хранящихся в регистре и ячейке памяти. Команды тестирования устанавливают значения признаков N, Z в соответствии с содержимым ячейки памяти или регистра А и по результату логической операции «И» над содержимым регистра А и ячейки памяти. Команды логических операций реализуют побитовые операции «НЕ», «И», «ИЛИ», «Исключающее ИЛИ» над содержимым регистра А и адресуемой ячейки памяти. Группа команд сдвига включает команды одноразрядных арифметических, логических и циклических сдвигов, выполняемых над содержимым регистров и ячейки памяти. Команды битовых операций обеспечивают установку в 0 или 1 заданного бита в ячейке памяти. Команды управления программой реализуют условные и безусловные ветвления, вызов подпрограмм и выход из подпрограммы или процедуры обработки прерывания. Условиями ветвления могут быть значения признаков Z, N, результаты сравнения операндов со знаком или без знака (>, >=, <, <=). В эту группу входит также команда программного прерывания SWI Кроме того, процессор реализует команды организации циклов DBNZ и сравнения на равенство с последующим ветвлением CBEQ В зависимости от используемого способа адресации выполнение команд занимает от 1 до 5 тактов; деление производится за 7 тактов. Выполнил материал практической части и изучил рис.1, Рис.2, Рис.3. 3. Ответить на контрольные вопросы Каковы преимущества микроконтроллеров 68НС08/908над семейством 68НС05/705? У 68НС08/908 увеличилась тактовая частота до 8 МГц, список команд с 65 до 90, способы адресации с 6 до 9. Это позволило повысить его производительность от 4 до 6 раз по сравнению с 68НС05/705. Каков состав МК семейства 68НС08/908? ОЗУ данных, ПЗУ или flash память, служебное ПЗУ, ЭСППЗУ, процессор CPU08, служебные и периферийные модули, внутренняя шина данных, последовательные интерфейсные модули и параллельные порты. Каковы характерные особенности моделей серий ВD, SR и GР? Модели серий BD, SR и GP имеют четыре параллельных порта. Ряд серий имеет специализированные последовательные порты, используемые для организации микроконтроллерных сетей. Что включает в себя группа команд пересылки данных? Группа команд пересылки включает в себя команды загрузки и сохранения содержимого, команды обмена данными между различными регистрами, а также команды, выполняющие сохранение содержимого регистров А, Н и X в стеке и загрузку этих регистров из стека. Что реализуют команды управления программой? Они реализуют условные и безусловные ветвления, вызов подпрограмм и выход из подпрограммы или процедуры обработки прерывания. 4. Сделать выводы. В данной работе я познакомился и сравнил семейства МК 68НС05/705 с усовершенствованным МК 68НС08/908. Рассмотрел структуру МК 68НС08/908. Изучил способы реализации и систему команд МК семейства 68НС08/908. |