ЭССОИ_КР_1. Контрольная работа 1 по дисциплине Электронные средства сбора, обработки промышленной и деловой информации учебное пособие В. Л. Савчук Электронные средства сбора, обработки промышленной и деловой информации Часть 1

Скачать 107 Kb. Скачать 107 Kb.

|

|

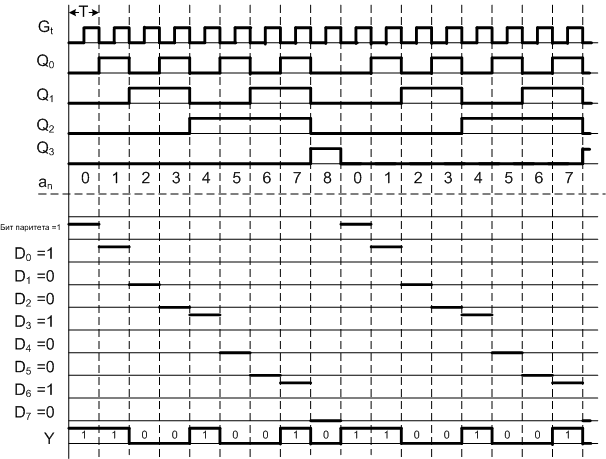

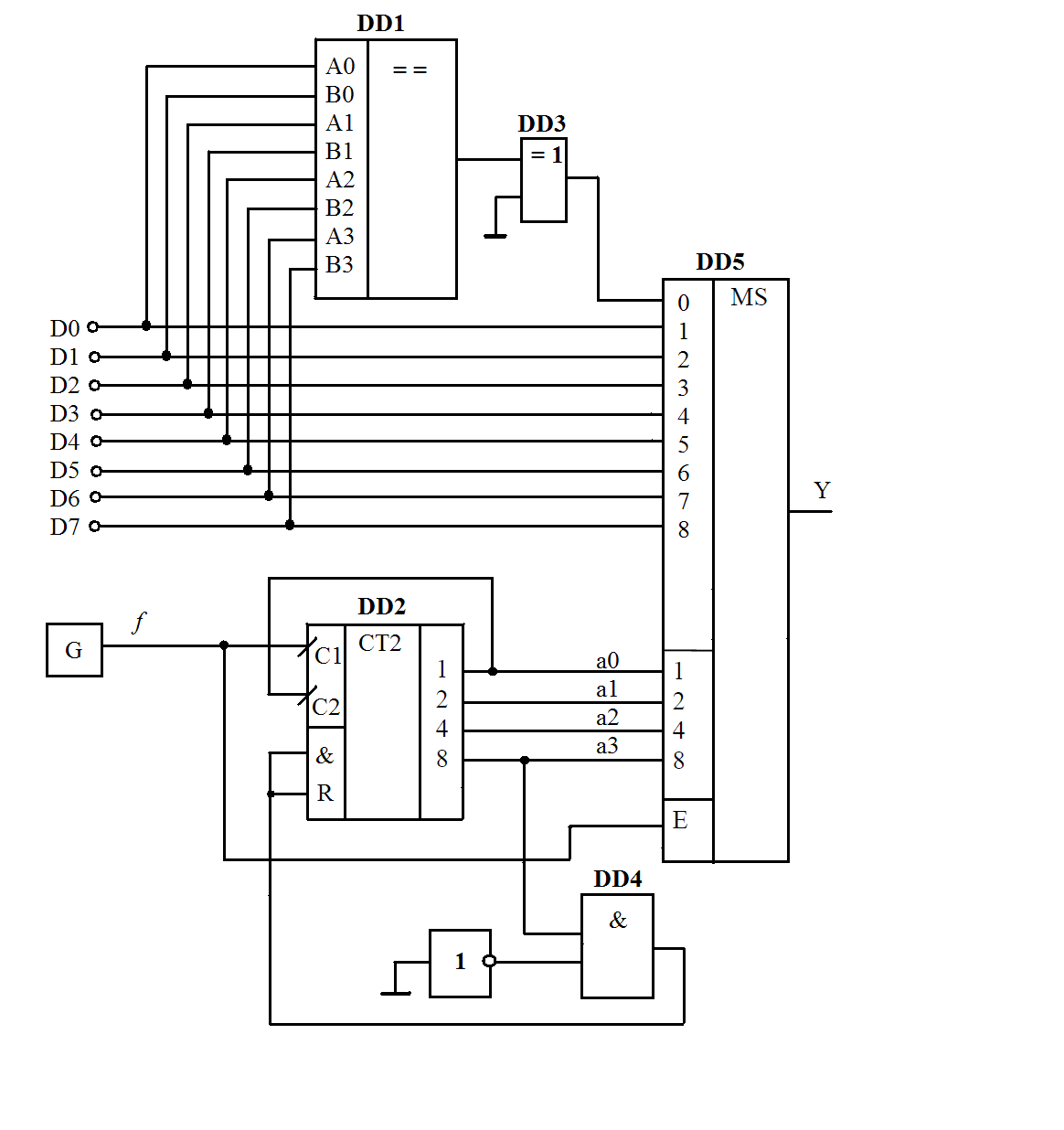

Томский межвузовский центр дистанционного образования Томский государственный университет систем управления и радиоэлектроники (ТУСУР) Кафедра промышленной электроники (ПрЭ) Контрольная работа №1 по дисциплине «Электронные средства сбора, обработки промышленной и деловой информации » учебное пособие В. Л. Савчук «Электронные средства сбора, обработки промышленной и деловой информации Часть 1» учебное методическое пособие В. Л. Савчук «Электронные средства сбора, обработки промышленной и деловой информации» Выполнил студент гр. з-366-б специальности 210106 Сердюков Дмитрий Владимирович 27 июля 2011 г. г. Шымкент 2011 Задание. Разработать кодер однополярного двоичного беспаузного сигнала (БВН) с проверкой на четность. Формат входного двоичного параллельного кода – 8 бит. Входные и выходные сигналы совместимы с ТТЛ. Режим работы – асинхронный, скорость передачи – 2400 бит/с. Исходя из вышеперечисленных условий задания, был разработан кодер на основе элементов DD1 – DD5. DD1 – микросхема К555ИП5 (сумматор по модулю два); DD2 – микросхема 1533ИЕ5 (4-х разрядный двоичный счётчик); DD3 – логический элемент «исключающее ИЛИ»: DD4 – логический элемент «И»; DD5 – 16-ти разрядный мультиплексор (микросхема К555КП1); G – тактовый генератор; Мультиплексор DD5 – переписывает на выход Y, состояние того входа, адрес которого подан на адресные входы а0..а3, с частотой f. Сумматор по модулю два (DD1), определяет четность нулей и единиц входного сигнала D0..D7, и если число не чётное – элемент DD3 («исключающее ИЛИ»), помещает в разряд 0 мультиплексора – логическую 1 (бит паритета), иначе в разряде 0 мультиплексора логический «0». (В приёмном устройстве – после проверки на чётность – младший разряд отбрасывается). 4-х разрядный двоичный счётчик (DD2) – работает с коэффициентом счёта 9 ( как только в разряде 8 будет записана логическая «1», произойдёт сброс на 0 счётчика). Таким образом, реализован последовательный перебор значений от 0 до 8, что в свою очередь вызывает последовательный вывод на выход Y – бит информации на входе. Временные диаграммы приведены на рис.1. Схема электрическая принципиальная, разработанного кодера, представлена на рис.2.  Рис. 1 – Временные диаграммы  Рис. 2 – Схема электрическая принципиальная Список используемой литературы. Шарапов А.В.Цифровые и микропроцессорные устройства: Учебное пособие. – Томск:-2003. - 166 с. Савчук В.Л. Электронные средства сбора, обработки промышленной и деловой информации: Учебное методическое пособие. – Томск:-1997. – 19 с. Савчук В.Л. Электронные средства сбора, обработки промышленной и деловой информации: Учебное пособие. Часть 1: – Томск:-2002. – 76 с. |