МПС. Экзамен Крылов И.А. П-477. Крылов И. А. П477 вариант 9 Задача

Скачать 66.24 Kb. Скачать 66.24 Kb.

|

|

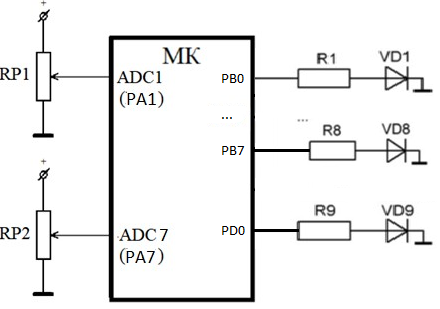

Крылов И.А. П-477 вариант 9 Задача: Нарисовать функциональную схему, рассчитать требуемые параметры настройки, составить программу преобразования аналогового значения ошибки по скорости двигателя в цифровой код: аналоговый сигнал задания: 7 канал АЦП, сигнал аналоговой обратной связи по скорости: 1 канал АЦП; работа АЦП: с однократным преобразованием, левым выравниванием, источник AREF (5В), количество разрядов АЦП - 9; вывод выполнить в порты D (старший байт) и B (младший байт). В таблице пояснить процесс получения 9 бит выходного кода при заданном выравнивании сигнала АЦП. Канал аналогового ввода: ADC7 – ADC1 Выравнивание результата и режим работы АЦП: Левое; однократный. Вывод в порты D (старший байт) и B (младший байт). Функциональная схема:  АDC1, ADC7 – аналоговые входы RP1, RP2 – потенциометры задания входных сигналов Настройка: Настройка регистра управления мультиплексором АЦП ADMUX: ADMUX=0 0 1 1 0 1 1 1 = $37 5 бит=1 т.к. левое выравнивание; 6 и 7 биты = 0 т.к. внешний источник 5 В; Первые 4 бита из за ADC7-ADC1. Настройка регистра управления АЦП ADCSRA: ADCSRA= 1 1 0 0 1 1 1 1 = $CF 7 бит разрешение работы 6 бит разрешение преобразования 5 бит = 0 т.к. у нас не циклический режим работы. 4 бит флаг готовности 3 бит прерывание 2-0 биты предделитель = 128 Таблица: Постарался пояснить как реализовал перенос 9 бита

Программа: .include"m32def.inc" .cseg .org 0 rjmp reset .org $20 rjmp ADC7_1 reset: ldi r16,low(RAMEND) ; инициализация стека ldi r17,high(RAMEND) out spl,r16 out sph,r17 clr r16 ;настройка портов ser r16 out DDRA,r16 out DDRD,r17 out DDRB,r17 ldi r17,0x37 ; настройка ADMUX out ADMUX,r17 ldi r17,0xCF ; настройка ADCSRA out ADCSRA,r17 sei main: ; основной цикл rjmp main ADC7_1: ;подпрограмма ldi r17,0xCF out ADCSRA,r17 in r20,ADCL ; считывание in r21,ADCH andi r20,0x80 ; оставляем только ADC1 rol r20 rol r20 ;сдвигаем из единицы переноса mov r22,r21 ;r22 регистр будем использовать для операций сдвига lsl r22 or r20,r22 ; добавляем в ADCH ADC1 andi r21,0x80 ; ADC9 rol r21 rol r21 ;0000 0001 out PORTB,r20 ; вывод в порты out PORTD,r21 reti правое выравнивание 8 бит in r20,ADCL ; считывание in r21,ADCH lsr r20 lsr r20 ror r21 ror r21 ror r21 or r21, r20 out portB r21 reti

| |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||