Курсовая работа. Курсовая работа Быстродействующее однотактное устройство табличного типа для вычисления логарифма входного числа

Скачать 1.04 Mb. Скачать 1.04 Mb.

|

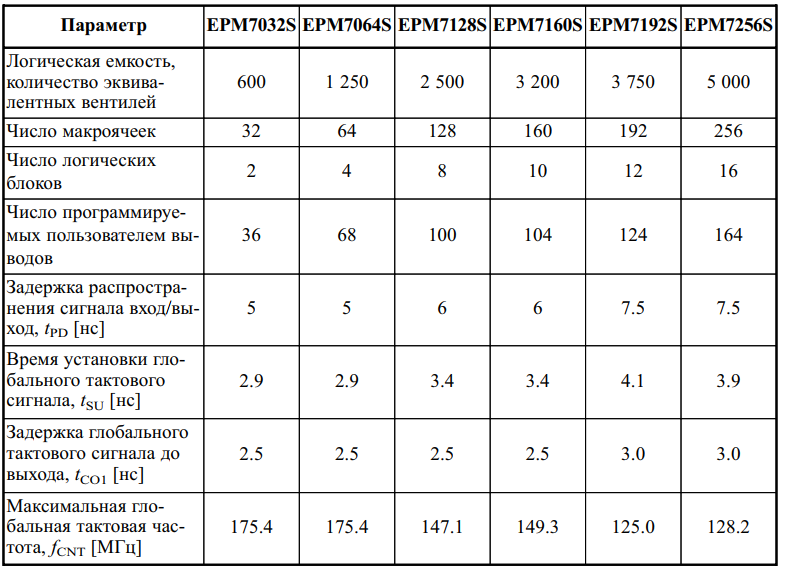

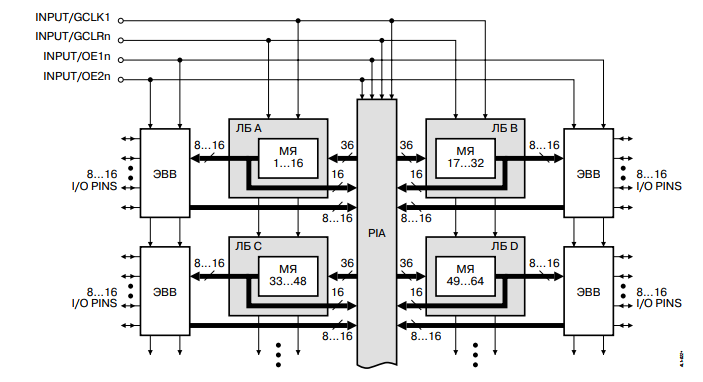

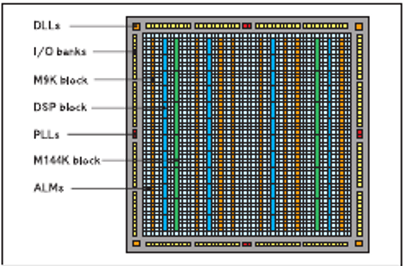

Технология фирмы AlteraФирма Altera также является одним из лидеров проектирования и поставок ПЛИС. Ею освоены технологии производства CPLD и FPGA. Altera выпускает CPLD серий MAX3000А, MAX7000В, MAX7000А, MAX7000, MAX II и FPGA серий ACEX, APEX, Mercury, Excalibur, Cyclone, Stratix [CITATION 1910 \l 1033 ]. Продукция Altera широко применяется в военной, автомобильной промышленности, IT-технологиях, медицинском оборудовании, при создании контрольно-измерительного оборудования, в беспроводных и проводных средствах связи и передачи. В настоящее время выпускаются CPLD семейств МАХ7000, МАХ7000А, МАХ7000В, МАХ7000Е, МАХ7000S. Семейства МАХ7000А и МАХ7000В рассчитаны на работу в системах с напряжением питания 3.3 и 2.5 В соответственно. Семейство МАХ7000S является дальнейшим развитием 5-вольтового семейства МАХ7000, допуская возможность программирования в системе, что упрощает процесс модернизации изделий. Основные характеристики МАХ7000S приведены в таблице 1.4 [ CITATION авт19 \l 1049 ]. Общий вид архитектуры семейств серии МАХ7000 приведен на рисунке 1.5. Таблица 1.4 Основные характеристики МАХ7000S   Рисунок 1.5 – Архитектура семейства МАХ7000 Новое семейство FPGA — Stratix III — сочетает высокую производительность, большой логический объем и малое энергопотребление [ CITATION Про19 \l 1049 ]. Главная особенность Stratix III — сниженное до двух раз энергопотребление (как динамическое, так и статическое) по сравнению с семействами FPGA предыдущего поколения, без потери производительности. Этого удалось достигнуть за счет реализации технологии программируемого энергопотребления (Programmable Power Technology), которая позволяет конфигурировать ресурсы ПЛИС (логические блоки, блоки цифровой обработки, блоки памяти) либо в режим с высокой производительностью, либо в режим с пониженным энергопотреблением. Предлагаемые фирмой Altera средства разработок предоставляют возможность анализировать проект и определять, какая производительность необходима тому или иному блоку. Блоки, не требующие высокой производительности (в том числе и неиспользуемые в проекте), устанавливаются в режим пониженного энергопотребления. Блоки, функционирование которых критично ко времени, устанавливаются в высокоскоростной режим. Таким образом, технология программируемого энергопотребления позволяет совместить в одном проекте два до сих пор не совместимых требования. Возможность устанавливать блоки ПЛИС либо в высокоскоростной режим, либо в режим с низким энергопотреблением, — новое слово в мире программируемой логики. Другая особенность семейства Stratix III, способная снизить энергопотребление, — возможность выбора напряжения питания ядра (VCCint). Для проектов, где определяющим фактором является высокая производительность, используется напряжение питания ядра 1,1 В. Для проектов, требующих пониженного энергопотребления, — 0,9 В. Микросхемы Stratix III будут выпускаться по 65-нанометровой технологии. Внутренние тактовые частоты Stratix III могут достигать 600 МГц. Максимальная производительность FPGA Stratix III на 25% выше, чем у семейств ПЛИС предыдущего поколения. Семейство Stratix III разделено на три подсемейства, каждое из них оптимизировано для определенных приложений: • Stratix III L — для решения задач, где требуется большая логическая емкость; • Stratix III E — для решения задач цифровой обработки сигналов и задач, требующих применения больших объемов памяти; • Stratix III GX — для решения задач высокоскоростных коммуникаций (микросхемы данного подсемейства будут содержать мультигигабитные трансиверы). FPGA Stratix III (рисунок 1.6) содержат массив адаптивных логических модулей, высокопроизводительные и гибкие блоки памяти и блоки цифровой обработки сигналов, блоки фазовой автоподстройки частоты (PLL) и блоки автоподстройки частоты по задержке (DLL). FPGA Stratix III содержат до двадцати четырех высокопроизводительных банков ввода-вывода. Наличие банков ввода-вывода с поддержкой различных интерфейсов внешней памяти и лучшими на сегодняшний день средствами обеспечения целостности сигналов существенно облегчают проектирование печатных плат для FPGA Stratix III. А встроенные средства защиты позволяют обезопасить проект от несанкционированного копирования или модификации. Объем аппаратных ресурсов - до 340 тыс. эквивалентных логических элементов, 21 Мбит встроенной памяти и 576 встроенных умножителей. Встроенные в FPGA подсемейства Stratix IIIЕ умножители 18x18 бит работают на частотах до 600 МГц. Встроенное ОЗУ FPGA Stratix III может работать на частотах до 600 МГц. Общий объем встроенной памяти может достигать 21 Мбит. FPGA Stratix III содержат блоки ОЗУ трех видов: • блоки MLAB. Объем блока MLAB 640 бит, FPGA может содержать до 6750 таких блоков. Блоки памяти MLAB могут использоваться для реализации сдвиговых регистров и буферов FIFO небольшого объема, линий задержек и т. п.; • блоки M9K. Объем блока M9K 9216 бит, FPGA может содержать до 1144 таких блоков. M9K используются как блоки памяти общего назначения; • блоки M144K. Объем блока 147 456 бит, FPGA может содержать до 48 таких блоков. Назначение блоков памяти M144K — хранение исполняемого кода синтезируемых процессорных ядер, реализация буферов большого объема для формирования пакетов при передаче данных или кадров в задачах обработки изображений. Наличие блоков памяти разного объема позволяет оптимальным образом размещать различные устройства на кристалле FPGA.  Рисунок 1.6 – Структура FPGA Stratix Еще одной особенностью ПЛИС фирмы Altera является наличие собственного микропроцессорного ядра, встраиваемого в архитектуру кристалла [ CITATION Про191 \l 1049 ]. NiosII является конфигурируемым процессорным RISC ядром общего назначения фон-неймановской архитектуры разрядностью 32 бита и может быть интегрирован в ПЛИС фирмы Altera, относящиеся к семействам на базе статической памяти (Cyclone, CyloneII, Stratix, StratixII). В отличие от обычных микропроцессоров и микроконтроллеров, поставляющихся с фиксированным набором периферийных устройств и объемом памяти, система на основе NiosII настраивается на этапе проектирования под конкретную задачу. Вместе с ядром NiosII поставляется ряд функциональных модулей стандартных периферийных устройств: параллельный ввод-вывод, универсальный асинхронный приемопередатчик (UART), последовательный интерфейс SPI, таймер и другие. Поддерживается как программная эмуляция, так и отладка в системе. Программные средства разработки включают в себя две линейки программных продуктов: MAX-Plus II и Quartus II [ CITATION Стр \l 1049 ]. |