Курсовая работа. Курсовая работа Быстродействующее однотактное устройство табличного типа для вычисления логарифма входного числа

Скачать 1.04 Mb. Скачать 1.04 Mb.

|

Сравнительная характеристика технологий Xilix и AlteraУ разработчиков часто встает вопрос: какую из существующих технологий выбрать для реализации своего проекта. Объективно оценить это очень трудно. Поэтому каждый выбирает по своим предпочтениям. Компания Altera предложила методику, которая позволяет оценить производительность, коэффициент заполнения кристалла и время компилирования FPGA разных производителей. Эта методика обсуждается на примере сравнения FPGA семейств Stratix III и Virtex-5 [ CITATION Сра19 \l 1049 ]. Компания Altera производит оценку FPGA с помощью программного средства разработки Quartus II, используя комплексный набор типовых проектов заказчика, которые отражают различные области применения, например, сетевые технологии, телекоммуникации, беспроводная и бытовая техника. К тому же проекты реализованы на основе различной технологии, например, ASIC, вентильные матрицы и FPGA других производителей. Отобранные проекты (которые хранятся в защищенной базе данных) используются для того, чтобы сравнить функционирование реальных устройств заказчиков с разрабатываемой в текущий момент архитектурой. Проекты, не оптимизированные для FPGA компании Altera, оцениваются по результатам более 150 тыс. тестов; затем на основе анализа предлагаются рекомендации по совершенствованию архитектуры следующих поколений FPGA или инструментов разработки. Для сравнительного анализа были отобраны семь наиболее популярных и крупных проектов на интернет - ресурсе www.opencores.org, которые представлены в таблице 1.5 [CITATION Как \l 1049 ]. Таблица 1.5 Исследуемые проекты

Для тестирования были использованы FPGA компаний Altera и Xilinx с наибольшей логической емкостью и близкими параметрами. В таблице 1.6 приведены данные о выбранных для сравнения FPGA компаний Altera и Xilinx, а также о соответствующем программном обеспечении. Таблица 1.6 Сравниваемые FPGA компаний Altera и Xilinx

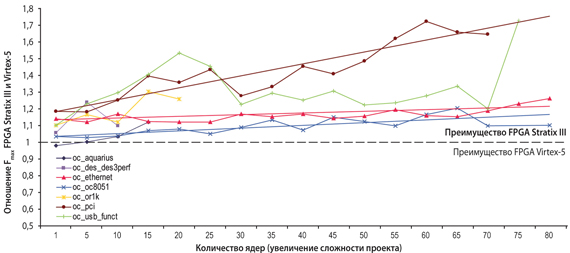

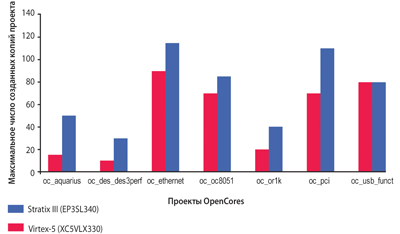

На рисунке 1.7 по оси Y отложено отношение максимальной рабочей частоты FPGA Stratix III FPGA к максимальной рабочей частоте FPGA Virtex-5. На оси X показано количество ядер, скопированных для каждого из семи проектов OpenCores. Все отношения выше линии, соответствующей единице, что указывает на преимущество в производительности FPGA Stratix III.  Рисунок 1.7 - Преимущество в производительности FPGA Stratix III увеличивается с увеличением сложности проекта (степени заполнения кристалла FPGA) Проверка по коэффициенту заполнения кристалла показала (рисунок 1.8): FPGA Stratix III в среднем имеет на 46% больший коэффициент заполнения кристалла, чем у сравниваемого прибора. Программное средство Quartus II позволяет достичь максимального заполнения кристалла адаптивными логическими модулями (АЛМ) для реализации логических функций, которые чрезвычайно эффективны из-за гибкости АЛМ.  Рисунок 1.8 - Максимально возможное число копий проектов на FPGA Stratix III и Virtex-5 Таблица 1.7 показывает максимальное число созданных копий и коэффициент заполнения FPGA Stratix III и Virtex-5. Таблица 1.7 Максимальное число созданных копий и коэффициент заполнения FPGA Stratix III и Virtex-5

В таблице 1.8 представлены данные по времени компилирования проекта, которое ограничено максимальным количеством ядер, размещенных в сравниваемых FPGA. Полученные результаты показывают, что компилирование FPGA Stratix III происходит значительно быстрее, чем FPGA Virtex-5. Таблица 1.8 Сравнение времени компилирования FPGA Stratix III и Virtex-5

Результаты оценки показали, что преимущества FPGA Stratix III в части производительности, коэффициента заполнения и времени компилирования увеличиваются с ростом сложности проекта. Это объясняется оптимальной архитектурой FPGA, которую с успехом использует программный инструмент разработки Quartus II. В силу указанных преимуществ для реализации целей курсового проекта выбрано семейство микросхем FPGA фирмы Altera и программный продукт Quartus II. | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||