Курсовая работа. Курсовая работа Быстродействующее однотактное устройство табличного типа для вычисления логарифма входного числа

Скачать 1.04 Mb. Скачать 1.04 Mb.

|

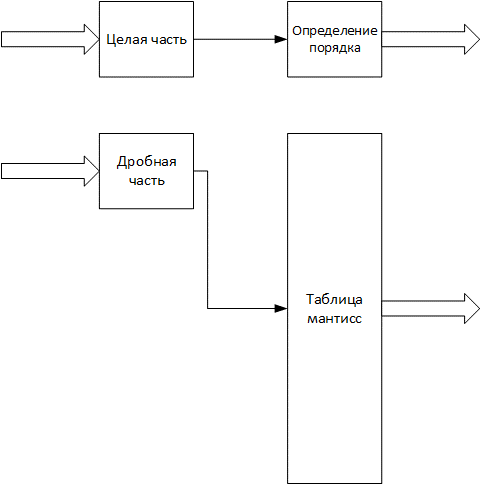

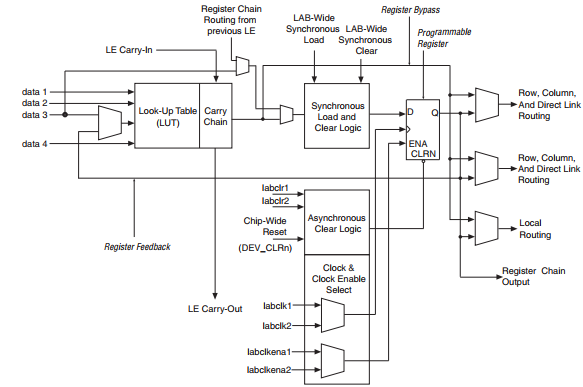

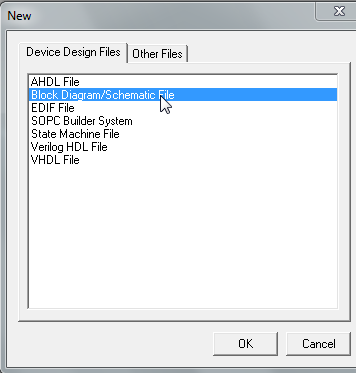

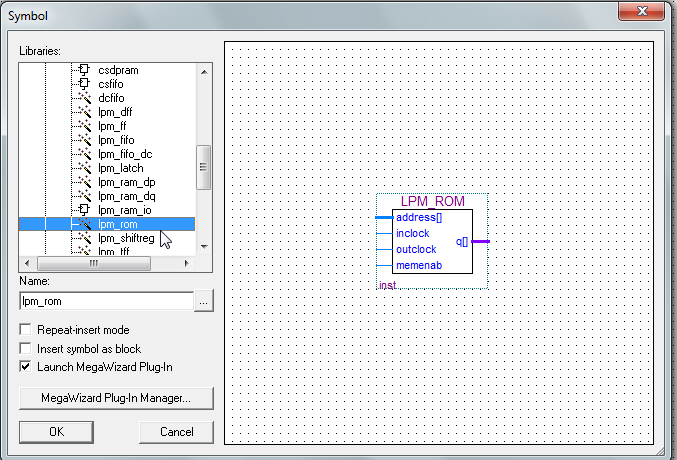

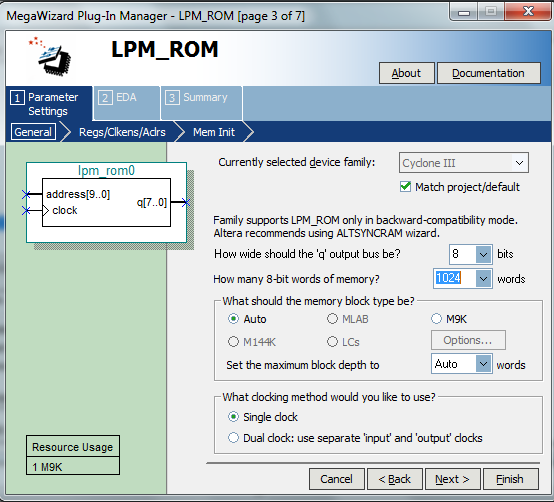

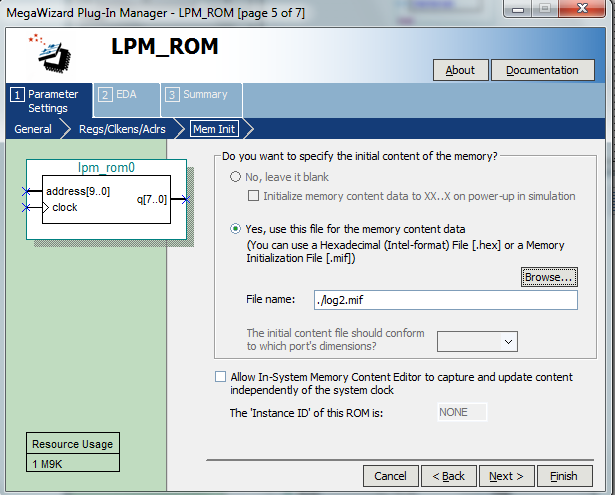

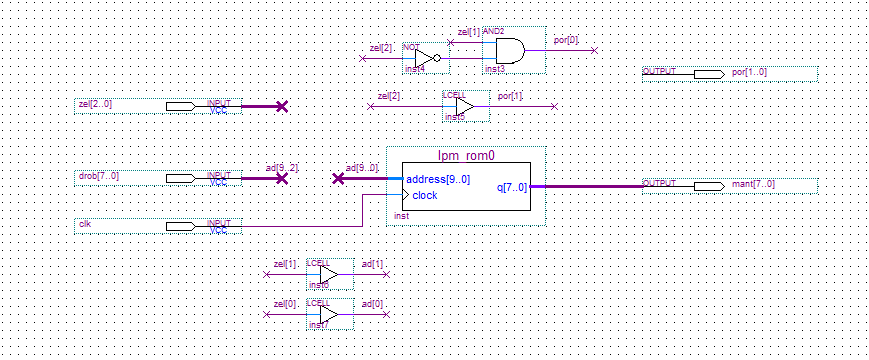

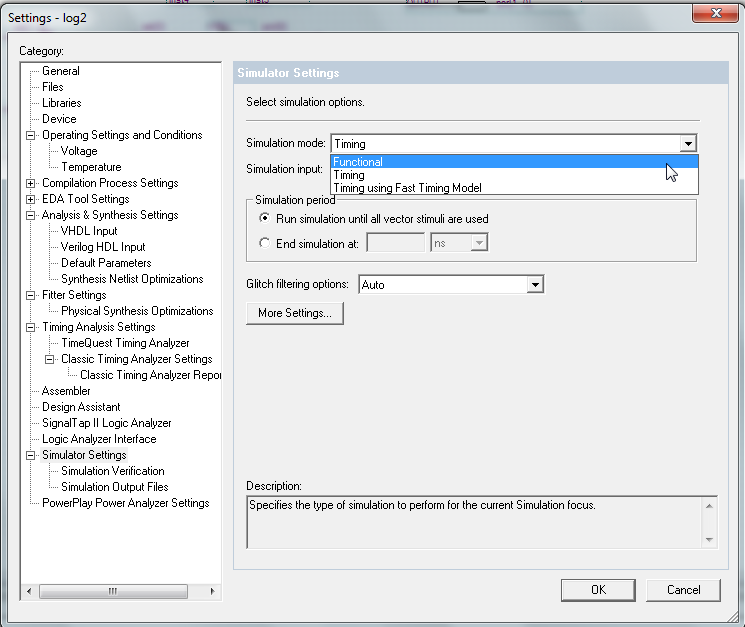

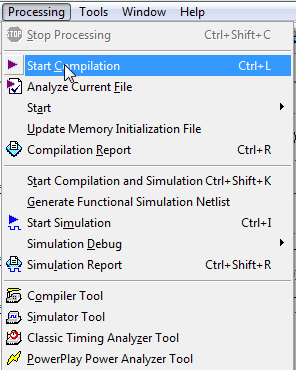

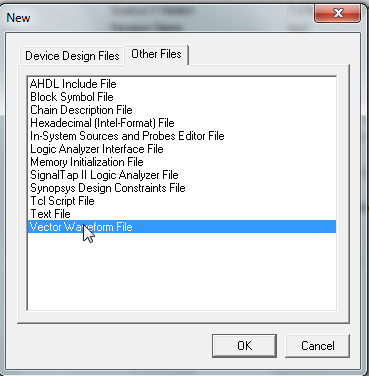

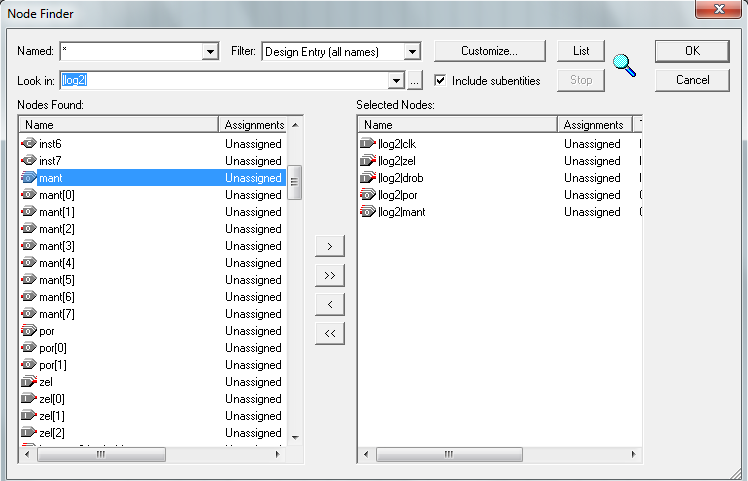

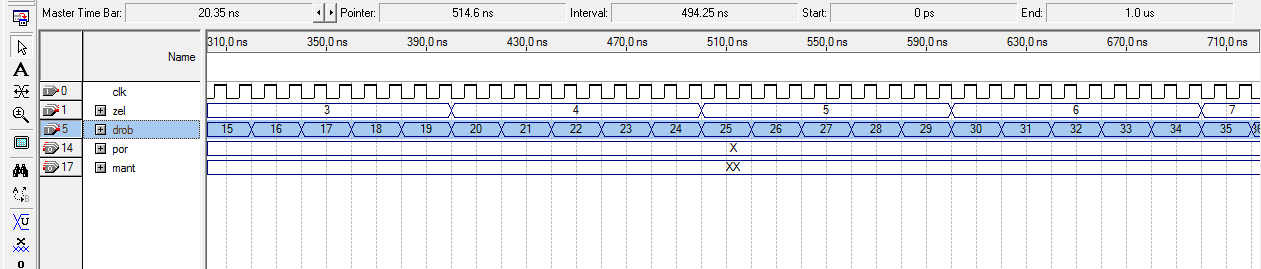

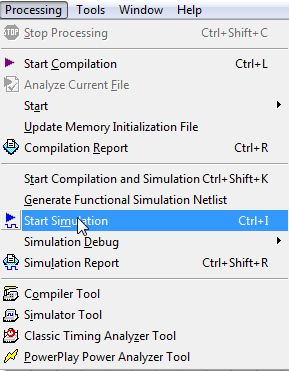

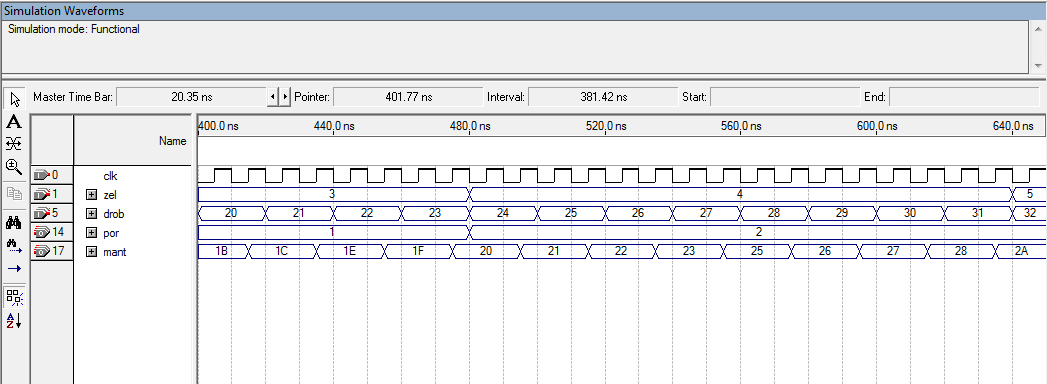

3.2 Разработка быстродействующего однотактного устройства табличного типа для вычисления логарифма входного числа2.1 Разработка функциональной схемыФункция логарифма часто встречается в специализированных вычислителях. Например, при цифровой обработке сигналов логарифмическая шкала используется для сравнения уровней сигналов в децибелах, в простых алгоритмах сжатия сигналов, некоторых алгоритмах нелинейной обработки сигналов. В спецвычислителях выгодно вычислять функцию логарифма по основанию 2. Во-первых, если аргумент x — число с фиксированной точкой, то порядок логарифма на единицу меньше числа значащих цифр p, а мантисса может быть задана таблично. Во-вторых, значение логарифма по любому основанию может быть найдено путем умножения на величину, обратную двоичному логарифму требуемого основания. Для проекта выбрано вычисление двоичного логарифма чисел с фиксированной точкой с применением таблицы, поскольку в ПЛИС существенно проще выполнять именно операции с фиксированной точкой. Функциональная схема устройства приведена на рисунке 2.1. При одинаковой размерности дробной части с увеличением порядка на 1 объем таблицы возрастает вдвое. При выборе максимального размера порядка возможно использовать одну и ту же таблицу, выбирая значения мантиссы по адресам с учетом порядка, т.е. каждое 2-е, 4-е и т.д. значения.  Рисунок 2.1 – Функциональная схема устройства 2.2 Ресурсы ПЛИС Cyclone IV E: EP4CE115F29C7Для реализации проекта предложено использовать микросхему FPGA фирмы Altera Cyclone IV E: EP4CE115F29C7, способную работать в диапазоне частот от 5 до 155.5 МГц [ CITATION Cyc16 \l 1049 ]. Микросхема выполнена в корпусе FBGA-780. Допускается использовать до 528 входов/выходов. Рабочий диапазон температур 0 – 850С. В составе микросхемы 114 480 логических элемента, способных выполнять логические функции 4 переменных и функции триггеров различных типов. Функциональная схема логического элемента приведена на рисунке 2.2.  Рисунок 2.2 – Функциональная схема логического элемента В составе микросхемы имеютя 8 блоков памяти М9К, объемом 8192 бита с поддержкой битов паритета.Блоки могут быть сконфигурирова как 8192х1, 4096х2, 2048х4, 1024х8, 1024х9, 512х16, 256х32, 256х36. Блоки памяти могут использоваться как одно- и двух портовые RAM, ROM, FIFO и регистры сдвига. В состав ПЛИС входят 266 умножителей 18х18 бит. 2.3 Расчет таблицы мантиссДля формирования таблицы мантисс и загрузочного файла ROM воспользуемся средствами системы Матлаб [ CITATION Дья081 \l 1049 ]. Для реализации проекта воспользуемся конфигурацией памяти 1024х8. Это позволит получить 8-ми битовую мантиссу. Точность представления мантиссы составит 1/256≈4∙10-3. Объем памяти 1 кбайт. Это при 8-ми разрядной дробной части входного числа позволит представить логарифмы от 1 до 8 с шагом 1.256. Составим программу формирования файла mif для загрузки ПЗУ. i1=4:2^-8:8-2^-8; x1=floor((log2(i1)-2)*2^8); s='log2.mif'; h1=fopen(s,'wt'); fprintf(h1,'%s\n','DEPTH = 1024;'); fprintf(h1,'%s\n','WIDTH = 8;'); fprintf(h1,'%s\n','ADDRESS_RADIX = HEX;'); fprintf(h1,'%s\n','DATA_RADIX = HEX;'); fprintf(h1,'%s\n','CONTENT'); fprintf(h1,'%s\n','BEGIN'); for i=1:length(x1) fprintf(h1,'%s\t',dec2hex((i-1),3)); fprintf(h1,'%c\t',':'); fprintf(h1,'%s;\n',dec2hex(x1(i),2)); end fprintf(h1,'%s\n','END;'); fclose('all'); Файл log2.mif прилагается. 2.4 Проектирование в среде Quartus IIРеализация начинается с создания нового проекта из меню File под руководством Менеджера проектов, в котором указывается рабочий директорий, имя проекта, файл верхней иерархии, тип микросхемы. Далее создается блок-схема средствами графического редактора из меню File (рисунок 2.3).  Рисунок 2.3 – Создание блок-схемы Затем на поле проекта создается блок-схема из библиотеки типовых элементов. Для создания ROM используем мегафункцию lpm_rom и указываем разрядность и объем памяти, имя загрузочного файла (рисунки 2.4 – 2.6).  Рисунок 2.4 – lpm_rom  Рисунок 2.5 – Параметры мегафункции  Рисунок 2.6 – Загрузочный файл Схема вычислителя логарифма приведена на рисунке 2.7.  Рисунок 2.7 – Блок-схема проекта После сохранения файла схемы необходимо откомпилировать проект. Указываем, что при моделировании будем использовать функциональный анализ (рисунок 2.8).  Рисунок 2.8 – Функциональный анализ Процедура запуска компиляции проекта показана на рисунке 2.9.  Рисунок 2.9 – Процедура запуска компиляции проекта Затем создается файл моделирования (рисунки 2.10 – 2.12).  Рисунок 2.10 – Выбор файла моделирования  Рисунок 2.11 – Задание набора сигналов  Рисуно 2.12 – Формирование входных сигналов Далее осуществляется симуляция проекта (рисунок 2.13).  Рисунок 2.13 – Запуск симуляции проекта Результаты симуляции приведены на рисунке 2.14.  Рисунок 2.14 – Результат симуляции Анализ временных диаграмм показывает, что устройство работтает согласно заложенному алгоритму. 4.ЗаключениеРазработан проект быстродействующего однотактного устройства табличного типа для вычисления логарифма входного числа. Выполнено формирование таблицы логарифмов в системе Матлаб. Проведенная верификация проекта показала правильность принятых решений. 5.Список литературыCITATION НКо14 \l 1033 : , [1], CITATION ПЛИ \l 1033 : , [2], CITATION МКу05 \l 1033 : , [3], CITATION АСе \l 1049 : , [4], CITATION Арх19 \l 1033 : , [5], CITATION При \l 1049 : , [6], CITATION Web19 \l 1033 : , [7], CITATION 1910 \l 1033 : , [8], CITATION авт19 \l 1049 : , [9], CITATION Про19 \l 1049 : , [10], CITATION Про191 \l 1049 : , [11], CITATION Стр \l 1049 : , [12], CITATION Сра19 \l 1049 : , [13], CITATION Как \l 1049 : , [14], CITATION Cyc16 \l 1049 : , [15], CITATION Дья081 \l 1049 : , [16],

|