Дискретное косинусоидальное преобразование Aldec. Курсовая работа по дисциплине Схемотехника Тема дкп студентка гр. 8363 Снопок Е. М. Преподаватель

Скачать 357.33 Kb. Скачать 357.33 Kb.

|

|

МИНОБРНАУКИ РОССИИ Санкт-Петербургский государственный электротехнический университет «ЛЭТИ» им. В.И. Ульянова (Ленина) Кафедра Систем автоматизированного проектирования Курсовая РАБОТА по дисциплине «Схемотехника» Тема: ДКП

Санкт-Петербург 2020 ЗАДАНИЕ на курсовую работу

Аннотация В ходе выполнения лабораторной работы была спроектирована схема максимума матрицы в среде САПР-Active HDL (Aldec), так же был разработан VHDL-код схемы. С помощью разработанной программы можно найти дискретное косинусное произведение матрицы, и получить на выходе результатом матрицу, на которой было произведено ДКП. Summary During the laboratory work, the maximum matrix scheme was designed in the CAD environment-Active HDL (Aldec), as well as the VHDL code of the scheme was developed. Using the developed program, you can find Discrete Cosine Transform of matrix, and get as the result matrix where DCT was used. содержание

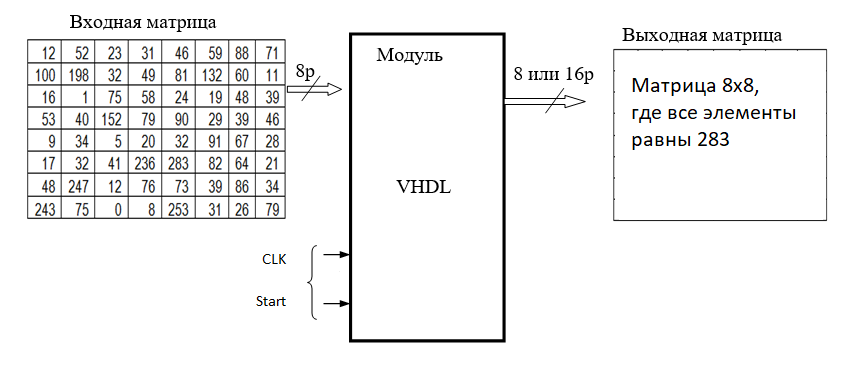

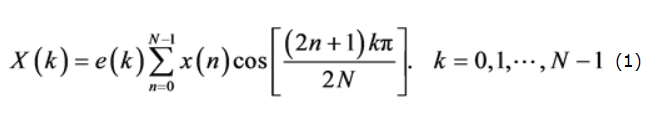

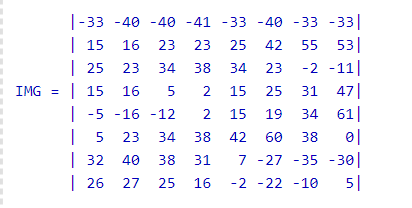

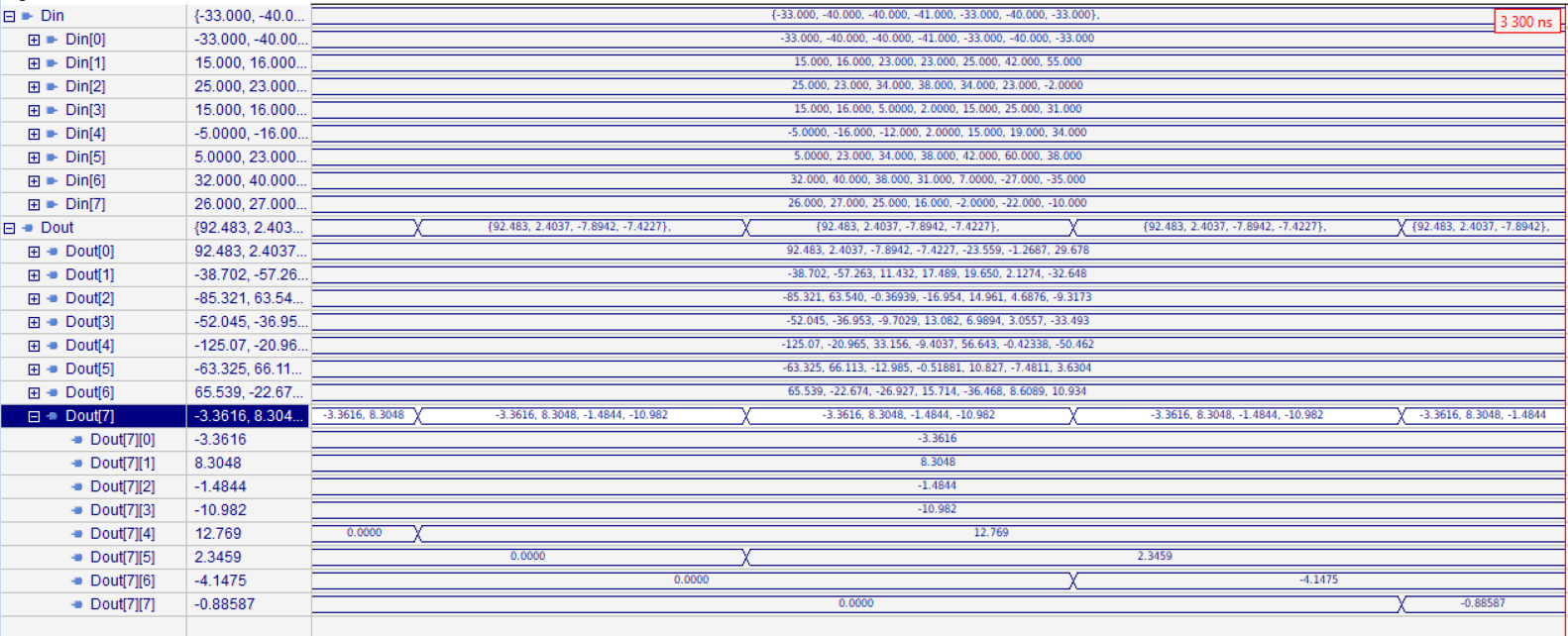

введение В качестве входных данных в разрабатываемый модуль передаётся матица размером 88 (64 элементов) целых чисел v{0, , 255}. Матрица передается по входной 8-и разрядной шине данных в разрабатываемый модуль и на выходе тоже получаем матрицу того размера 88. Теоретическая часть Описание модуля и числовые примеры работы схемы  Рис. 1. Пример входной и выходной матриц С помощью разработанной программы можно найти дискретное косинусное произведение матрицы, и получить на выходе результатом матрицу, на которой было произведено ДКП. Алгоритм требуемого модуля Считываем с входной шины исходную матрицу Задаем матрицу коэффициентов дискретного косинусного преобразования, которая находится по формуле, показанной на рисунке 1, где N для нашего случая равно 8.  Рисунок 1 Проходим два цикла (по строкам и столбцам), зануляя значения временных матриц, так как без объявления переменных в этих матрицах, туда запишется -256, хотя должен быть 0. Проходим три цикла (по строкам и столбцам, 3-ий цикл нужен для нескольких проходов на том же месте), чтобы получить перемножение между матрицей коэффициентов и входной матрицей. Проходим два цикла, чтобы транспонировать полученную матрицу. Проходим три цикла (по строкам и столбцам, 3-ий цикл нужен для нескольких проходов на том же месте), чтобы получить перемножение между матрицей коэффициентов и полученной транспонированной матрицей. Проходим два цикла, чтобы транспонировать итоговую матрицу. Выводим итоговую матрицу в выходную шину. Описание фрагментов VHDL кода В ходе написания кода мне понадобились знания по следующим разделам: Типы данных в VHDL. Основным типом, наиболее адекватно представляющим цифровые сигналы, является std_logic. Он может принимать следующие значения: ‘U’ – не инициализировано; ‘X’ – неизвестное значение, формируемое активным выходом; ‘0’ – логический ноль; ‘1’ – логическая единица; ‘Z’ – «третье состояние», состояние высокого импеданса выхода; ‘W’ – «слабое неизвестное» значение; ‘L’ – «слабый ноль», состояние логического нуля, формируемое источником сигнала с более высоким сопротивлением, чем обычный логический выход; ‘H’ – «слабая единица», состояние логической единицы, формируемое источником сигнала с более высоким сопротивлением, чем обычный логический выход; ‘-‘ – произвольное значение (don’tcare). Для сигналов, описанных как std_logic, допустимо большинство операций – побитные логические, операции сравнения и сдвига. Формально, сигналы типа std_logic не могут участвовать в арифметических выражениях, однако на практике синтезаторы допускают это путем перегрузки (overloading) арифметических операторов. Типы INTEGER и REAL определяют численные данные — целые и действительные соответственно. Диапазон представления чисел может зависеть от реализации, но стандартными считаются диапазоны {-231+1, +231-1} для типа INTEGER. ARRAY (<диапазон> «,<диапазон> »)OF<тип элемента массива>. Диапазон задает множество допустимых значений индекса. Число измерений массива формально не ограничено. Если диапазон задан конструкцией RANGE<>, то это является объявлением неограниченного массива. В этом случае определяется не диапазон значений индекса, а только тип индексной переменной. Такое определение предполагает задание диапазона при определении конкретного экземпляра объекта, относимого к такому типу, например, при вызове подпрограмм. В подобных случаях диапазон устанавливается динамически в соответствии с диапазоном подставляемого фактического параметра. Алгоритм перемножения матриц, транспонирования матриц и прямого преобразования на С++ (представлен далее.) Void MultiMatrix(m8x8 m1,m8x8 m2, m8x8 res){ for(int i=0;i for(int k=0;k } } Void TransponMatrix(m8x8 m1, m8x8 res){ for(int i=0;i res[i][j]=m1[j][i]; } Void FDCT_8x8(m8x8 m1, m8x8 res){ MultiMatrix(A,m1,a1); MultiMatrix(a1,AT,res); } 2. Практическая часть 2.1. Разработка и описание фрагментов кода Первый файл с package add, где объявляется новый тип данных matrixreal (тип данных размером 8x8 с вещественными элементами от -255.0 до 255.0). library IEEE; use IEEE.STD_LOGIC_1164.ALL; package add is type vectrreal is array(0 to 7) of real range -255.0 to 255.0; type matrixreal is array(0 to 7) of vectrreal; end package add; Второй файл с использованием первого: library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.NUMERIC_STD.ALL; use ieee.std_logic_unsigned.all; use ieee.std_logic_arith.all; use work.add.all; Объявление входных и выходных портов: Имя порта: Clk; Тип порта: Входной порт типа std_logic; Назначение порта: Порт, отвечающий за время; Имя порта: Start; Тип порта: Входной порт типа std_logic; Назначение порта: Порт, разрешающий начать работу модуля; Имя порта: Din; Тип порта: Входной порт типа matrixreal; Назначение порта: Порт, соответствующий входной матрице; Имя порта: Done; Тип порта: Выходной порт типа std_logic; Назначение порта: Порт, отвечающий за этап работы модуля; Имя порта: Dout; Тип порта: Выходной порт типа matrixreal; Назначение порта: Порт, соответствующий выходной матрице; Тело кода: Объявляем новые переменные: Имя переменной: i, j, k; Тип переменной: integer; Назначение переменной: индексы, нужные для цикла в матрице; Имя переменной: InBlock; Тип переменной: matrixreal; Назначение переменной: Входная матрица; Имя переменной: OutBlock; Тип переменной: matrixreal; Назначение переменной: Выходная матрица; Имя переменной: dct; Тип переменной: matrixreal; Назначение переменной: Матрица Коэффициентов; Имя переменной: temp; Тип переменной: matrixreal; Назначение переменной: Временная матрица, полученная после произведения матрицы коэффициентов на входную матрицу; Имя переменной: dctt; Тип переменной: matrixreal; Назначение переменной: Временная матрица, полученная после транспонирования матрицы temp; Имя переменной: OutBlock; Тип переменной: matrixreal; Назначение переменной: Временная матрица, полученная после произведения матрицы коэффициентов на матрицу temp; Имя переменной: OutAnother; Тип переменной: matrixreal; Назначение переменной: Временная матрица, полученная после транспонирования матрицы OutBlock, является результатом работы программы, и выгружается в выходную шину. Задаем значение матрице коэффициентов dct; dct := ( (0.354, 0.354, 0.354, 0.354, 0.354, 0.354, 0.354, 0.354), (0.490, 0.416, 0.278, 0.098, -0.098, -0.278, -0.416, -0.490), (0.462, 0.191, -0.191, -0.462, -0.462, -0.191, 0.191, 0.462), (0.416, -0.098, -0.490, -0.278, 0.278, 0.490, 0.098, -0.416), (0.354, -0.354, -0.354, -0.354, 0.354, -0.354, -0.354, 0.354), (0.278, -0.490, 0.098, 0.416, -0.416, -0.098, 0.490, -0.278), (0.191, 0.462, 0.462, -0.191, -0.191, 0.462, -0.462, 0.191), (0.098, 0.278, 0.416, -0.490, 0.490, -0.416, 0.278, -0.098)); Ждем разрешения начала работы модуля с помощью порта Start; wait until Start = '1'; Зануляем временные матрицы, и конечную матрицу; for i in 0 to 7 loop for j in 0 to 7 loop temp(i)(j) := 0.0; OutBlock(i)(j) := 0.0; Dout(i)(j) <= 0.0; end loop; end loop; Получаем временную матрицу temp; for i in 0 to 7 loop for j in 0 to 7 loop for k in 0 to 7 loop temp(i)(j) := temp(i)(j) + dct(i)(k) * Din(k)(j); end loop; end loop; end loop; Транспонируем матрицу temp; for i in 0 to 7 loop for j in 0 to 7 loop dctt(i)(j) := temp(j)(i); end loop; end loop; Получение временной матрицы OutBlock; for i in 0 to 7 loop for j in 0 to 7 loop for k in 0 to 7 loop OutBlock(i)(j) := OutBlock(i)(j) + dct(i)(k) * dctt(k)(j); end loop; end loop; end loop; Транспонируем матрицу OutBlock; for i in 0 to 7 loop for j in 0 to 7 loop OutAnother(i)(j) := OutBlock(j)(i); end loop; end loop; Выгружаем результат в выходную шину; for i in 0 to 7 loop for j in 0 to 7 loop wait until Clk = '1' and Clk'event; Done <= '0'; Dout(i)(j)<= OutAnother(i)(j); end loop; end loop; end process; end main; 3. Временные Диаграммы 3.1. Разработка временных диаграмм (ВД) и примеры ВД Рассмотрим несколько случаев с разными матрицами: Входная матрица равна:  На временной диаграмме мы можем наблюдать входную матрицу, и выходную матрицу. Так как в матрице 8 элеметнов, и они являются еще и вещесвтенными, программа показывает только 7 элеметнов, но если раскрыть подробнее, то отобразит все 8, как показано на примере последней строки выходной матрицы  Выходная матрица соответствует ожидаемой. заключение В ходе выполнения работы был реализован модуль, способный вычислять максимальное значение входной матрицы и выдавать на выходе матрицу состоящую из элементов равных максимальному значению. Код написан на VHDL в среде Active-HDL 9.1. Также был изучен теоретический материал по теме курсовой работы. И были получены практические навыки в написании кода и создании временных диаграмм. список использованных источников Математическое и программное обеспечение устройств с программируемой логикой. 2019 г. Фахми, Соколов https://www.kit-e.ru/articles/circuit/2009_03_134.php - лекции по схемотехнике https://link.springer.com/chapter/10.1007/978-3-642-21697-8_80 https://www.ijsr.net/archive/v4i7/SUB156248.pdf https://orenstudent.ru/DCT_2.htm http://promelchuvsu.ucoz.net/Design_DDonVHDL/operatory.pdf приложение А Исходный код library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.NUMERIC_STD.ALL; use ieee.std_logic_unsigned.all; use ieee.std_logic_arith.all; use work.add.all; entity main is port ( Clk : in std_logic; Start : in std_logic; Din : in matrixreal; Done : out std_logic; Dout : out matrixreal ); end main; architecture main of main is begin process variable i, j, k: INTEGER; variable OutBlock : matrixreal; variable temp : matrixreal; variable dct : matrixreal; variable dctt : matrixreal; variable OutAnother: matrixreal; begin dct := ( (0.354, 0.354, 0.354, 0.354, 0.354, 0.354, 0.354, 0.354), (0.490, 0.416, 0.278, 0.098, -0.098, -0.278, -0.416, -0.490), (0.462, 0.191, -0.191, -0.462, -0.462, -0.191, 0.191, 0.462), (0.416, -0.098, -0.490, -0.278, 0.278, 0.490, 0.098, -0.416), (0.354, -0.354, -0.354, -0.354, 0.354, -0.354, -0.354, 0.354), (0.278, -0.490, 0.098, 0.416, -0.416, -0.098, 0.490, -0.278), (0.191, 0.462, 0.462, -0.191, -0.191, 0.462, -0.462, 0.191), (0.098, 0.278, 0.416, -0.490, 0.490, -0.416, 0.278, -0.098)); wait until Start = '1'; Done <= '0'; for i in 0 to 7 loop for j in 0 to 7 loop temp(i)(j) := 0.0; OutBlock(i)(j) := 0.0; Dout(i)(j) <= 0.0; end loop; end loop; for i in 0 to 7 loop for j in 0 to 7 loop for k in 0 to 7 loop temp(i)(j) := temp(i)(j) + dct(i)(k) * Din(k)(j); end loop; end loop; end loop; for i in 0 to 7 loop for j in 0 to 7 loop dctt(i)(j) := temp(j)(i); end loop; end loop; for i in 0 to 7 loop for j in 0 to 7 loop for k in 0 to 7 loop OutBlock(i)(j) := OutBlock(i)(j) + dct(i)(k) * dctt(k)(j); end loop; end loop; end loop; for i in 0 to 7 loop for j in 0 to 7 loop OutAnother(i)(j) := OutBlock(j)(i); end loop; end loop; wait until Clk = '1' and Clk'event; Done <= '1'; for i in 0 to 7 loop for j in 0 to 7 loop wait until Clk = '1' and Clk'event; Done <= '0'; Dout(i)(j)<= OutAnother(i)(j); end loop; end loop; end process; end main; | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||