Микропроцессорные устройства. Лаба 1. Отчёт по ЛР1. Лабораторная работа 1 Исследование дешифратора и шифратора ст гр. Рм11 В. А. Дюсембаев Проверил Ю. В. Анохин

Скачать 251.5 Kb. Скачать 251.5 Kb.

|

|

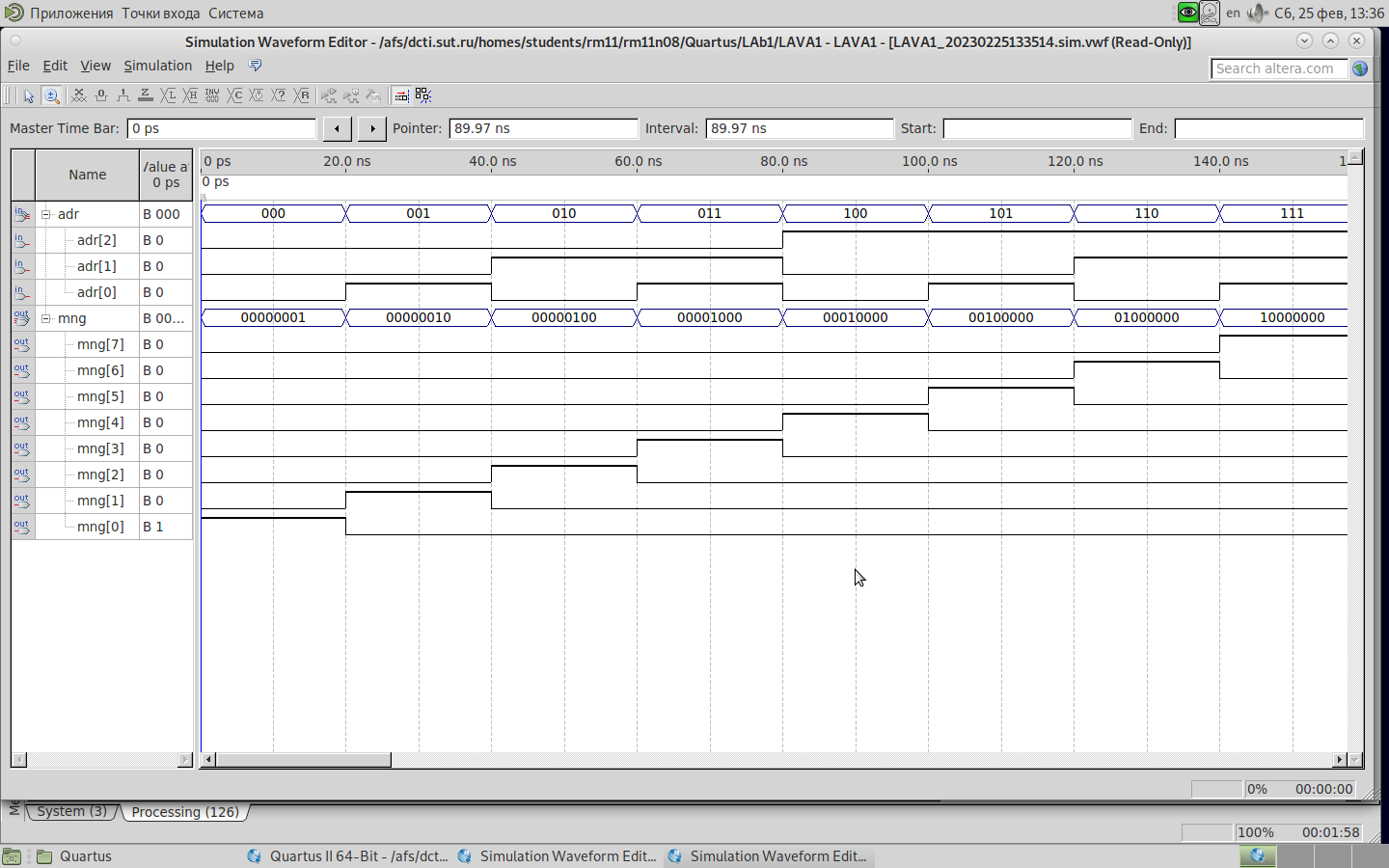

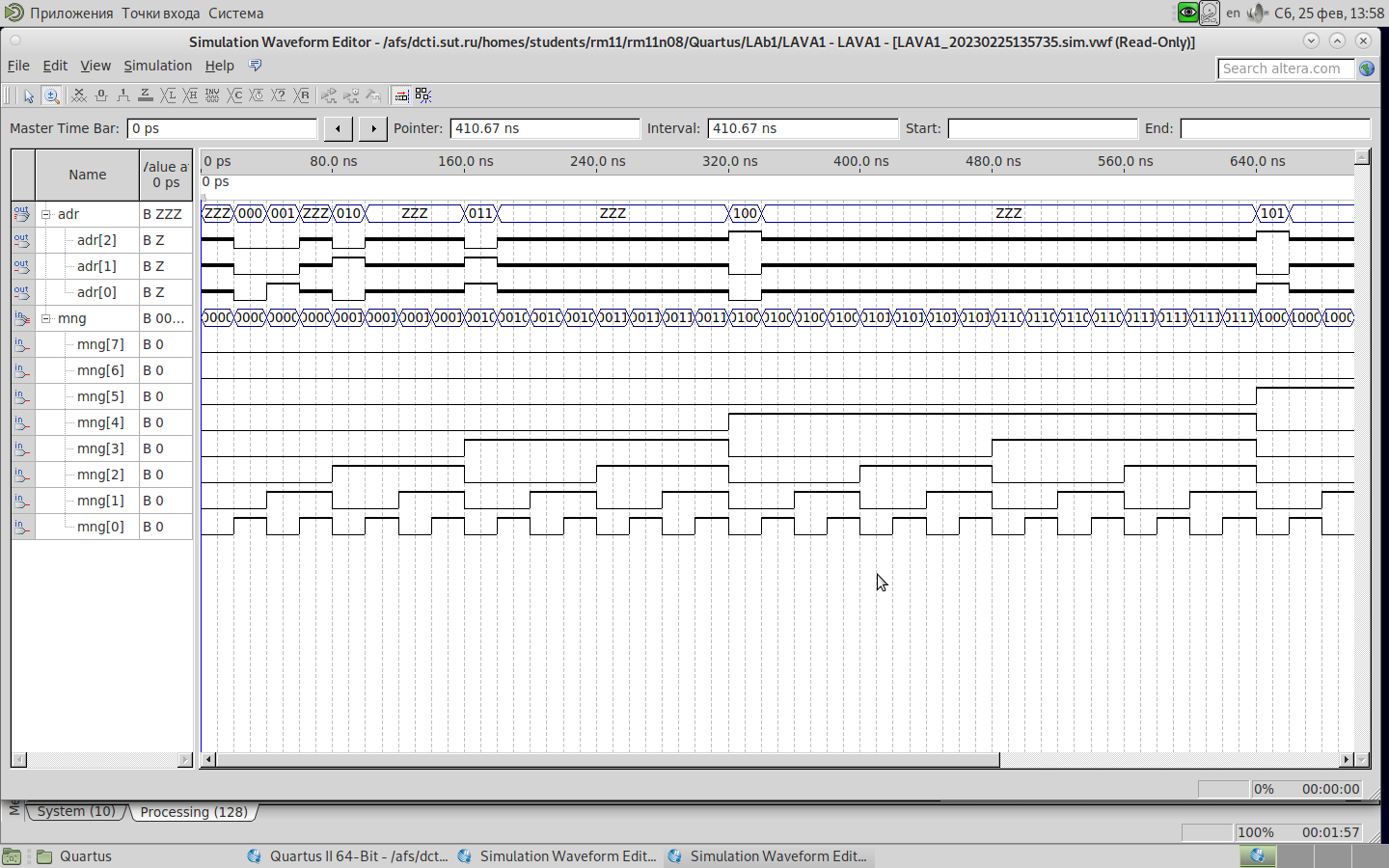

ФЕДЕРАЛЬНОЕ АГЕНТСТВО СВЯЗИ Федеральное государственное бюджетное образовательное учреждение высшего образования «Санкт-Петербургский государственный университет телекоммуникаций им. проф. М. А. Бонч-Бруевича» _____________________________________________________________________________ Кафедра программной инженерии и вычислительной техники Дисциплина «Микропроцессорные устройства» Лабораторная работа № 1Исследование дешифратора и шифратора Выполнил: ст. гр. РМ-11 В. А. Дюсембаев Проверил: Ю. В. Анохин _____________________ Санкт-Петербург 2023 Цель работы: 1) изучение функционирования простейшего КЦУ; 2) получение основных навыков проектирования схем в редакторе пакета Quartus15. Краткие сведения об исследуемых устройствах. В данной работе исследуются два устройства: дешифратор и шифратор. В схемах микропроцессорных устройств дешифратор применяется для получения сигнала управления на направлении, адрес которого указан на адресных входах в текущий момент времени. К входам шифратора подключаются управляющие линии, по которым поступают запросы от различных устройств. На выходах шифратора в момент прихода запроса устанавливается адрес подключенного устройства, пославшего запрос. По этому адресу подключается шина данных для обмена данными между микропроцессорной системой и подключенным устройством. Шифратор - устройство, определяющее адрес поступившего запроса. Программа__1.1_module_dec_(input_wire_[2:0]adr,_output_wire_[7:0]mng);_reg_[7:0]y;_assign_mng=y;'>Программа 1.1 module dec (input wire [2:0]adr, output wire [7:0]mng); reg [7:0]y; assign mng=y; always @(adr) begin case(adr) 3'b000: y=8'b00000001; 3'b001: y=8'b00000010; 3'b010: y=8'b00000100; 3'b011: y=8'b00001000; 3'b100: y=8'b00010000; 3'b101: y=8'b00100000; 3'b110: y=8'b01000000; 3'b111: y=8'b10000000; endcase; end endmodule  Программа 1.2 module cod (input wire [7:0]mng, output wire [2:0]adr); reg [2:0]cd; assign adr=cd; always @(mng) begin case(mng) 8'b00000001: cd=3'b000; 8'b00000010: cd=3'b001; 8'b00000100: cd=3'b010; 8'b00001000: cd=3'b011; 8'b00010000: cd=3'b100; 8'b00100000: cd=3'b101; 8'b01000000: cd=3'b110; 8'b10000000: cd=3'b111; default: cd=3'bzzz; endcase; end endmodule  Выводы: Осознали, что шифратор и дешифратор можно использовать, когда нужно передать большое количество данных, не используя большое количество проводов. Поняли, что код на выходе устройств зависит от кода на входе, так как шифратор и дешифратор не обладают памятью. На выходе дешифратора одновременно может находиться только один сигнал. На вход шифратора одновременно не может подаваться несколько сигналов иначе возникает неопределённость, что видно на временной диаграмме шифратора. |