Архитектура ЭВМ лабораторная работа 1. Лабораторная работа 1. Лабораторная работа 1 Ознакомление с работой мп кр580 и работой эмулятора emКР580

Скачать 2.87 Mb. Скачать 2.87 Mb.

|

Лабораторная работа 1Ознакомление с работой МП КР580 и работой эмулятора emКР580Тимиров И. Х. ст. гр. ЗИВТ-181 Цель работы: 1. Ознакомиться с руководством пользования эмулятором emКР580 (п. 1.1). 2. Изучить типовую структуру МП КР580, назначение выводов МП, струк-туру памяти МП-системы, форматы команд МП по вводному разделу практикума и по [1, 2, 3]. 3. Изучить работу программы Прогр. 1.1.  Рис. 1. Структурная схема МП КР580 Выводы микропроцессора имеют следующее назначение: Выводы C1 и C2 используются для ввода в микропроцессор синхросиг-налов от тактового генератора. Выводы ШД0 … ШД7 образуют двунаправленную шину данных для обмена данными между процессором и внешней памятью или внешними устройствами. Выводы ША0 … ША15 образуют шину адреса, которая используется процессором для вывода адреса ячейки памяти или адреса внешнего устройства, с которой(ым) будет проводиться обмен данными. Вывод СНХР (СИНХР) используется для синхронизации процессором внешних устройств. Вывод СБР – это аппаратный сброс микропроцессорной системы. Вывод ГТ используется процессором для приема сигналов от внешнего устройства или памяти о готовности его (ее) к обмену данными. Вывод ОЖ используется МП для формирования им сигналов внешнему устройству или памяти об ожидании готовности устройства (па-мяти) к обмену информацией между ним и процессором. Выводы ЧТ и ЗП используются процессором для формирования им сигналов чтения и записи для внешней памяти и устройств ввода/вывода. Выводы ЗПР и РПР – выводы для сигналов запроса и разрешения прерывания. Выводы ЗПДП и РПДП – выводы для сигналов запроса и разрешения прямого доступа к памяти.  На Рис. 2 показана структура памяти МП КР580  Рис. 3. Форматы 1-, 2-х и 3-хбайтных команд МП КР580. Система команд КР580.В Табл. – 11 приведена справочная информация о системе команд МП КР580, разбитая по подгруппам команд. Табл. 1. Однобайтные пересылки.

Табл. 2. Двухбайтные пересылки.

Табл. 3. Обмен байтами.

Табл. 4. Команды ввода и вывода.

Табл. 5. Арифметические и логические операции с одним операндом.

Табл. 6. Арифметические и логические операции с двумя операндами.

Табл. 7. Команды сдвига содержимого аккумулятора.

Табл. 8. Команды передачи управления

Табл. 9. Команды условной передачи управления.

Табл. 10. Команды вызова и возврата из подпрограммы.

Табл. 11. Специальные команды.

Коды команд МП КР580.В Табл. приведены условные обозначения типов операндов, а в Табл. информация для определения машинного кода любой команды процессора КР580. Табл. 12 Обозначения типов операндов.

Табл. 13. Перечень всех команд процессора с указанием кода каждой команды.

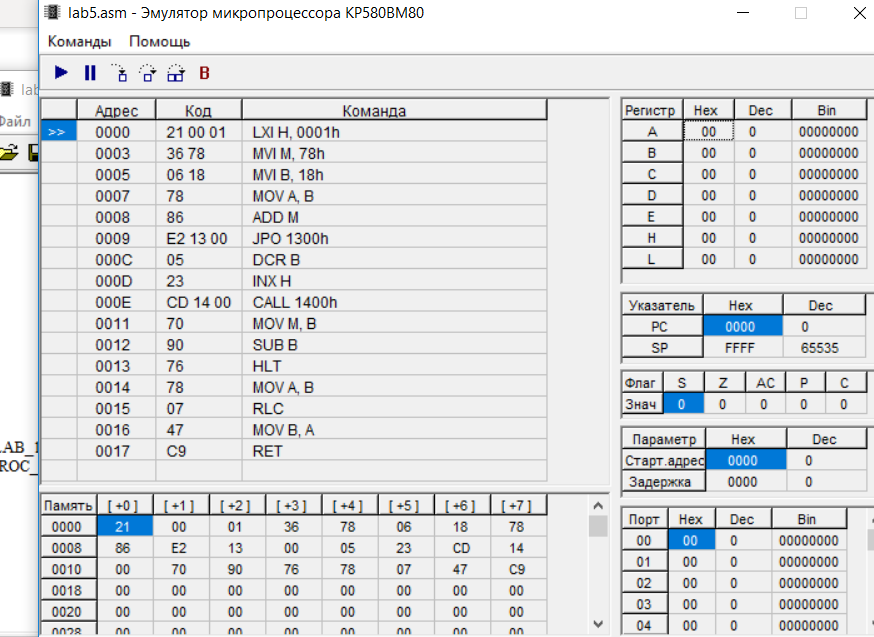

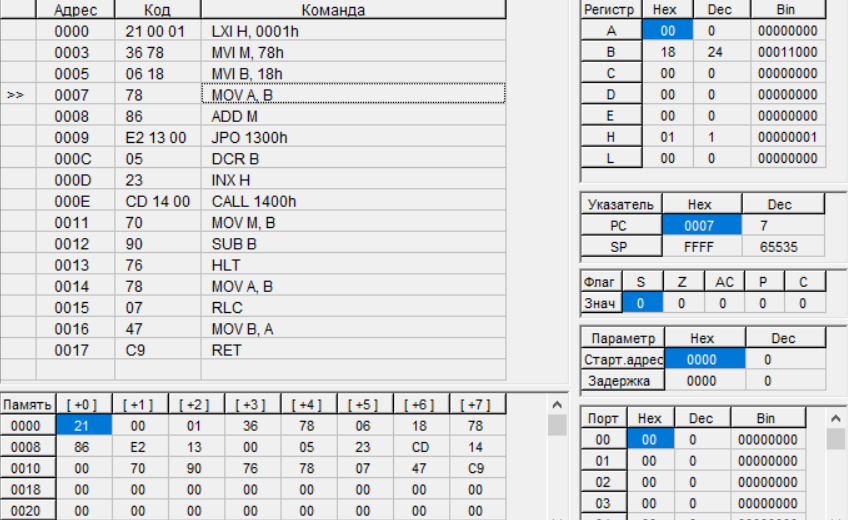

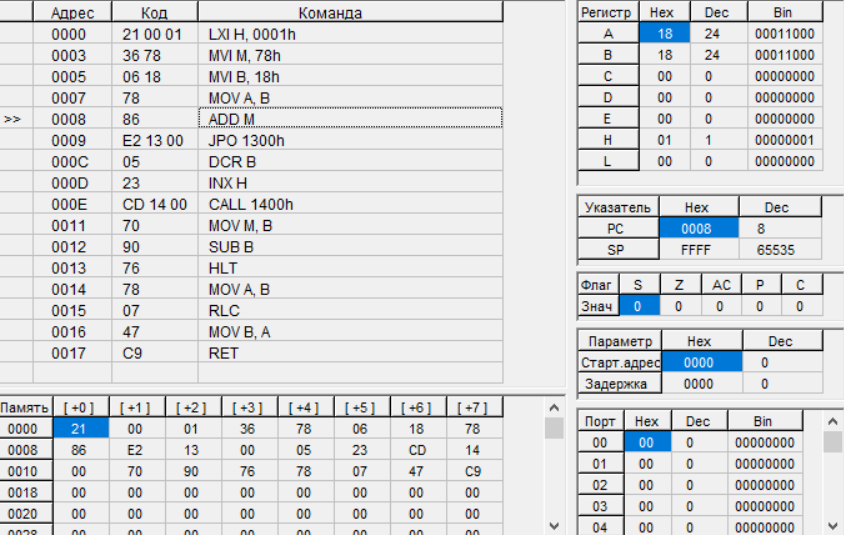

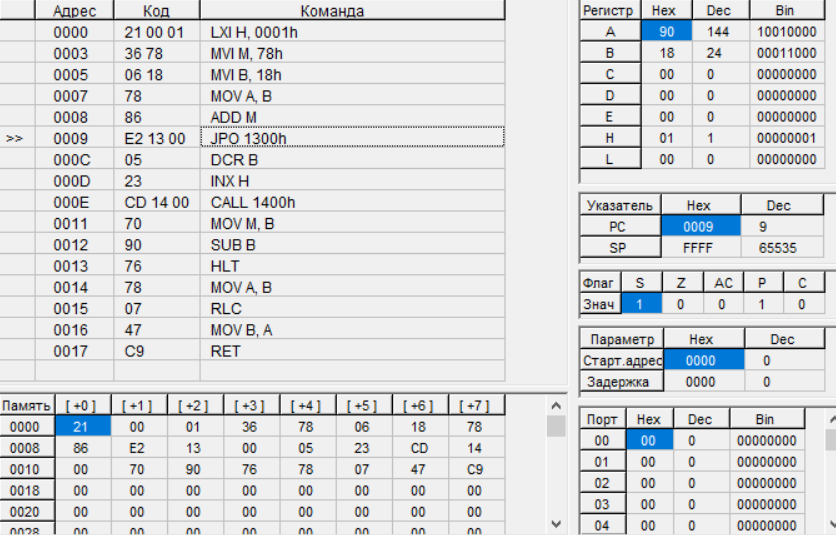

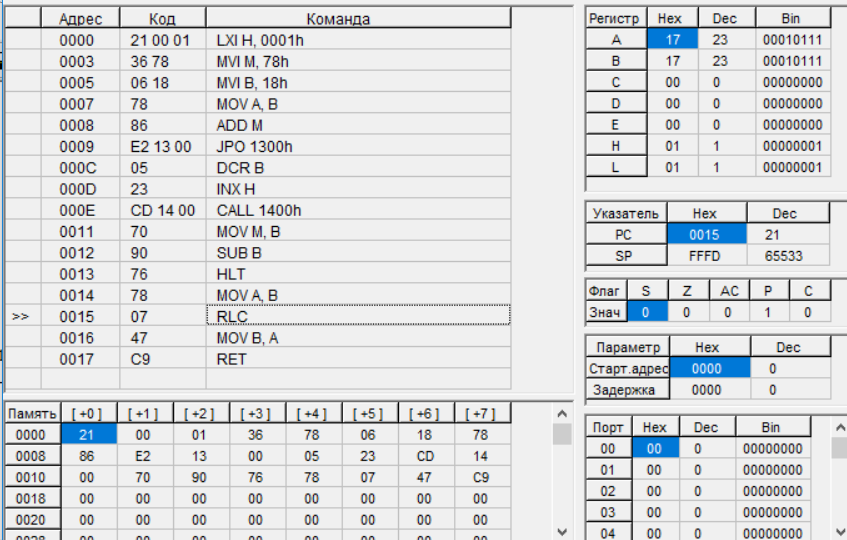

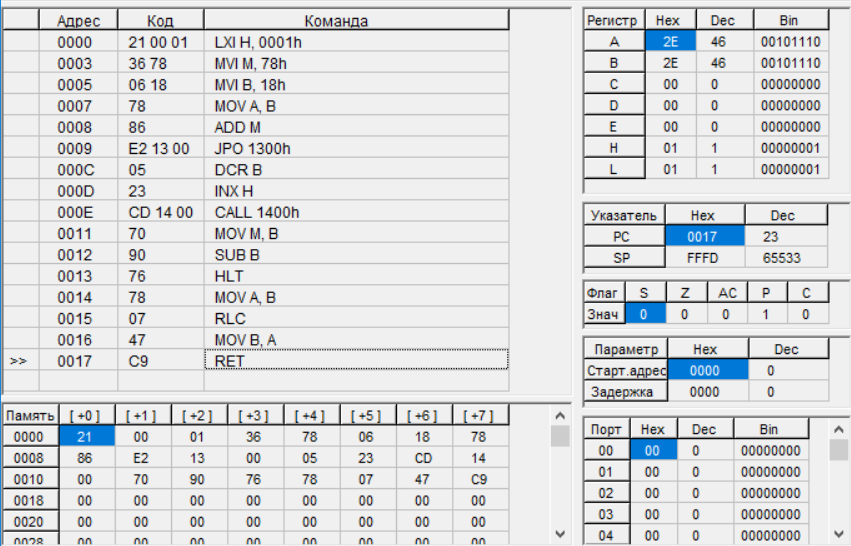

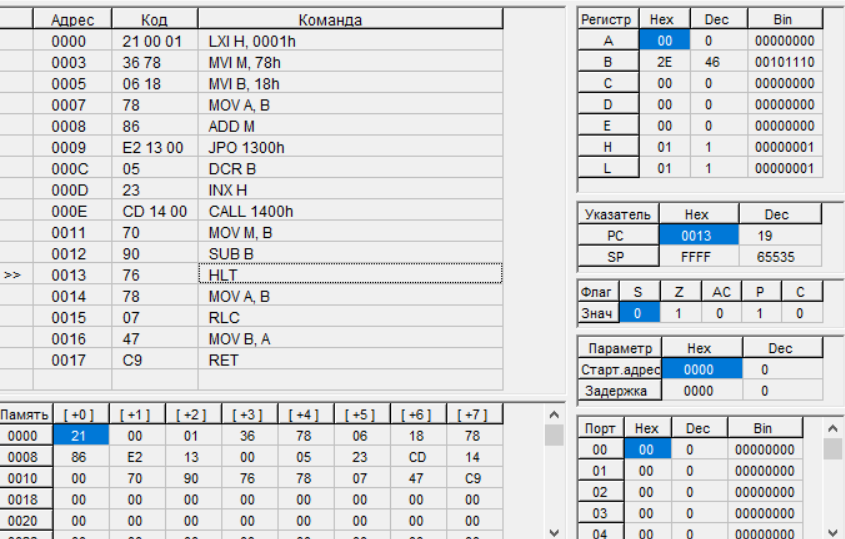

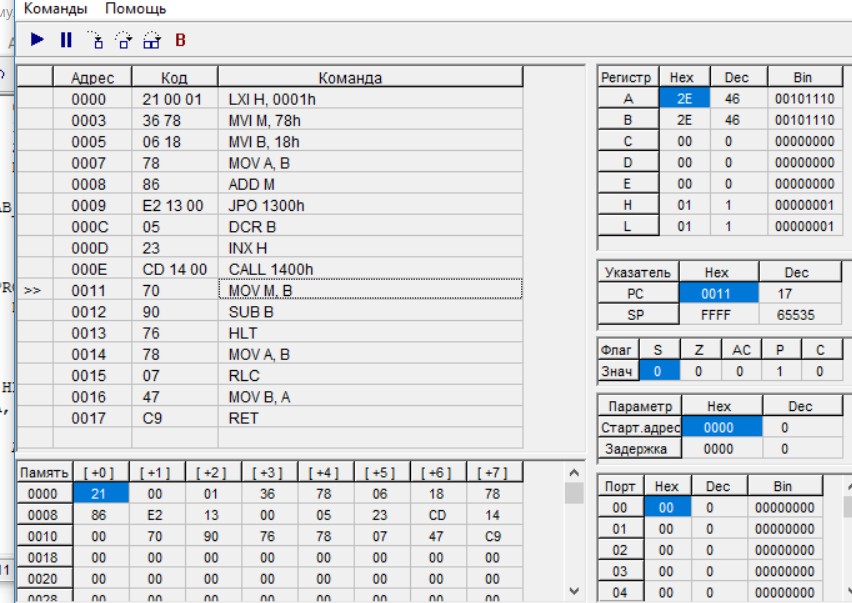

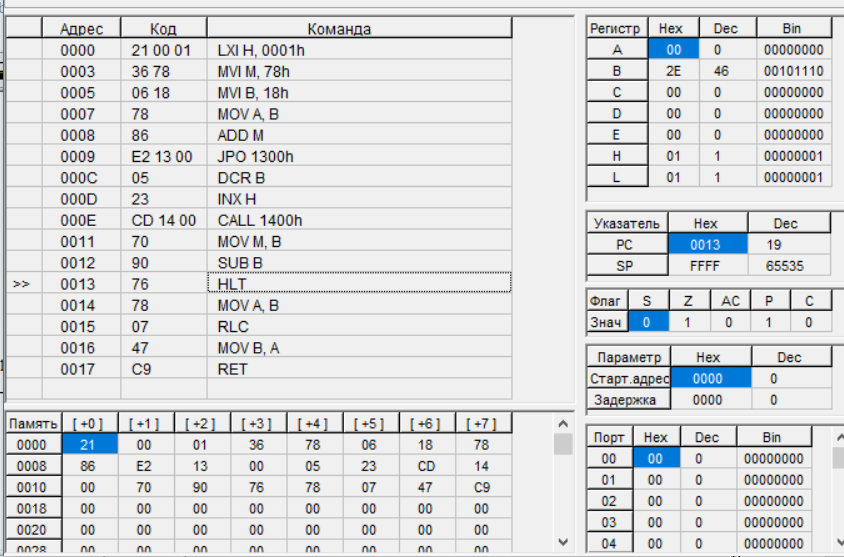

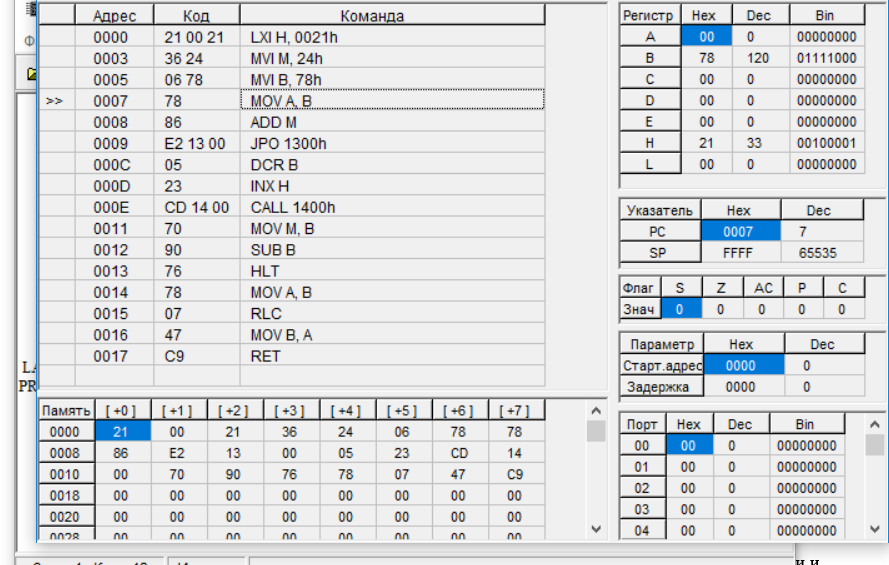

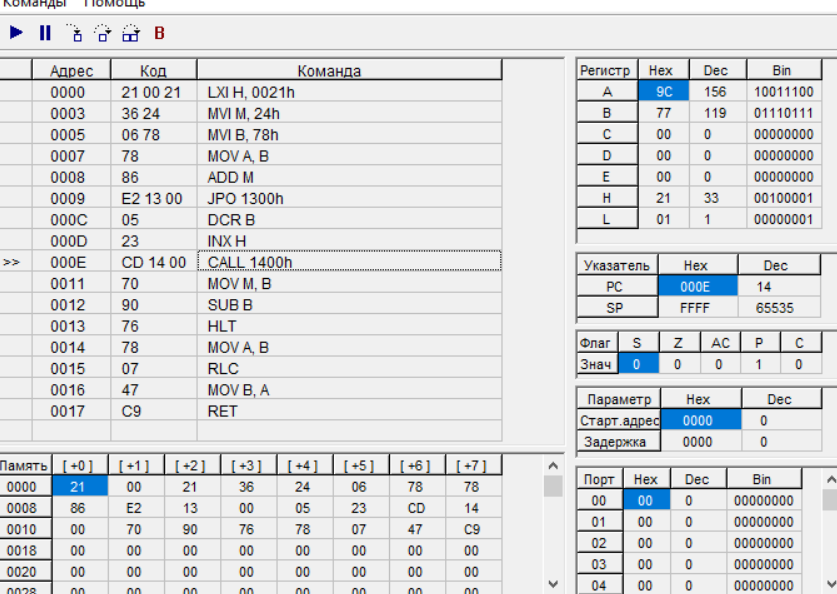

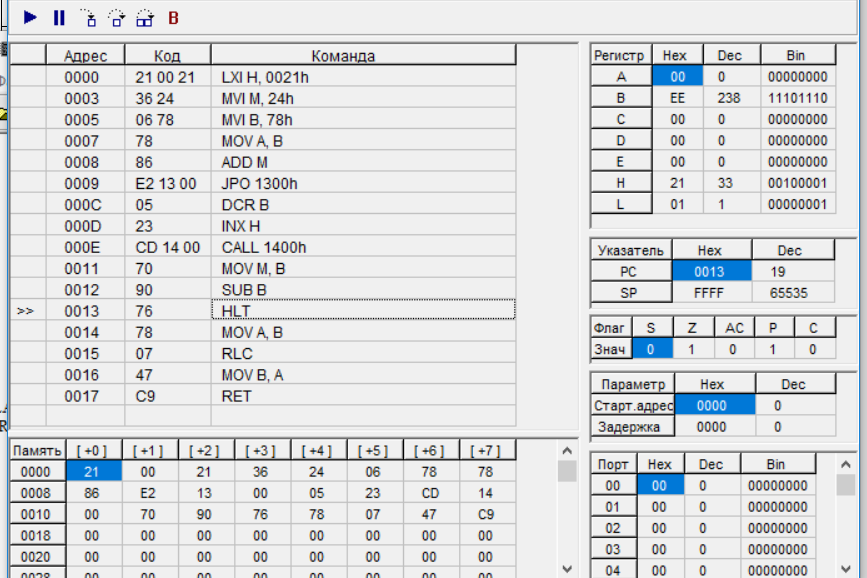

Меню эмулятора содержит следующие пункты: Команды. Список всех команд вызываемых при просмотре или отладки работы программы. Выполнить до курсора. Выполнение программы до выделенной строки в поле команд (F4). Выполнить одну команду. Выполнение одной команды программы (F7). Выполнить процедуру. Выполнение одной команды, не заходя в процедуры (F8). Процедурами считаются команды условного и безусловного перехода к подпрограммам, а также команды обработки прерываний. Запустить программу. Запуск программы до ее завершения (F9). Прервать. Остановка выполнения программы (Esc) при запуске ее до завершения. Это единственное действие, которое доступно во время отработки команд программы, оно позволяет в любой момент прерват выполнение программы процессором. При остановке выполнения программы курсор команды будет показывать на следующую выполняемую команду. Установить точку. Установка точки останова в выделенной строке в поле команд (Ctrl + F8). При этом возможно установление только одной точки останова. Установка точки останова в строке, где она уже установлена, приведет к удалению из этой строки точки останова. Если точка останова устанавливается в другой строке, то предыдущая точка удаляется. Выход. Выход из эмулятора в текстовый редактор (Alt + x, Alt + F4). Ход работы В программе emKP580 был написан код на языке Assambler:  После сохранения и ассемблирования я перешла в программе в режим эмулирования:  Анализ программы в режиме пошагового выполнения:  Произошла адресация содержимого регистра (В) в Аккумулятор.  Сложение (А) с байтов в ячейке, расположенной по адресу в паре регистров В, L.  Флаг (P) установлен на 1, поэтому программа не переходит по метке LAB_1. После происходит декрементация (В) и инкрементация пары регистров (Н, L) и переход в подпрограмму PROC_1:  В подпрограмме PROC_1 происходит сдвиг значения (А) влево и запись результата в регистр (В). После чего подпрограмма закрывается и продолжается работа основной программы:  Следующий шаг заключается в записи содержимого регистра (В) в ячейку по адресу пары регистров (H, L) и из (А) вычетается байт в регистр (В), а результат заносится в (А):  В результате чего флаг (Z) устанавливается на единицу. Анализ программы в режиме одного приёма:  Результаты совпадают с пошаговым выполнением программы. Анализ программы в пошаговом режиме без захода в подпрограмму: Все шаги до вызова подпрограммы PROC_1 идентичны:  Результат выполнения программы такой же, как и в уже рассмотренных режимах:  Результат работы программы при изменении адреса ячейки и вводимых данных в первых трёх строках кода:   Перед вызовом подпрограммы PROC_1:  После вызова подпрограммы:  Конечный результат выполнения программы:  Вывод Ознакомилась с МП KP580 и его работой, а также работой эмулятора emKP580, который представляет программу, имитирующую все основные действия, выполняемые МП при обработке им определённого кода. Также узнала о командах МП и его архитектуре. Анализировала работу программы, написанную на языке Ассемблер в трёх режимах. Помимо этого, проанализировала работу программы с изменёнными числовыми значениями адреса и данных. 1 | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||