Лабораторная работа 14 Исследование интегральных элементов типа ттл

Скачать 449.76 Kb. Скачать 449.76 Kb.

|

|

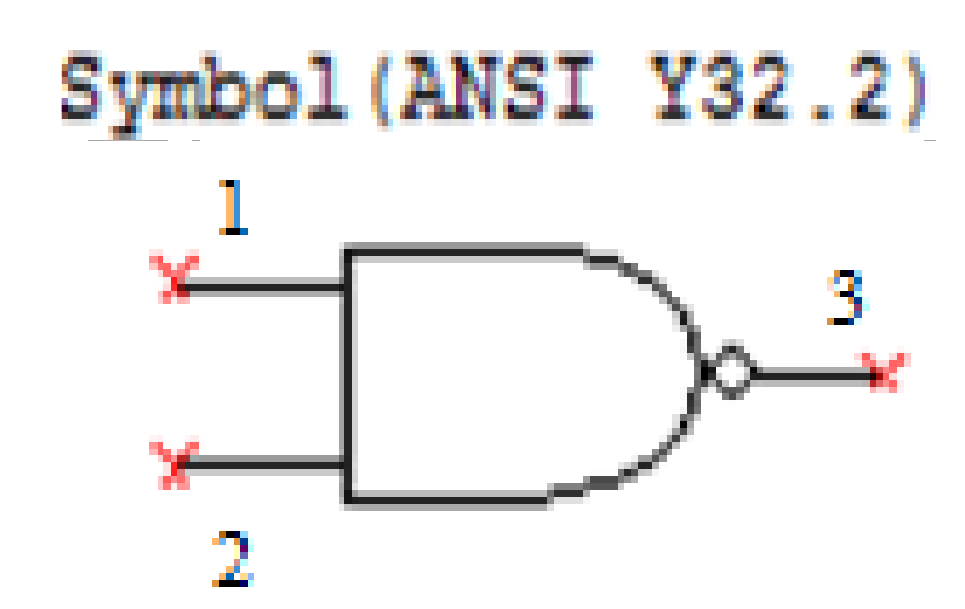

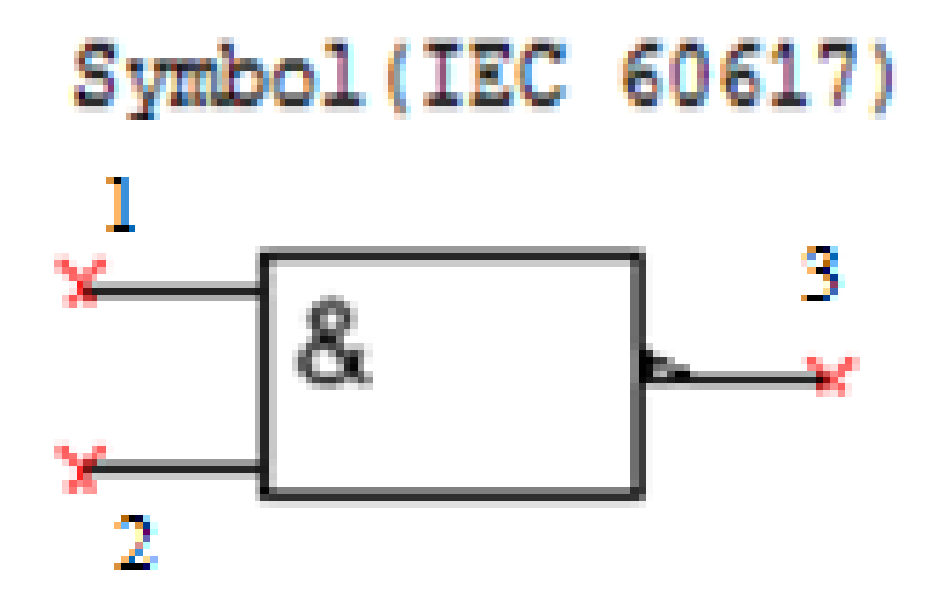

ЛАБОРАТОРНАЯ РАБОТА № 14 Исследование интегральных элементов типа ТТЛ Цель работы: исследование основных характеристик и параметров интегральных элементов транзисторно-транзисторной логики (ТТЛ) 1. Теоретические сведения Логические элементы вместе с запоминающими элементами составляют основу устройств цифровой обработки. Логические элементы выполняют простейшие логические операции над цифровой информацией. В настоящее время в радиоэлектронной аппаратуре, вычислительных устройствах, устройствах автоматики, измерительных приборах широко применяются микросхемы транзисторно-транзисторной логики ТТЛ различных серий. Серия микросхем – это совокупность микросхем, характеризуемых общими технологическими и схемотехническими решениями, а также уровнями электрических сигналов и напряжения питания. Каждая серия микросхем характеризуется некоторым набором параметров, дающих достаточно подробное представление об этой серии. При определении этих параметров ориентируются именно на логические элементы - простейшие устройства серии микросхем. В соответствии с этим говорят о параметрах не серии микросхем, а о параметрах логических элементов данной серии. Новые технологии позволяют размещать на кристалле все больше и больше транзисторов. Это привело к распространению новых средств для построения цифровых устройств – микросхем высокой степени интеграции и программируемой пользователем структурой. Однако, практически всегда возникает потребность в реализации одиночных логических функций или преобразовании уровней сигнала или буферизации линий интерфейса. Для удовлетворения таких потребностей появились одновентильные логические схемы, в которых в одном корпусе размещается один логический элемент. Обычно такие микросхемы изготавливаются в сверхминиатюрных корпусах с поверхностным монтажом (например, логические микросхемы И-НЕ и ИЛИ-НЕ).

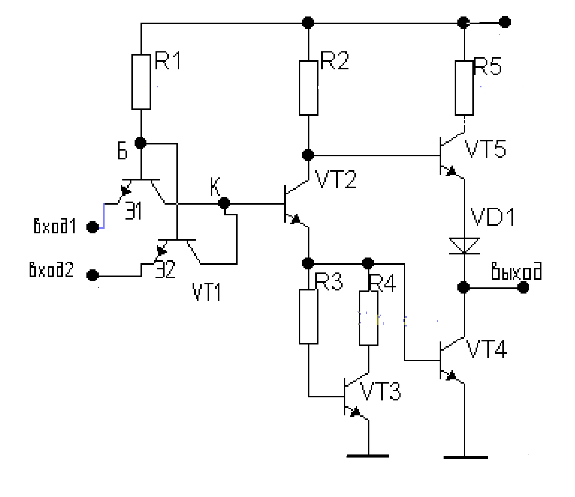

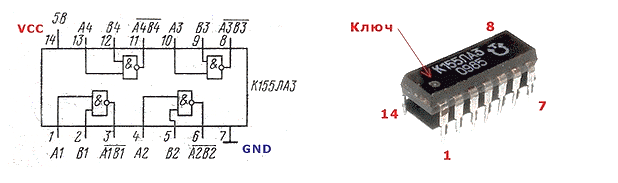

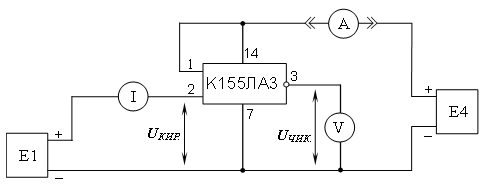

Логическая операция И реализуется с помощью двухэмиттерного транзистора VT1 и резистора R1, а операция НЕ – на оставшихся транзисторах VT2-VT5, диоде VD1 и резисторах R2…R5, на которых построен сложный инвертор. Рассмотрим особенности работы такого ключа. Если хотя бы на одном из входов схемы имеется низкий уровень напряжения (логический ноль), то соответствующий эмиттерный переход многоэмиттерного транзистора VT1 откроется. Поскольку в этой ситуации втекающий в коллектор транзистора VT1 ток ограничен на уровне Iко транзистора VT2, то многоэмиттерный транзистор VT1 насыщается и его остаточное напряжение Uк.э.н1 составляет при этом не более 0,3В. Потенциал базы VT2, равный Uºвх +Uк.э.н1 , недостаточен для открывания двух последовательно включенных эмиттерных переходов транзисторов VT2 и VT5 , а вместе с ними заперт и транзистор VT3. В свою очередь, транзистор VT4 и диодVD1 открыты за счет подключения базы VT4 через резисторR2 к положительному полюсу источника питания. При этом на выходе схемы возникает высокий уровень напряжения Vвых=Еn-Iб4R2-Uбэ4-Uак1, достигающий значения 3,6…4,2 В (на открытом эмиттерном переходе транзистора падает напряжение от 0,65 до 0,75 В, а ток в цепи базы VT4 незначителен).   a) б) Рис. 14.2. Микросхема К155ЛА3: а) внешний вид, б) цоколевка К числу основных характеристик ключей относятся: – передаточная – зависимость напряжения на выходе схемы от напряжения на входе Uвых=f1(Uвх) (рис. 14.3); – входная – зависимость входного тока ключа от входного напряжения Iвх=f2(Uвх) (рис. 14.4); – выходная – зависимость выходного напряжения от нагрузочного тока Uвых=f3(Iвых) (обычно снимают две выходные характеристики, соответствующие единичному и нулевому состояниям ключа).

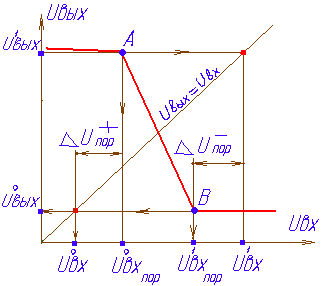

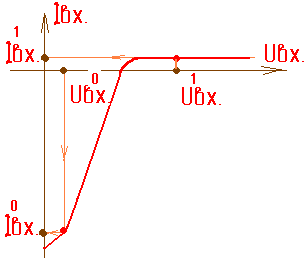

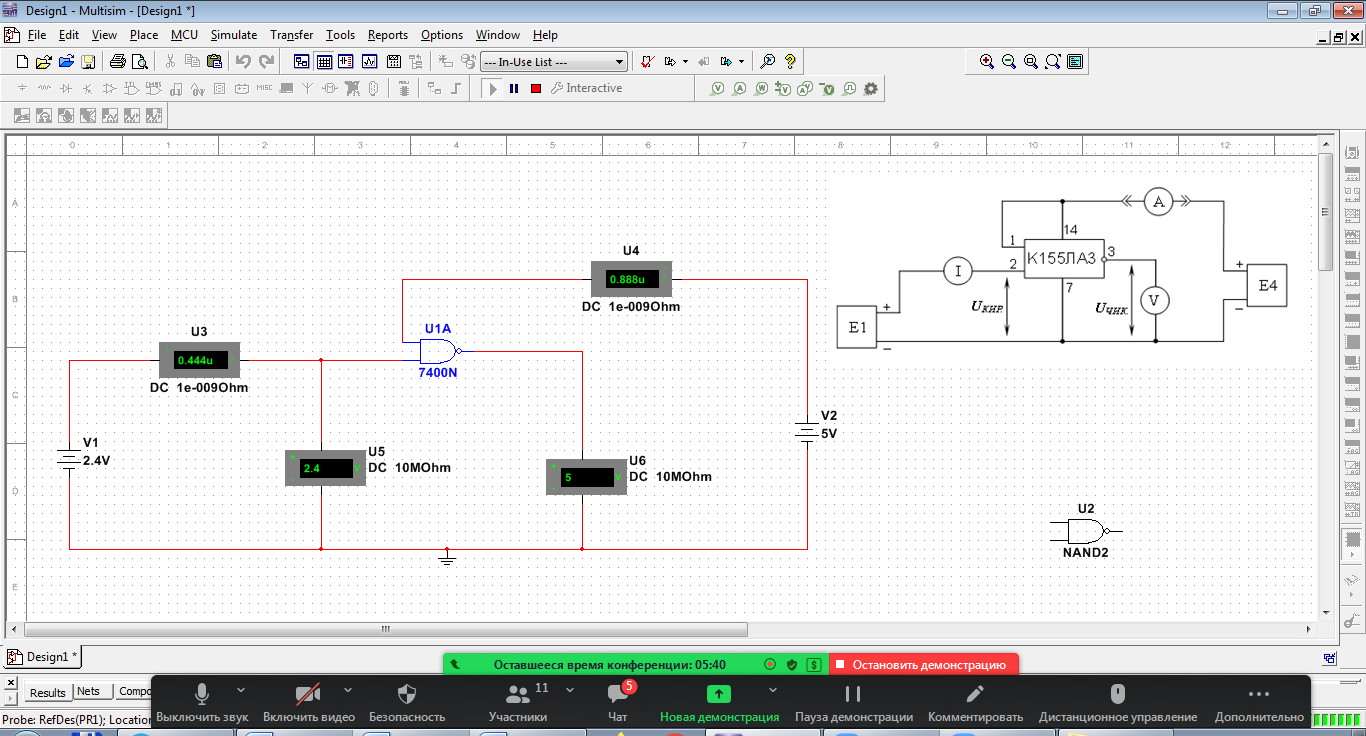

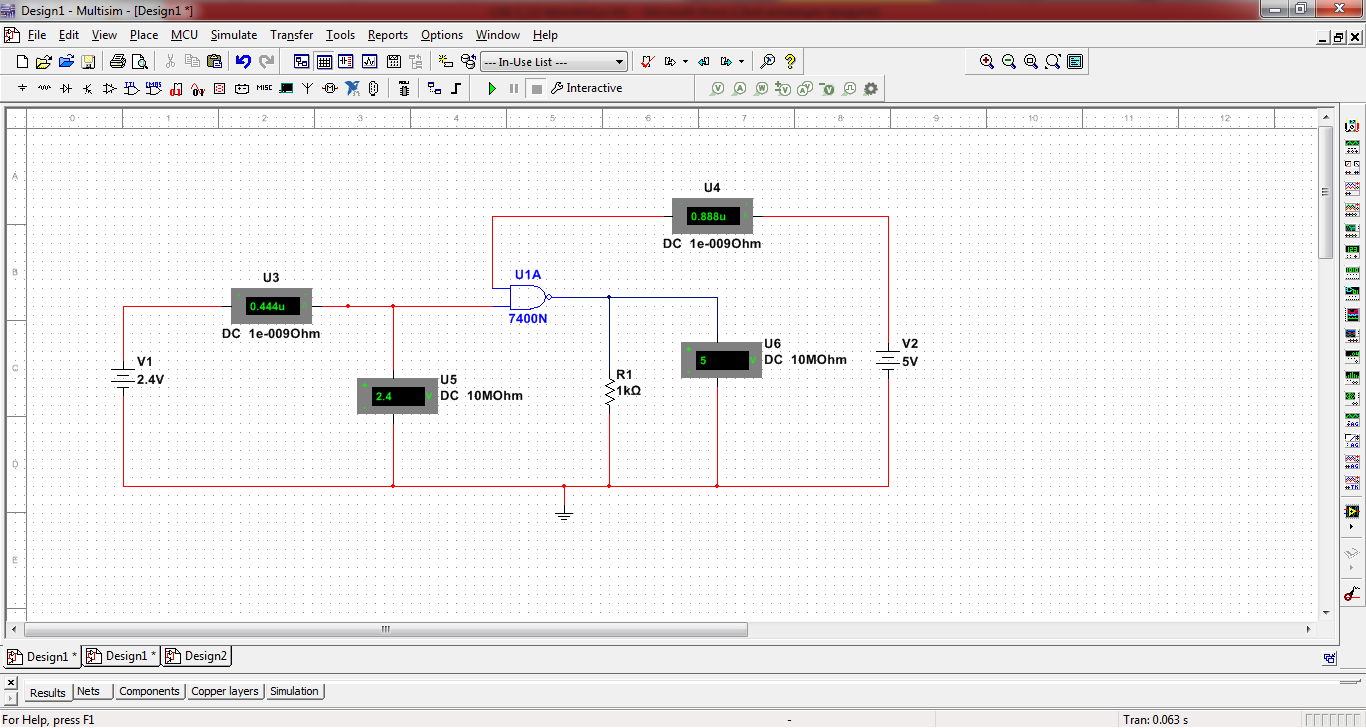

Последовательность обработки передаточной характеристикй сводится к следующим действиям. На передаточной характеристике намечаются точки А и В, в которых касательные к графику идут под углом 45, т.е. где dUвых/dUвх = 1 и эти точки проектируются с использованием нанесенной на график линии равного усиления Uвых=Uвх на оси абсцисс и ординат. В результате выполнения операции будут определены: – U¹ и Uº - соответственно напряжения логической единицы и логического ноля, т. е. значения высокого и низкого уровней напряжения. Эти напряжения могут быть отнесены ко входной или выходной цепям ключа и поэтому получают соответствующие дополнительные индексы в обозначении (U¹вх , Uºвх , U¹вых , Uºвых); – U¹пор иUºпор – пороговые напряжения логической единицы и логического нуля, т.е. наименьшее (наибльшее) значение высокого (низкого) напряжения на входе ключа, при котором он начинает изменять свое состояние. На рис. 14.3 смена состояния ключа происходит на участке между точками А и В. Найденные уровни напряжения позволяют оценить логический перепад ∆Uвых = U¹вых-Uºвых, положительную ∆U⁺n=Uºвх.пор-Uºвх и отрицательную ∆U⁻n=U¹вх-U¹вх.пор статические помехи, а также статическую помехоустойчивость ключа Un.ст как меньшую из двух получаемых величин ∆U⁺nи ∆U⁻n. Здесь Un.ст определяется на входе схемы как максимально допустимое отклонение напряжения, при котором ещё не происходит изменения уровней выходного напряжения ключа. Легко показать, что ключи, у которых нет петли гистерезиса на передаточной характеристике, могут иметь статическую помехоустойчивость не более половины логического перепада. Поэтому по степени отклонения от единицы отношения статической помехоустойчивости к половине логического перепада можно судить о качестве спроектированной схемы. При снятии входной характеристики на один из входов подают изменяющееся напряжение в пределах 0…Еn и наблюдают в его цепи ток. При этом все остальные входы объединяют и присоединяют к источнику с уровнем напряжения, соответствующим логической единице (нулю). Выходная цепь исследуемого элемента при этом остается ненагруженной Пользуясь входной характеристикой схемы, можно отыскать такие параметры ключа, как I¹вх иIºвх - входные токи логической единицы и нуля, т. е. токи во входной цепи ключа при подаче на его вход напряжения логической единицы U¹вх и нуля Uºвх. Примерный вид входных характеристик ТТЛ- и ЭСЛ-ключей и способ оценки параметров I¹вх иIºвх приводятся на рис. 14.4 При снятии выходной характеристики ключа в его входной цепи создают комбинацию входных сигналов, переводящую исследуемый ключ в состояние логического нуля или логической единицы. Выходную цепь ключа присоединяют к источнику тока и, изменяя нагрузочный ток, регистрируют изменения выходного напряжения. Быстродействие микросхемы определяется через среднее время задержки распространения сигнала:  , ,где t0,1зади t1,0зад – соответственно среднее время задержки по переднему и заднему фронтам импульса, измереннон на уровне 0.5 амплитуды импульса. Среднюю потребляемую микросхемой мощность можно определить с помощью следующей формулы:  2. Задание к выполнению лабораторной работы 2.1. Измерение входной и передаточной характеристик. 2.1.1. Для исследования характеристик микросхемы К155ЛА3 собрать схему, приведенную на рис. 14.5 (можно выбрать любой из четырех логических элементов 2И-НЕ).  Рис.14.5. Схема исследования К одному из входов выбранного для исследования ЛЭ 2 И-НЕ подключить источник Е1, к другому входу “+” источника питания (Е4). Устанавливая значения напряжени я источника Е1 от 0 до 5 В с шагом 0.5 В(ишлатилмаяпганига) эса манбанинг “+” қутбини уланг. Е1 кириш кучланишини 0...5 В, произвести измерения IВХ=f(UВХ) и UВЫХ=f(UВХ) Результаты исследования ззанести в табл. 14.1 Таблица14.1

2.1.2. В Измерить значения токов I0ИСТи I1ИСТ при UВХ=U0 ≈ 0,4 В и UВХ=U1 2,4 В (значения U0 и U1 приводятся в паспортных данных ИМС). 2.2. Исследование нагрузочной характеристики ИМС. Используя схему на рис. 14.5, . с помощью источника Е1 установить напряжение UВХ=0,4 В, соответствующее значению логического 0. Поочередно подключая на выход сопротивления RН=56 кОм,10 кОм, 1 кОм, 470 Ом, 100 Ом, измерить значения выходного напряжения и снять нагрузочную характеристику UВЫХ=f(RН). Результаты измерения занести в табл. 14.2. Таблица 14.2

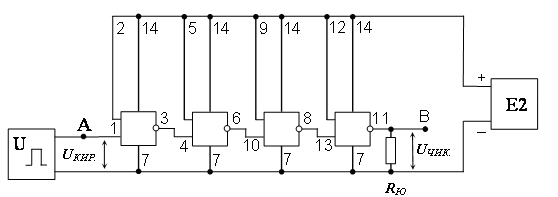

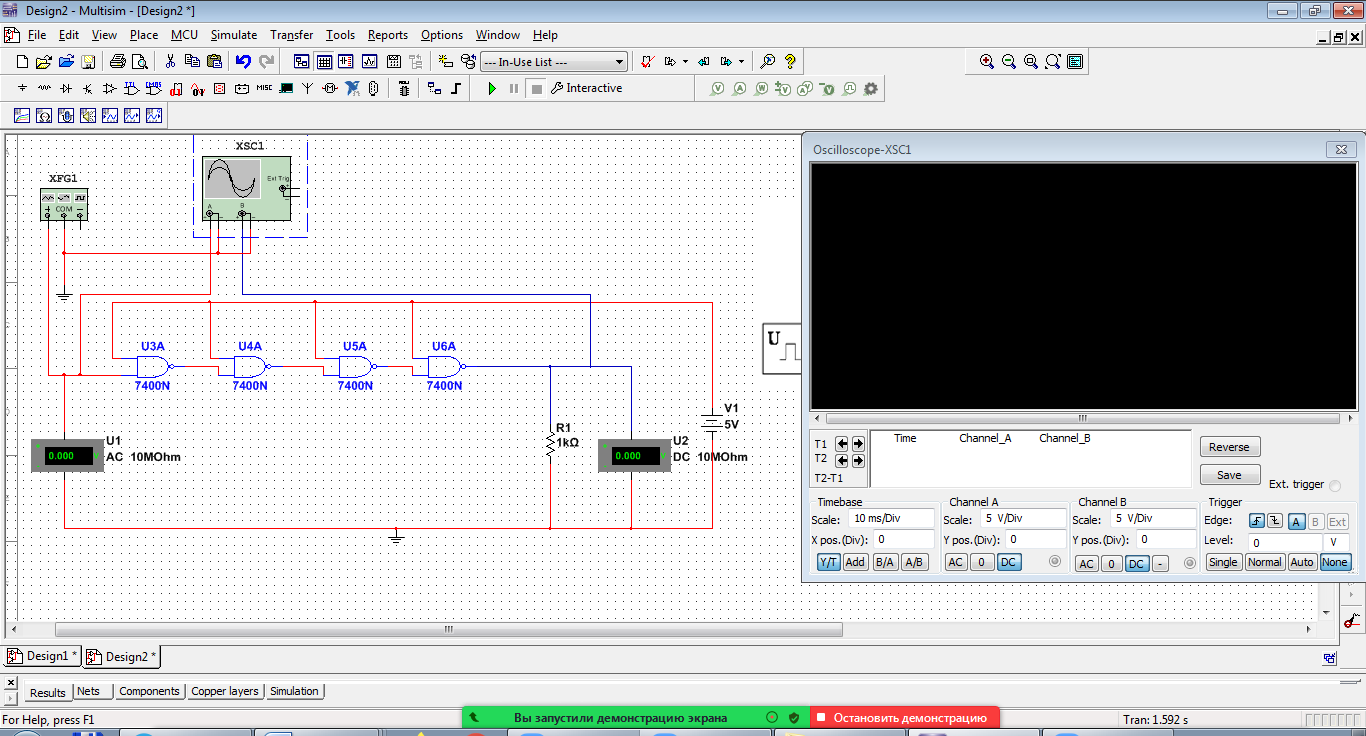

2.3. Исследование быстродействия ИМС. Собрать схему, приведенную на рис. 12.6. Для облегчения исследования и увеличения времени задержки, последовательно соединить 4 микросхемы. (Полученный результат необходимо разделить на 4).  Рис. 12.6 . Схема исселедования Подключить осцилограф между входом (точка А) и выходом (точка В). На выходе схемы (рис. 12.6) осцилограф необходимо подключается через делитель напряжения 1:10, что позволяет уменьшить влияние емкости соединительных проводов осцилографа. (Из-за низкого сопротивления делитель во входной цепи не требуется). Подать на вход последовательность прямоугольных импульсов амплитудой 5 В и частотой 1 кГц. Определить время задерзжи по переднему и заднему фронтам импульса.(t0,1зад , t1,0зад). 3. Обработка результатов исследования. 3.1. Построить графики зависимостей UВЫХ=f(UВХ) ва IВХ=f(UВХ) по результатам исследования в п. 2.1. Определить основные параметры: U0, U1, I0ВХ, I1ВХ, UМ+, UМ-, UМ.. Ўртача истеъмол қувватини РСР ҳисобланг. 3.2. Определить среднее время задержки распространения tзад ср ҳамда қайта уланиш ишини Аул ҳисоблаб топинг. 3.3. Построить график зависимости U1ВЫХ=f(RН) по результатам исследования в п. 2.2. По графику определить значение RН..min, соответствующее паспортному значению U1ВЫХ=2,4 В. Содержание отчета - паспортные данные и принципиальная схема микросхемы К155ЛА3; - таблицы с результатами исследований и графики зависимостей; - выводы по значениям параметров исследуемой ИМС. Контрольные вопросы 1. С какой целью в схемах ТТЛ применяется сложный инвертор? 2. Достоинства и недостатки схем ТТЛ? 3. схема с тремя устойчивыми состояниями ? 4. Функции шунтирующих диодов в выходных каскадах ИМС? NI Multisim дастурий муҳитида схемаларни йиғиш  1-sxema  2-sxema  3-sxema | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||