Лабораторная работа 2 итог. Лабораторная работа 2 Исследование комбинационных схем. Цель работы

Скачать 1.18 Mb. Скачать 1.18 Mb.

|

|

Лабораторная работа №2 Исследование комбинационных схем. Цель работы: Изучение принципов действия типовых комбинационных схем: дешифраторов, шифраторов, мультиплексоров, демультиплексоров. 1. Краткие теоретические сведения. Любая логическая схема без памяти полностью описывается таблицей истинности. Эта таблица является исходной информацией для синтеза схемы на основе логических элементов «И», «ИЛИ», «НЕ». Для разработки требуемого цифрового устройства сначала на основе таблицы истинности записывают его логическое выражение. Затем с целью упрощения цифрового устройства минимизируют его логическое выражение и далее разрабатывают схему, реализующую полученное логическое выражение. Логические выражения можно получить двумя способами: - на основе совершенной дизъюнктивной нормальной формы (СДНФ); - на основе совершенной конъюнктивной нормальной формы (СКНФ). Совершенная дизъюнктивная нормальная форма (СДНФ) Функция представляется суммой групп. Каждая группа состоит из произведения, в которую входят все переменные. Например:  Совершенная конъюнктивная нормальная форма (СКНФ) Функция представляется произведением групп. Каждая группа состоит из суммы, в которую входят все переменные. Например:  Если схема имеет несколько выходов, то каждый выход описывается своей функцией. Такая система функций называется системой собственных функций. СДНФ составляется на основе таблицы истинности по следующему правилу: для каждого набора переменных, при котором функция равна 1, записывается произведение, в котором с отрицанием берутся переменные, имеющие значение «0». Пример: Таблица 1.1 – Заданная таблица истинности

СДНФ:  СКНФ составляется на основе таблицы истинности по правилу: для каждого набора переменных, при котором функция равна 0, записывается сумма, в которой с отрицанием берутся переменные, имеющие значение 1. Таблица 1.2 – Заданная таблица истинности

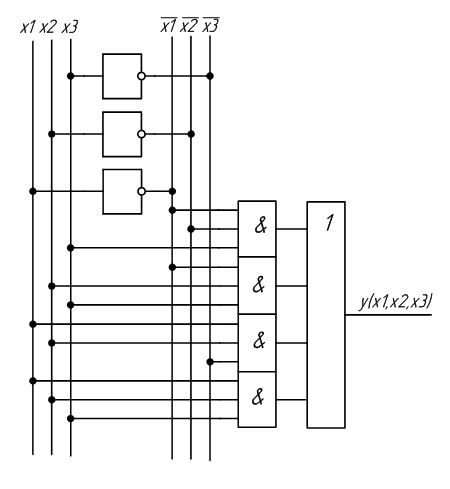

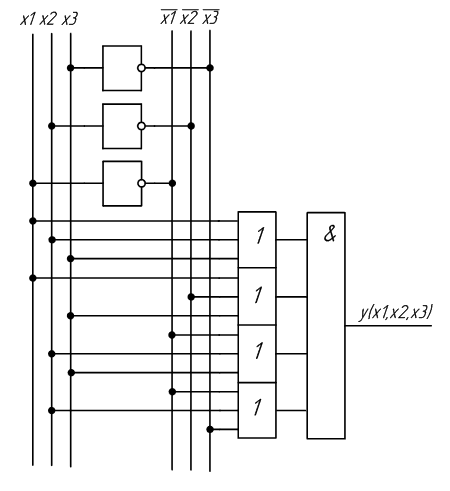

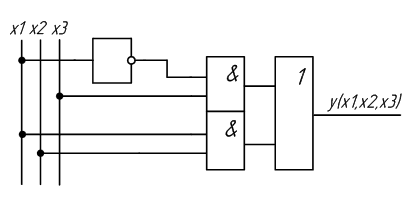

СКНФ:  На основе полученных выражений можно составить схему устройства, реализующего заданную функцию. Схема устройства, полученная на основе СДНФ, изображена (рис.1), а на основе СКНФ (рис.2).  Рис.1 – схема устройства, полученная на основе СДНФ  Рис. 2 – схема устройства, полученная на основе СКНФ С целью упрощения цифрового устройства применяют минимизацию функций. Используя законы алгебры логики можно упростить исходную функцию.  На основе полученного выражения составим новую схему устройства (рис.3).  Рис. 3 – Схема устройства, полученная после минимизации логической функции 2. Типовые комбинационные схемы. 2.1 Дешифратор (декодер) Дешифратор (декодер) служит для преобразования n-разрядного позиционного двоичного кода в единичный выходной сигнал на одном из 2n выходов. При каждой входной комбинации сигналов на одном из выходов появляется 1 . Таким образом, по единичному сигналу на одном из выходов можно судить о входной кодовой комбинации. Таблица истинности для декодера с двумя входами изображена в таблице 2.1. Таблица 2.1 – Таблица истинности двухразрядного дешифратора

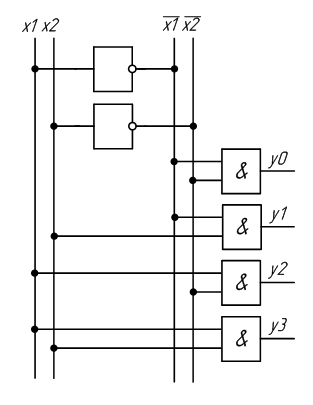

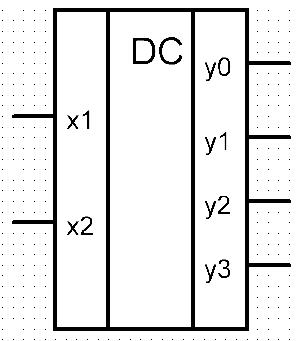

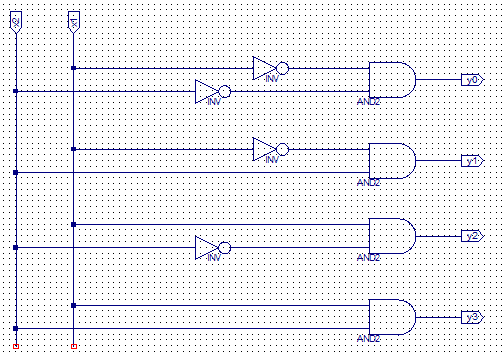

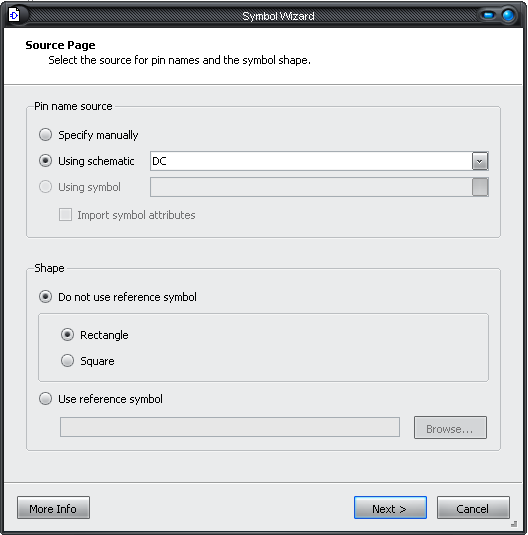

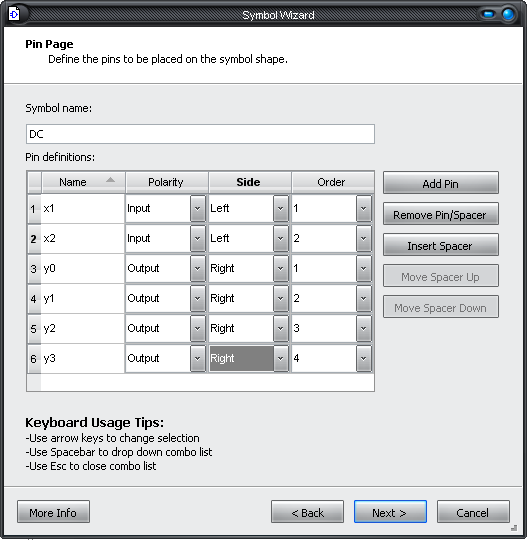

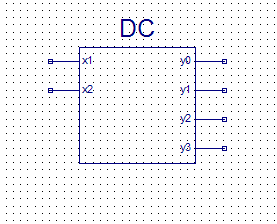

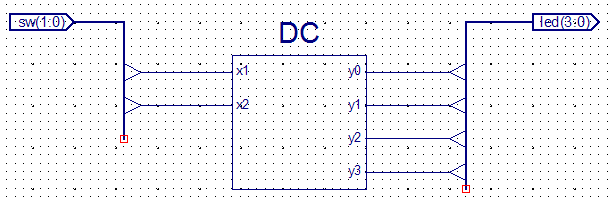

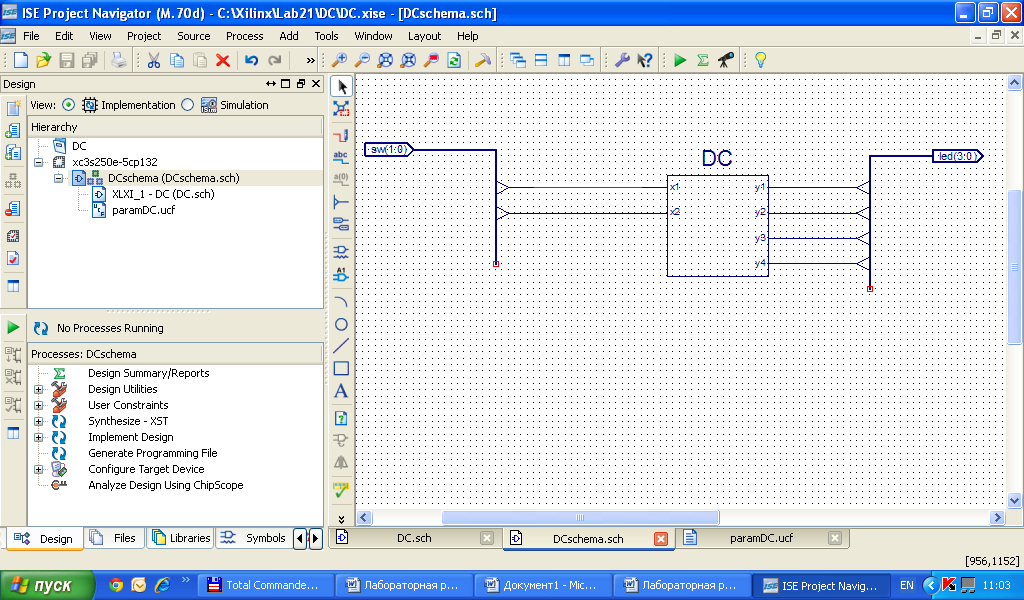

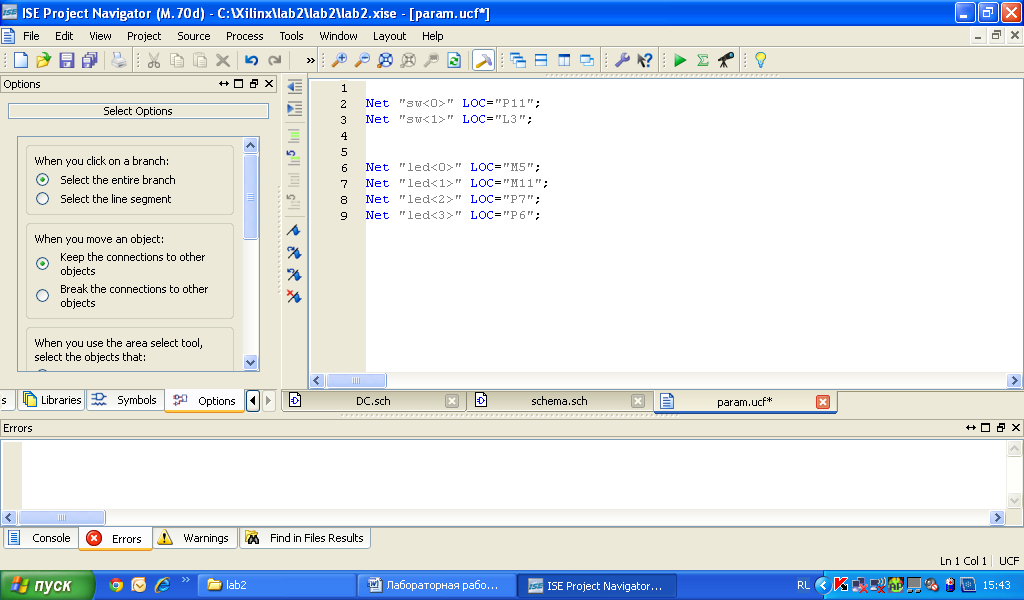

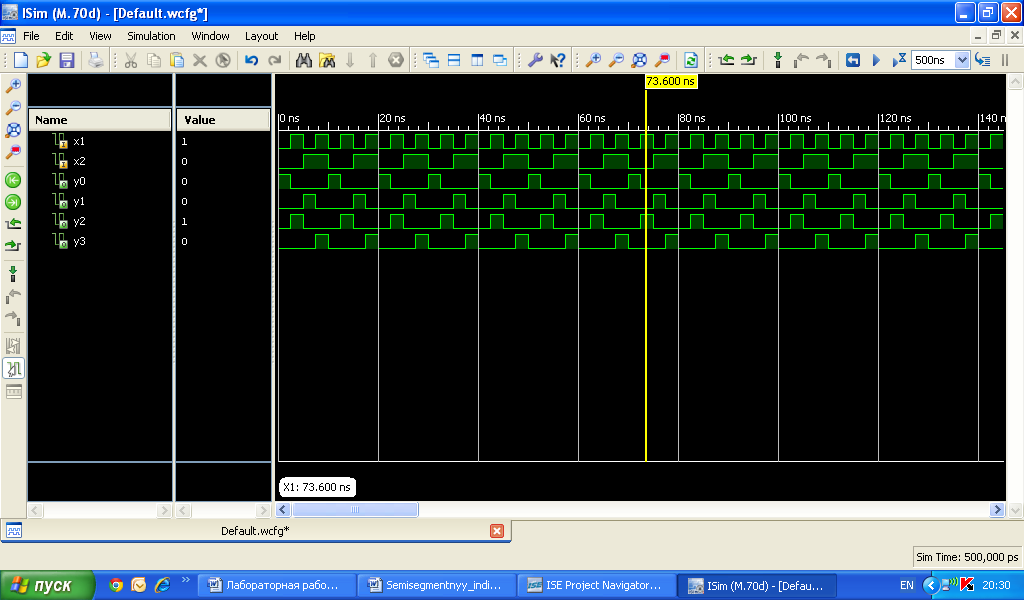

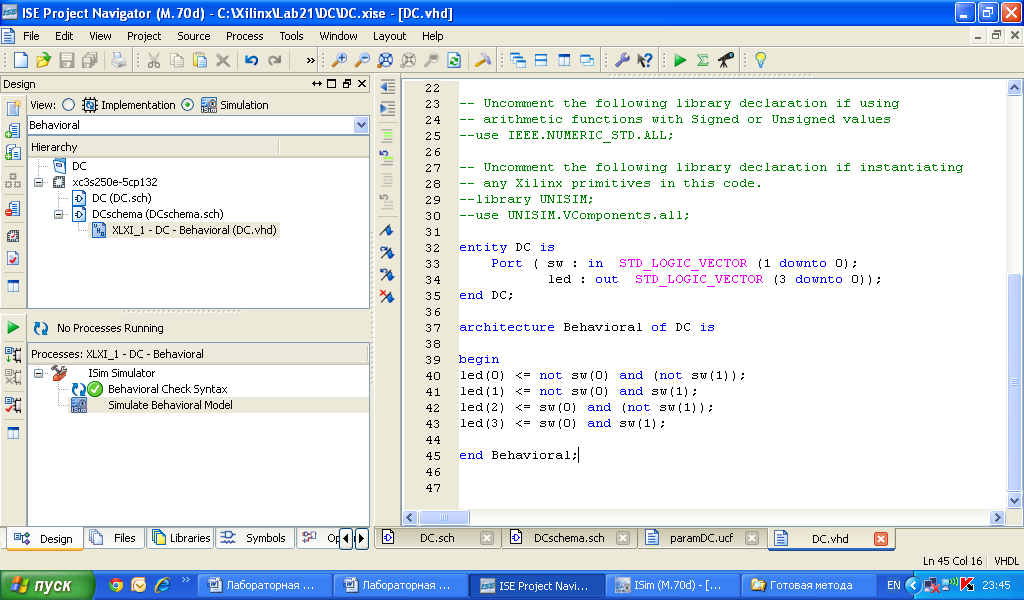

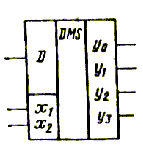

Для построения схемы декодера по таблице истинности воспользуемся методикой, изложенной выше. Например, устройство должно иметь 4 выхода. Для каждого выхода записываем логическое выражение. На основе СДНФ:  По этой системе выражений несложно построить схему требуемого дешифратора (рис.4).  Рис. 4 – схема дешифратора Условное графическое изображение дешифратора (рис.5).  Рис. 5 2.1.1 Создание принципиальной схемы В первую очередь следует запустить программу Xilinx. Создадим новый проект, задаем название FPGA_lab2. Вызываем мастер создания нового источника New Source Wizard, чтобы создать новую схему Schematic, необходимую для дальнейшей работы. Зададим имя нового модуля, File name – DC. Нарисуем принципиальную схему дешифратора (рис.6).  Рис. 6 Теперь нам необходимо представить данную схему дешифратора в виде отдельного элемента, назовём его DC. На главной панели выбираем вкладку ToolsSymbol WizardОткроется окно (рис.7) В строке Usingschematicвыберем имя элемента – DCNextОткроется окно (рис.8).  Рис. 7 В этом окне нужно задать параметры нашего дешифратора. Нажатием на кнопку AddPin – добавится новая строка в которой можно задать параметры входной или выходной ножки. Нажмём на эту кнопку шесть раз, т.к у нас две входных и четыре выходных ножки. Зададим параметры (рис.8).  Рис. 8 Важно чтобы порядок расположения входных и выходных ножек был выбран в правильной последовательности. Далее нажимаем NextFinish элемент создан (рис.9). Новый элемент добавился в библиотеку элементов, и теперь мы можем его использовать в любой схеме.  Рис. 9 Вызываем мастер создания нового источника New Source Wizard, чтобы создать новую схему Schematic, необходимую для дальнейшей работы. Зададим имя нового модуля, File name –Lab2_schema. Начертите схему (рис.10).  Рис. 10 После создания схемы необходимо обозначить каждый проводник, подходящий к шинам sw(1:0) и led(3:0) (рис.11).   Рис.11 Обозначение проводников, подходящих к общим шинам. Теперь осталось создать файл param с расширением *.ucf. В нём опишем привязку выводов проекта к входам-выводам кристалла. Пропишем в нём следующие строки (рис.12).  Рис. 12. Описание схемы. Далее проведём запуск автоматизированного размещения проекта в кристалле и анализ генерируемых отчетов для выявления предупреждений и ошибок, а при отсутствии таковых и не критичных переходим к следующему этапу. Верификация проекта, т. е. окончательное временное моделирование (Post-Fit Simulation) после размещения проекта в кристалле при всех реальных задержках распространения сигналов внутри микросхемы ПЛИС. В окне Hierarchy выбирается проект, а в области окна процессов (Processes) нужно запустить Implement Top Module 2.1.2 Проверка работоспособности схемы Обычно после того, как был создан проект с помощью схемотехнического редактора, перед этапом автоматизированного размещения проекта в кристалле, должен быть этап предварительного функционального моделирования для выявления ошибок и проверки работоспособности проектируемого проекта или отдельных его частей. Проверка работоспособности схемы производится при помощи симулятора ISim. Для этого в режиме симуляции выделяется исследуемая схема и запускается ISim Simulator. (Подробное описание данного шага приведено в лабораторной работе 1). По результатам симулирования работы схемы (рис.13) составляется таблица истинности, на основании которой делается вывод о правильности функционирования дешифратора.  Рис.13. Результат проверки работоспособности схемы. 2.1.3 Реализация на языке VHDL Создается модуль VHDL “DecoderLogicVHDL.vhd”, описание этой операции приведено в лабораторной работе №1. Для схемы дешифратора записываются логические уравнения, описывающие функционирование каждого элемента (рис. 14).  Рис. 14. Описание функционирования дешифратора на языке VHDL. Затем путем нажатия кнопки Create Schematic Symbol в режиме Implementation создается визуальный компонент для данного модуля. Далее производится проверка работоспособности данной программы. Результаты сравниваются и таблицей истинности соответствующей дешифратору. 2.2 Шифратор. Такие устройства выполняют задачи, обратные дешифрации. С их помощью активным значениям определенных входных сигналов можно поставить в соответствие выходные коды (комбинации выходных сигналов). Таблица истинности для кодера с четырьмя входами изображена в таблице 2.2. Таблица 2.2 – Таблица истинности для четырёхразрядного шифратора

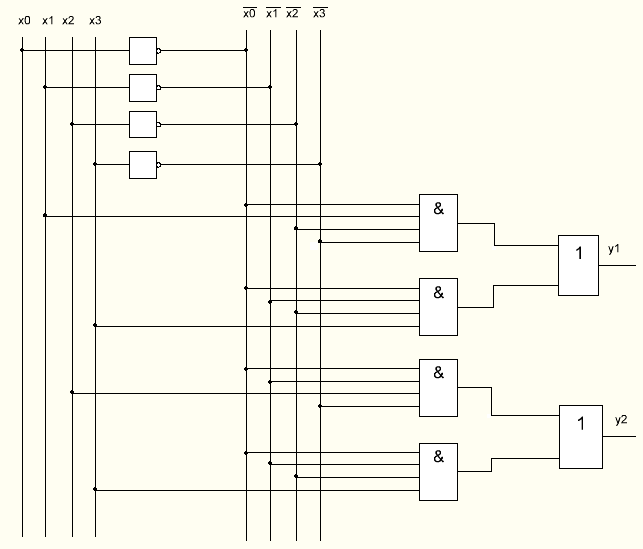

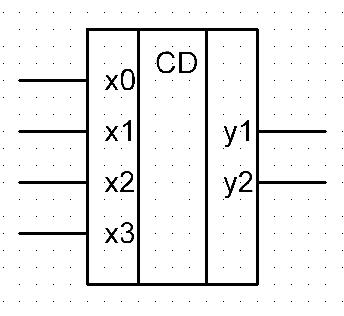

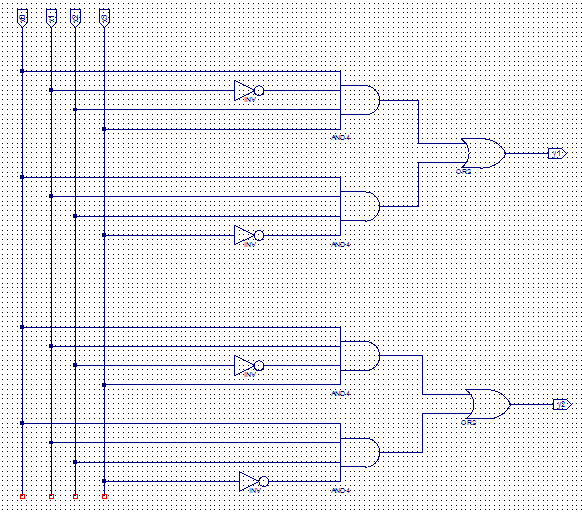

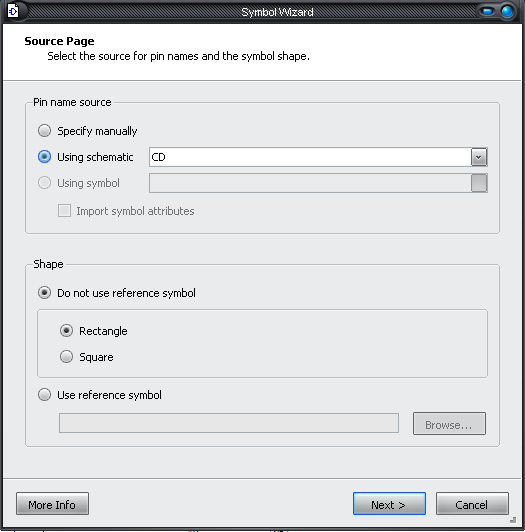

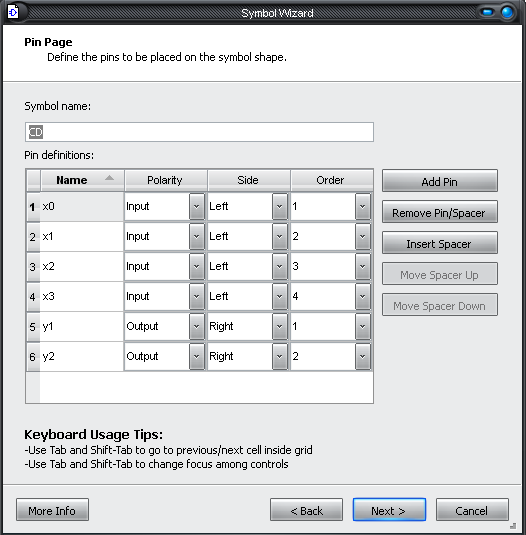

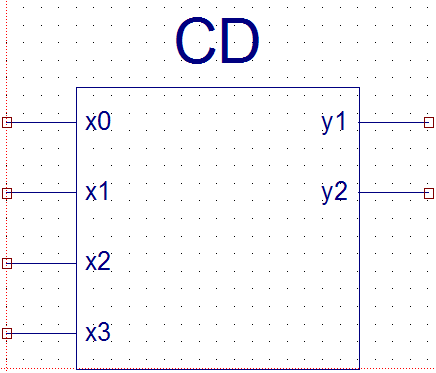

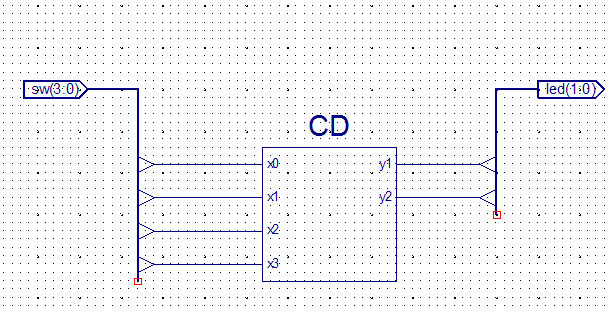

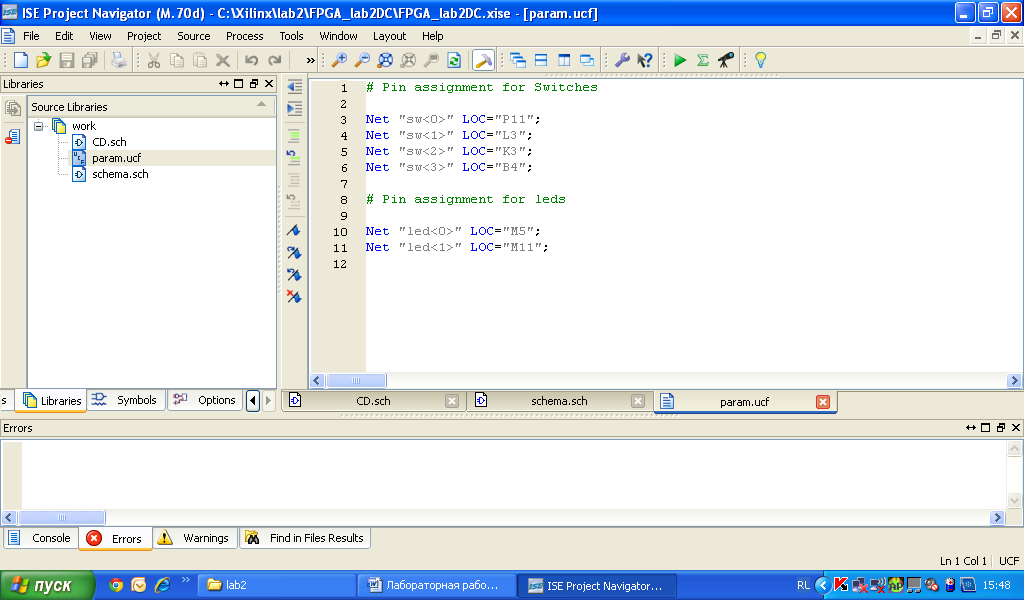

Для каждого выхода записываем логическое выражение. На основе СДНФ:  По этой системе выражений несложно построить схему требуемого шифратора (рис.15).  Рис. 15. Схема шифратора. Условное графическое изображение шифратора (рис.16).  Рис. 16. Создание элемента шифратора. 2.2.1 Создание принципиальной схемы Создадим новый проект, задаем название FPGA_lab2DC. Зададим имя нового модуля, File name – CD. Нарисуем принципиальную схему шифратора (рис.17).  Рис. 17. Принципиальная схема шифратора. Теперь нам необходимо представить данную схему шифратора в виде отдельного элемента, назовём его CD. На главной панели выбираем вкладку ToolsSymbol WizardОткроется окно (рис.18) В строке Usingschematicвыберем имя элемента – CDNextОткроется окно (См. рис.19) В этом окне задаются параметры нашего кодера.  Рис. 18  Рис. 19 Далее нажимаем NextFinish элемент создан (рис.20) Новый элемент добавился в библиотеку элементов и теперь мы можем его использовать в любой схеме.  Рис. 20. Элемент шифраторы. Вызываем мастер создания New Source Wizard, чтобы создать новую схему Schematic, необходимую для дальнейшей работы. Зададим имя нового модуля, File name –Lab2_schema (рис.21).  Рис. 21. Схема шифратора. Осталось создать файл param с расширением *.ucf. В нём опишем привязку выводов проекта к входам-выводам кристалла (рис.22).  Рис. 22 Последовательность дальнейших действий такая же, как при проверке работоспособности схемы дешифратора. При VHDL-программировании для схемы шифратора записываются логические уравнения, описывающие функционирование каждого элемента. 2.3 Мультиплексор Мультиплексор – это устройство, обеспечивающее коммутацию на выходе одного из нескольких информационных входных сигналов в соответствии с заданным кодом на управляющих входах. Такая схема позволяет управлять переключением информационных входов мультиплексора при помощи двоичных кодов, подаваемых на его управляющие входы. Количество информационных входов в таких схемах выбирают кратным степени числа два. Таблица истинности для мультиплексора с двумя управляющими входами изображена в таблице 2.3. Таблица 2.3 – Таблица истинности для мультиплексора

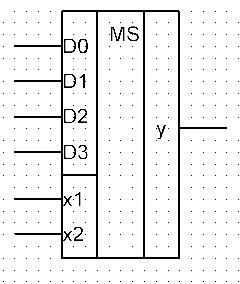

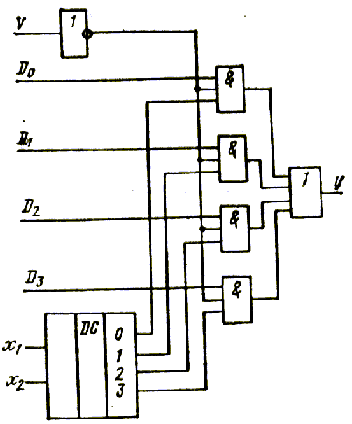

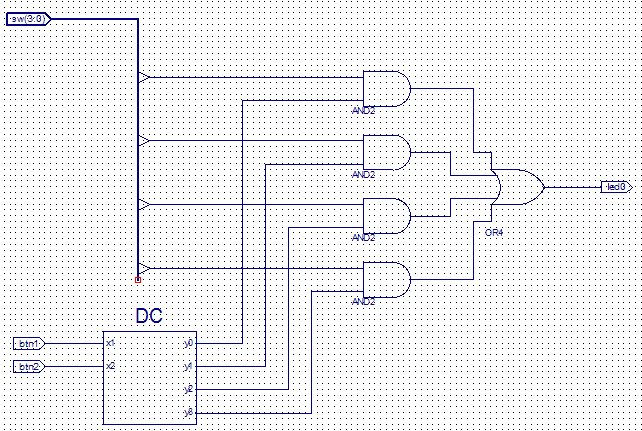

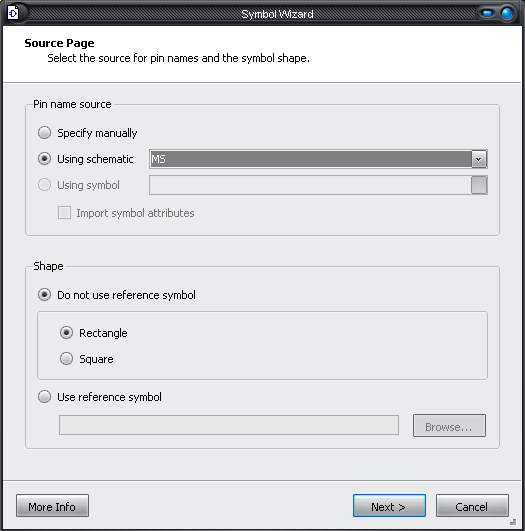

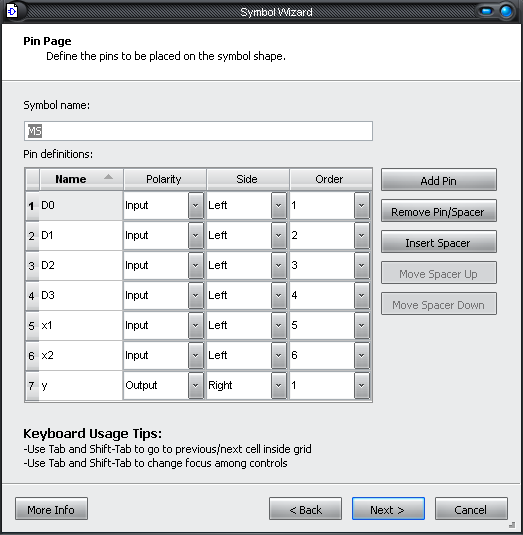

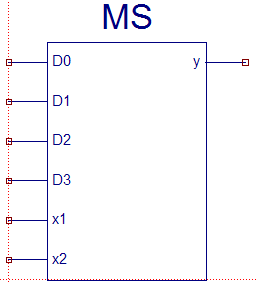

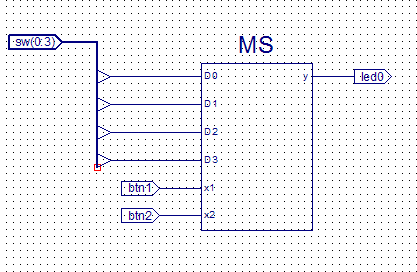

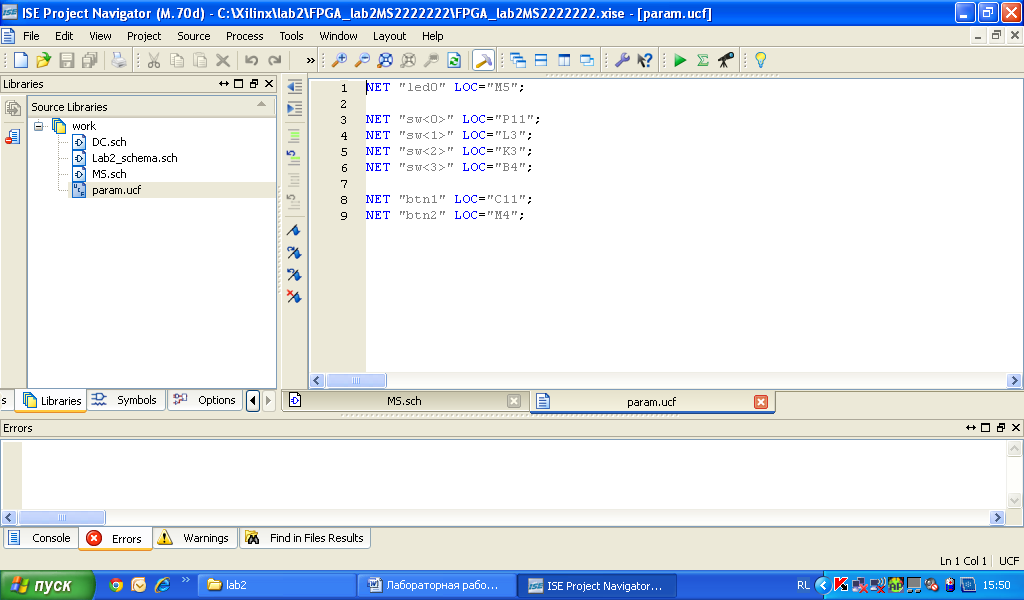

Условное графическое обозначение одного из вариантов мультиплексора (рис.23).  Рис. 23. Мультиплексор D0, D1, D2, D3 – информационные входы, а х1 и х2 – управляющие. Пример структурной схемы мультиплексора (рис.24).  Рис. 24. Схема мультиплексора. Создание принципиальной схемы Всё делаем аналогично методике создания схем шифратора и дешифратора. Создадим новый проект, задаем название FPGA_lab2MS. Вызываем мастер создания нового источника New Source Wizard, чтобы создать новую схему Schematic, необходимую для дальнейшей работы. Зададим имя нового модуля, File name – MS. Нарисуем принципиальную схему мультиплексора (рис.25). Данная схема содержит встроенную схему дешифратора, методика создания которого приведена выше.  Рис. 25. Принципиальная схема мультиплексора. Теперь нам необходимо представить данную схему мультиплексора в виде отдельного элемента, назовём его МS. На главной панели выбираем вкладку ToolsSymbol WizardОткроется окно (рис.26) В строке Usingschematicвыберем имя элемента – MSNextОткроется окно (рис.27) В этом окне заданы параметры нашего мультиплексора.  Рис. 26  Рис. 27 Далее нажимаем NextFinish элемент создан (рис.28). Новый элемент добавился в библиотеку элементов и теперь мы можем его использовать в любой схеме.  Рис. 28 Вызываем мастер создания нового источника New Source Wizard, чтобы создать новую схему Schematic, необходимую для дальнейшей работы. Зададим имя нового модуля, File name –Lab2_schema. На основе нового элемента MS начертите схему (рис.29).  Рис. 29 Остаётся создать файл param с расширением *.ucf. В нём опишем привязку выводов проекта к входам-выводам кристалла. Пропишем следующие строки (рис.30).  Рис. 30 Далее необходимо выполнить проверку работоспособности схемы. А так же написать программу на VHDL, которая будет описывать работу мультиплексора. 2.4 Демультиплексор Представляет собой цифровое устройство для коммутации информационного входного сигнала на один из нескольких выходов в соответствии с заданным кодом на управляющих входах, т.е. решают задачи, обратные мультиплексированию. Условное графическое обозначение демультиплексора с четырьмя информационными выходами (рис.31).  Рис. 31 Таблица истинности для демультиплексора изображена в таблице 2.4. Таблица 2.4 – Таблица истинности для демультиплексора

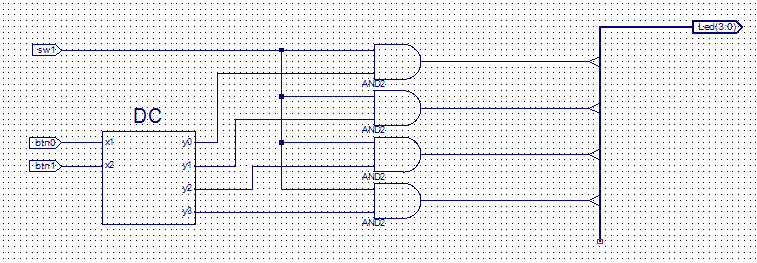

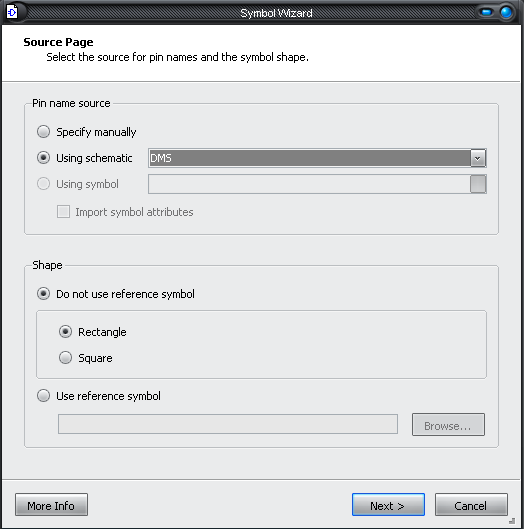

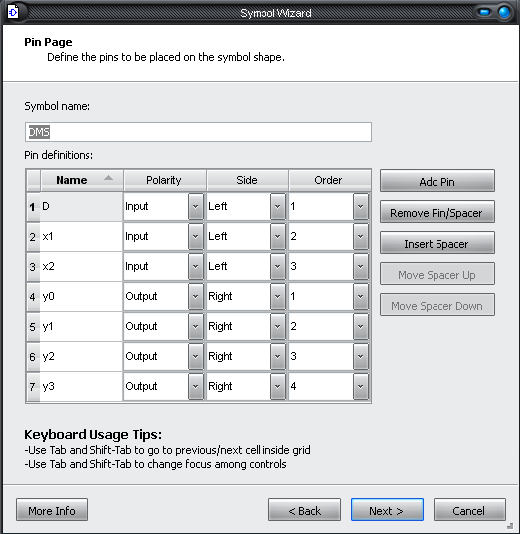

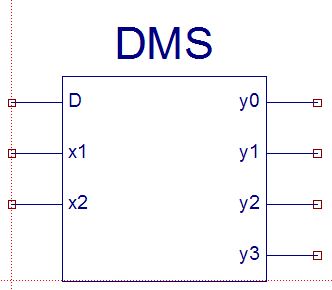

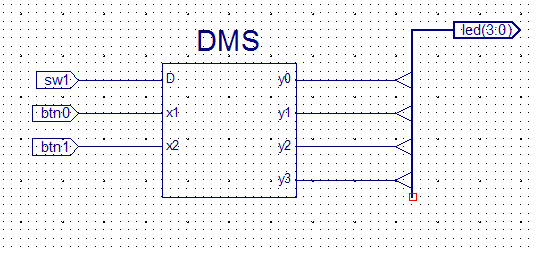

Создание принципиальной схемы Всё делаем аналогично методике создания схемы мультиплексора. Создадим новый проект, задаем название FPGA_lab2DMS. Вызываем мастер создания нового источника New Source Wizard, чтобы создать новую схему Schematic, необходимую для дальнейшей работы. Зададим имя нового модуля, File name – DMS. Нарисуем принципиальную схему демультиплексора (рис.32). Данная схема содержит встроенную схему дешифратора, методика создания которого была приведена выше. Теперь нам необходимо представить данную схему мультиплексора в виде отдельного элемента, назовём его DМS. На главной панели выбираем вкладку ToolsSymbol WizardОткроется окно (рис.33) В строке Usingschematicвыберем имя элемента – DMSNextОткроется окно (рис.34) В этом окне заданы параметры нашего демультиплексора.  Рис. 32  Рис.33  Рис. 34 Далее нажимаем NextFinish элемент создан (рис.35). Новый элемент добавился в библиотеку элементов и теперь мы можем его использовать в любой схеме.  Рис. 35 Вызываем мастер создания нового источника New Source Wizard, чтобы создать новую схему Schematic, необходимую для дальнейшей работы. Зададим имя нового модуля, File name –Lab2_schema. На основе нового элемента DMS начертите схему (рис.36).  Рис. 36 Остаётся создать файл param с расширением *.ucf. В нём опишем привязку выводов проекта к входам-выводам кристалла. Пропишем следующие строки (рис.37).  Рис. 37 3.Задание к работе Исследовать принцип работы типовых комбинационных схем: дешифратора, шифратора, мультиплексора, демультиплексора. Заполнить таблицы истинности для каждой схемы. Таблица 3.1 – Таблица, описывающая работу дешифратора

Таблица 3.2 – Таблица, описывающая работу шифратора

Таблица 3.2 – Таблица, описывающая работу мультиплексора

Таблица 3.4 – Таблица истинности для демультиплексора

Содержание отчета 1 Цель работы. 2 Структурные формулы и схемы для дешифратора, шифратора, мультиплексора, демультиплексора. 3 Таблицы истинности исследуемых схем. 4 Выводы. Контрольные вопросыДайте определение комбинационного цифрового устройства. Дайте определение мультиплексора. Приведете таблицу истинности мультиплексора. Приведите примеры использования мультиплексоров. Синтезируйте четырехвходовой мультиплексор. Дайте определение дешифратора. Приведете таблицу истинности дешифратора. Приведите примеры использования дешифраторов. Синтезируйте трехвходовой дешифратор в базисе И-НЕ (ИЛИ-НЕ). Дайте определение шифратора. Приведете таблицу истинности шифратора. Приведите примеры использования шифраторов. Синтезируйте восьмивходовой шифратор в базисе И-НЕ (ИЛИ-НЕ). Дайте определение демультиплексора. Приведете таблицу истинности демультиплексора. Приведите примеры использования мультиплексоров. Синтезируйте демультиплексор с четырьмя выходами. Приведите пример схемы демультиплексора, выполненного на дешифраторе. Поясните назначение двунаправленного коммутатора аналоговых и цифровых сигналов. Какими параметрами он характеризуется? |