ДИИДС лаб.раб №3 Послед. схемы. Лабораторная работа 3 Часть Триггеры Цель изучение типов триггеров и их функций. Продолжительность лабораторной работы 4 часа

Скачать 1.8 Mb. Скачать 1.8 Mb.

|

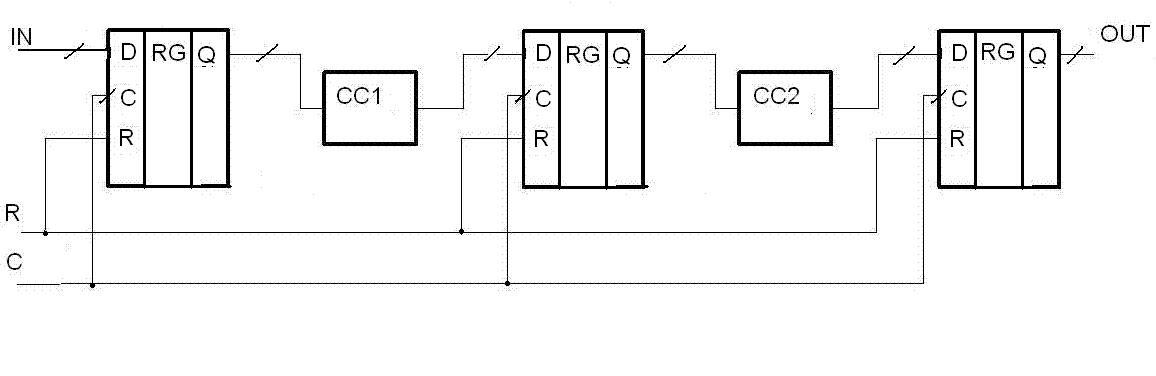

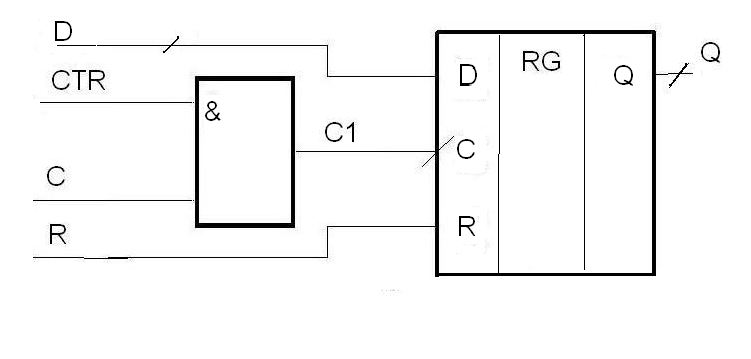

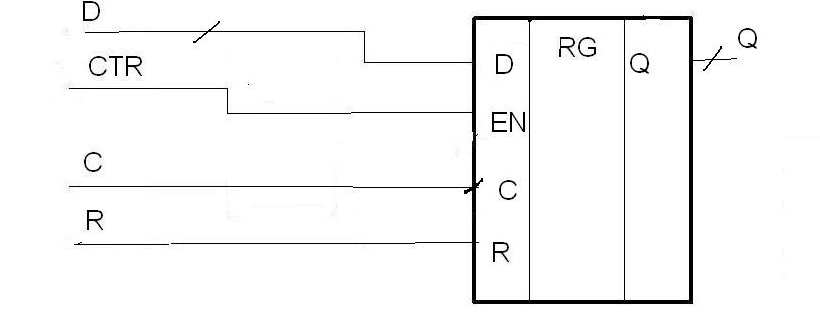

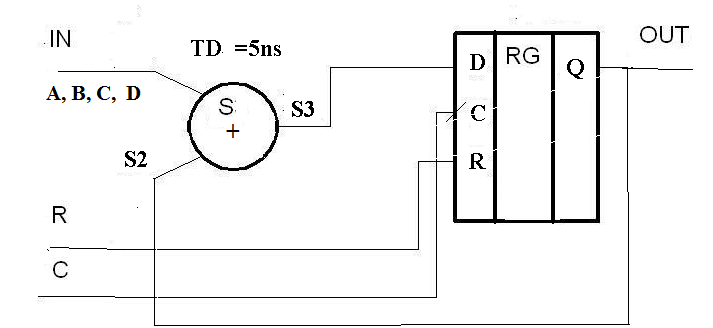

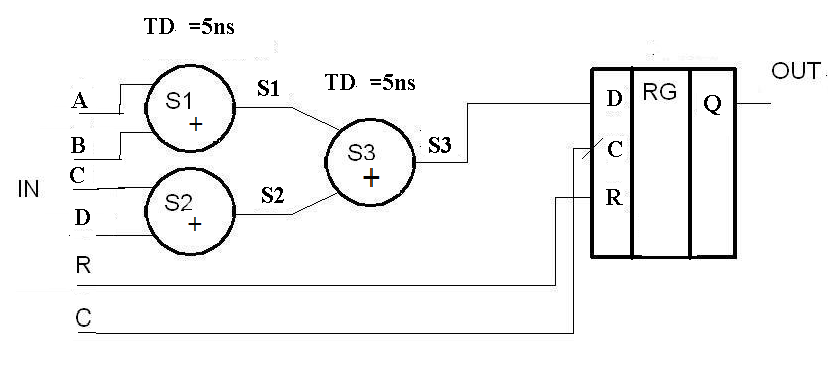

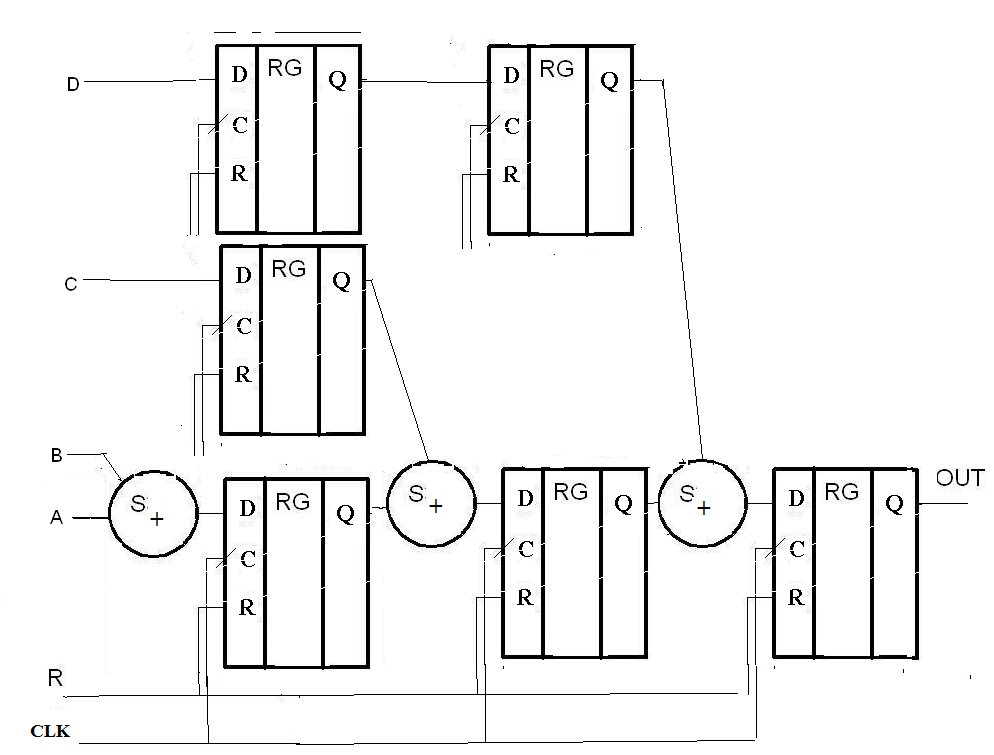

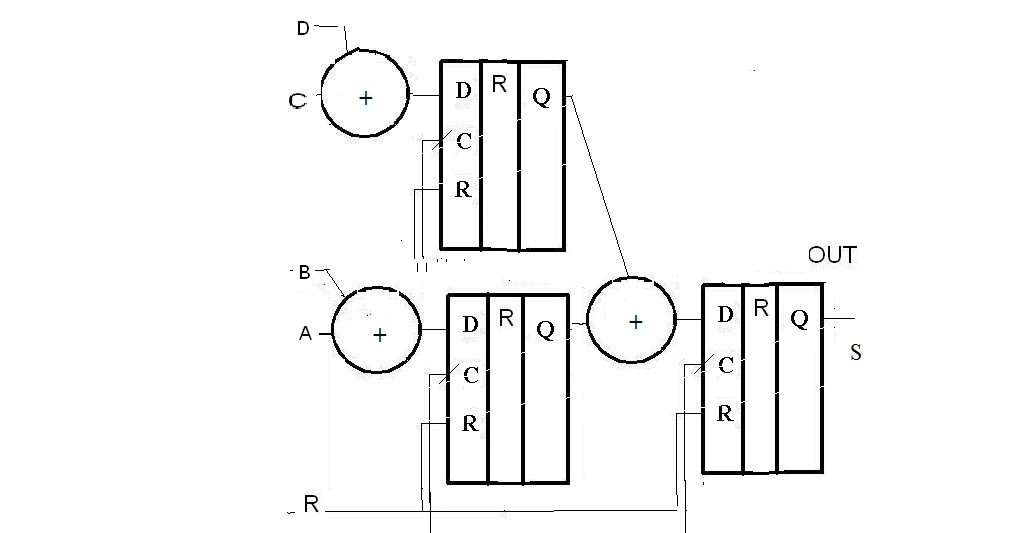

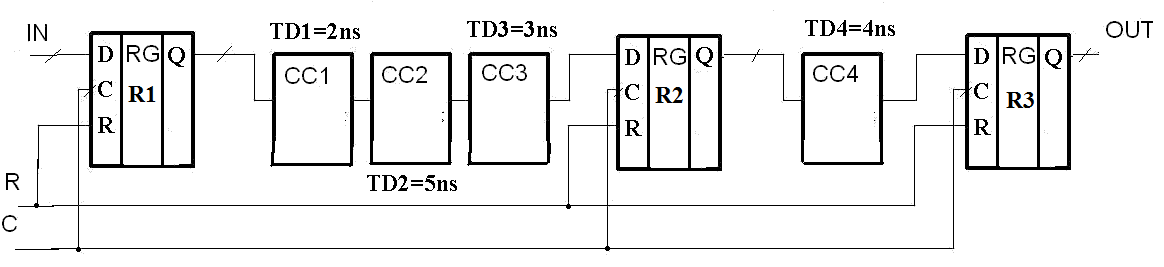

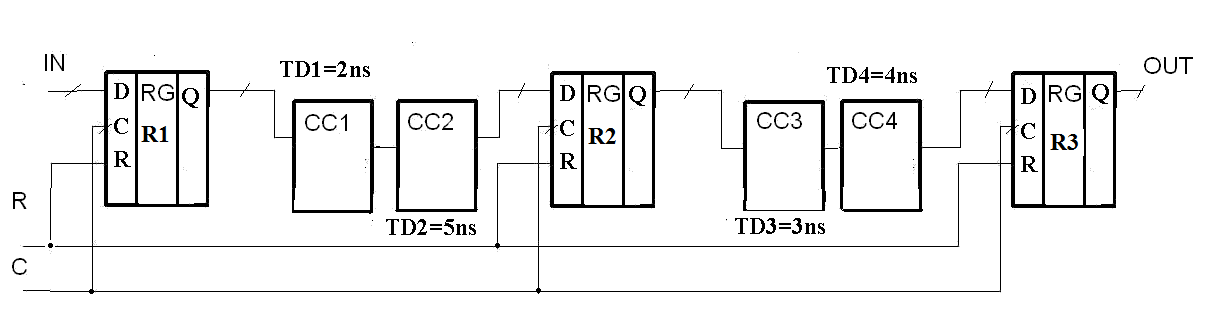

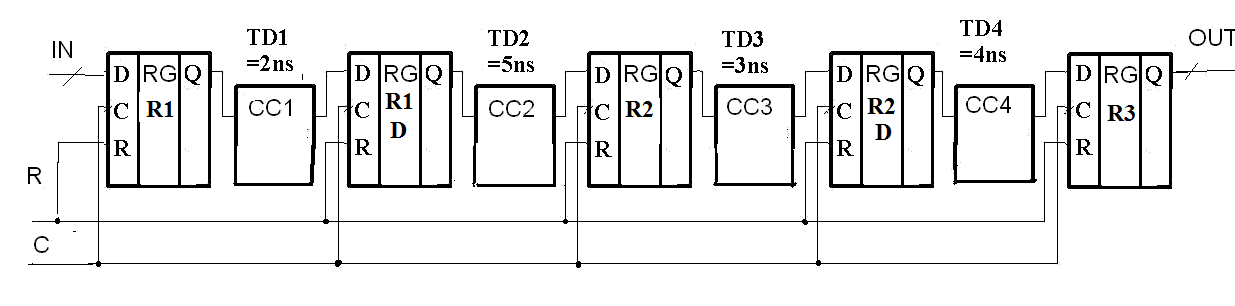

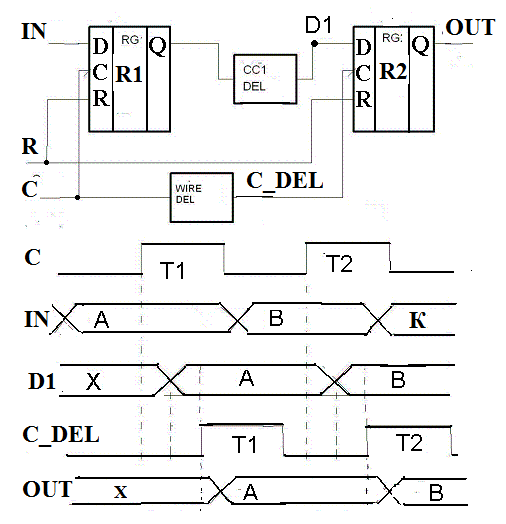

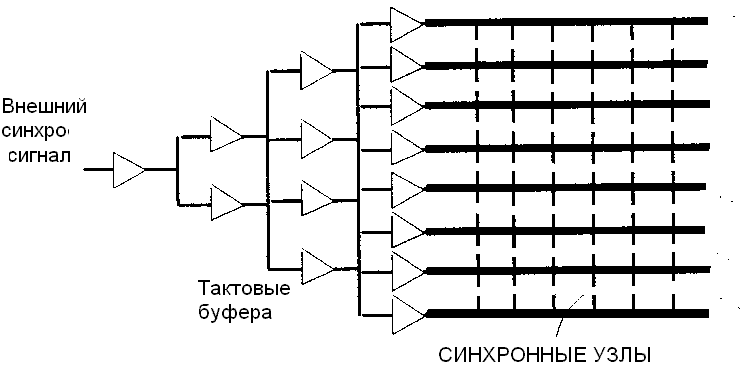

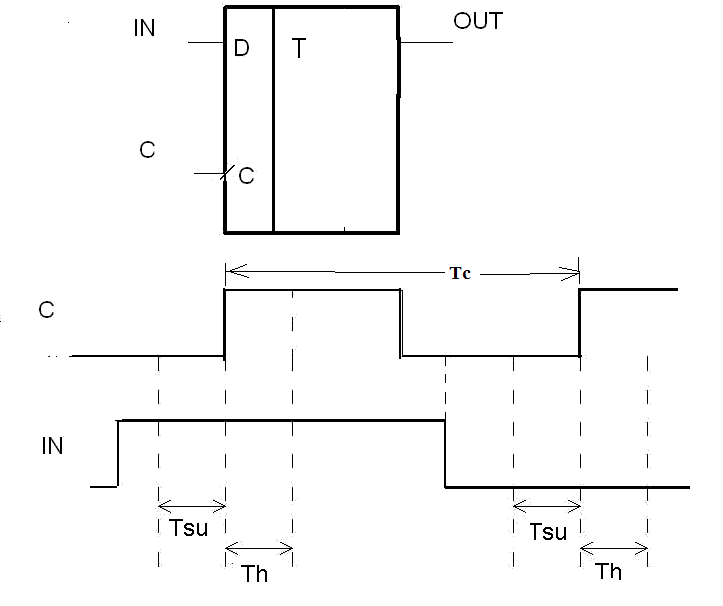

Часть 3 .Изучение методов проектирования синхронных схемЦель работы состоит в изучении основных характеристик счетчиков и изучении методики проектирования синхронных схем , а также овладение практическими навыками моделирования цифровых схем Проектирование синхронных схем Современные подходы к проектированию цифровой аппаратуры рассмотрены в большом числе литературных источников.Ниже приводятся лишь некоторые рекомендации из этой области. При их анализе временных соотношений следует учитывать, что в схемах, реализованных на элементах среднего уровня интеграции типа отечественных серий КР1553 и КР1554 тактовые частоты лежат в пределах десятков мегагерц и задержки сигналов в проводниках существенно меньше задержек сигналов в элементах. Однако в современных Больших Интегральных Схем(БИС) с тактовой частотой в несколько сотен мегагерц задержки в проводниках соизмеримы с задержками логических элементов и могут превышать их. Понятие синхронной схемы Синхронные схемы (модули) – это тактируемые схемы, которые обладают следующими свойствами. 1)Все запоминающие элементы схемы (триггеры–flipflop, регистры(register), блоки памяти (оперативной – ОЗУ (RAM), постоянной– ПЗУ(ROM), с организацией типа очередь– ФИФО(FIFO )и т.п.) должны изменять свои состояния одновременно по одному и тому же активному фронту поступающего извне тактового сигнала(С- clock ). 2)Этот синхросигнал(С-clock) без задержек, т.е. одновременно, должен поступать на все запоминающие элементы схемы. Внешний синхросигнал при реализации синхронной схемы на кристалле вводится через специальный тактовый буфер и разводится так, чтобы обеспечить одновременность его поступления на все запоминающие элементы. На рис.6.1 представлена обобщенная структура синхронной схемы с однотактной синхронизацией (сигнал С). К моменту прихода внешнего синхросигнала С на регистры (RG–register) выходы комбинационных схем (CC–combinatorial circuit) должны успеть принять стабильное состояние.  Рис.7.1. Обобщенная структура синхронной схемы Таким образом, согласно принципам «чистого синхронизма» не рекомендуется, например, строить схемы, в которых применяются управляемые синхросигналы (gated clocks). Управляемым называется синхросигнал, генерируемый внутри схемы и трассируемый, если САПР не получает специальных указаний от проектировщика, как обычный сигнал. На схеме рис.7.2 это сигнал C1.  Рис.7.2. Схема приема на регистр с управляемым синхросигналом С1 . Применение «управляемых синхросигналов» сильно усложняет расчет временных параметров схем. Использование триггеров с разрешающим входом, как это показано на рис.7.3 во многих случаях позволяет избежать ситуации с управляемыми синхросигналами.  Рис.7.3. Улучшенный вариант схемы приема на регистр, построенный на триггерах с разрешающим входом EN Прежде чем рассмотреть синхронные схемы более подробно, следует ответить на вопрос, почему в основной массе проектов используются синхронные, а не асинхронные схемы? Преимущества 1) Синхронные схемы более устойчивы к разбросу параметров элементов и условий эксплуатации – температуры, напряжения источников питания и т.п. 2) Элементная база современных БИС в основном ориентирована на синхронную схемотехнику. 3) Интерфейс между двумя блоками синхронных устройств обычно более прост, чем между двумя асинхронными и не требует реализации протоколов типа «рукопожатие». 4) Большинство современных САПР ориентировано на проектирование синхронных схем. К недостаткам синхронных схем относится высокое энергопотребление сети распространения синхросигналов и помехи, порождаемые мощными синхроимпульсами. 7.1.2. Параллелизм и конвейеризация Есть два известных пути повышения производительности(количество информации ,перерабатываемой в единицу времени) и быстродействия ( для схем это тактовая частота)устройств – это параллелизм и конвейеризация. Рассмотрим в качестве примера схему сложения четырех слагаемых S=A+B+C+D. Вариант последовательного сложения представлен на рис.7.4. Схема использует один сумматор и регистр и требует четырех тактов на выполнение операции.Задержка в тактах от поступления информации на вход до получения результата- латентность схемы равна 4 тактам . Tсл_послед= 4*ТD, где время ТD включает задержку на сумматоре и на регистре . После обнуления регистра сигналом сброса R,А +0 загружается в регистр на первом такте, В+А на втором и т.д.Устройство управления,отчситывающее число тактов и вырабатывающее сигналы управления( занято-свободно, готово и т.п.) на рис 7.4 не отражено.Количество оборудования(без учета управления) Ко_послед=1Рг+1См(один сумматор+регистр).  Рис.7.4.Последовательный вариант вычисления суммы четырех слагаемых (Tсл_послед= 4*TD,Ко_послед=1Рг+1См ) Параллелизм. Примером использования принципа параллелизма может служить схема вычисления суммы четырех слагаемых S=(A+B)+(C+D) c использованием трех сумматоров и одного регистра. Первые два сумматора параллельно вычисляют выражения в скобках (рис.7.5.).Задержка такой схемы состоит из двух задержек сумматора и задержки регистра.Тактовый период этой схемы больше, чем у последоватеьлной за счет задержки не одного,а двух сумматоров.Tclk_пар>Tclk_посл. Tсл_парал= 2*TD,Ко_парал=1Рг+3См  Рис.5.5.Параллельный вариант вычисления суммы четырех слагаемых (Tсл_парал= 2*TD,Ко_парал=1Рг+3См) По сравнению с последовательным вычислением суммы S=A+B + C+D такая схема позволяет уменьшить время получения результата в два раза. Однако обьем аппаратуры – количество сумматоров увеличилось в три раза и количество шин в 2,5 раз. Конвейеризация. На рис.7.6.представлен вариант конвейерной организации схемы сложения четырех слагаемых. Схема использует три регистра и три сумматора. Первая сумма на выходе OUT конвейера появляется через три такта (время инициализаци конвейера в данном случае равно его латентности ), а далее новые суммы появляются на каждом такте. Если время такта равно TD. то производительность этой схемы в четыре раза больше, чем у последовательного варианта (рис.7.4), а быстродействие примерно в два раза больше, чем у параллельного (рис.7.5). Однако количество регистров в конвейерной схеме возросло в шесть раз по сравнению с параллельным вариантом суммирования четырех чисел А.B,C, D (рис.7.5). Ко_конв= 6рг+3cм А по сравнению с последовательным вариантом  Рис.7.6.Конвейерный вариант вычисления суммы четырех слагаемых (TсLk_конв= TD,Ко_конв= 6рг+3cм) ) Параллелизм в сочетании с конвейеризацией На рис 7.7 представлен вариант сочетающий параллельное суммирование четырех слагаемых и конвейерный принцип разделения суммирования на два этапа. Читателю предлагается оценить плюсы и минусы такого решения.  Рис.7.7. Параллельно-конвейерная реализация устройства сложения четырех чисел Балансировка конвейера На рис.7.8.представлена некоторая трехкаскадная конвейерная схема. Блоки ее комбинационной части CC1,CC2.CC3,CC4 ( СС-Combinatorial circuit) имеют разные задержки, обозначенные как TD1=2нс.,TD2=5 нс., TD3=3 нс.,TD4=4 нс.  Рис.7.8. Обобщенная конвейерная схема, состоящая из трех каскадов Напомним , что наиболее длинный путь сигнала в комбинационной части схемы называется критическим. Критический путь во многом определяет быстродействие схемы. В схеме рис.5.7 критический путь находится в первой комбинационной части (на входе регистра R2), состоящей из блоков CC1.CC2.CC3 При расчете его задержки Tкр= TD1+TD2+TD3=10 ns учитываются как максимальные задержки сигналов элементов, лежащих на этом пути, так и задержки их связей. Как уменьшить задержку критического пути и повысить быстродействие конвейерных схем? Одним из путей решения этой задачи является балансировка конвейера. В сбалансированном конвейере все задержки комбинационных частей примерно равны. Представленная На рис.7.9. схема конвейера сбалансирована по задержкам комбинационных частей (в первой части задержка =TD1+ TD3=7 нс., во второй задержка =TD3 +TD4=7 нc) путем перемещения второго (считая слева- направо) регистра R2 «вперед» или другими словами комбинационного блока СС3 в комбинационную часть другого регистра- R3. Тактовую частоту в сбалансированном конвейере рис.5.8 удалось повысить примерно в 1,3 раза ( 10/7) по сравнению с схемой рис.7.7.  Рис.7.8. Сбалансированный конвейер (Tкр=TD1+TD2=TD3+TD4=7ns) В схеме представленной на рис.7.10. дальнейшее улучшение быстродействия конвейера достигнуто добавлением двух промежуточных регистров(R1D и R2D).  Рис.7.10. Конвейер с добавлением промежуточных регистров (Tкр=TD2=5 ns) Глубина-латентность конвейера, представленного на рис.7.10 увеличилась (теперь не 3 , как на рис.7.8 , а 5 каскадов), но задержка критического пути уменьшилась и стала равна 5 нс., В общем случае, повышение быстродействия конвейерной схемы достигается, если это возможно, путем разбиения комбинационной части с большим критическим путем на отдельные составляющие и введением дополнительных регистров между ними для хранения промежуточных данных. Таким способом тактовая частота и быстродействие конвейера повышается, но за счет увеличения расхода оборудования и латентности (latency)- задержки появления первой информации на выходе конвейера после его запуска. Есть ли предел на пути повышения тактовой частоты? Имеется множество ограничений, часть из которых будет упомянута ниже. 7.1.3. Сеть распространения синхросигналов По мере увеличения быстродействия схем сеть разводки (clock distribution net) тактовых сигналов (синхросигналов) становится все более сложным компонентом устройств. К ее важнейшим параметрам следует отнести . А) Расфазировка или разброc моментов поступления синхросигнала (ClockSkew) на различные элементы схемы. Этот параметр статический. Он означает разницу моментов поступления синхросигнала в различные части устройства. На рис.7.11 показан случай, когда задержка синхросигнала в цепи разводки(wire_del) больше задержки комбинационной части схемы(CC1_del), что приводит к ее неправильной работе. Данные А, поступающие на вход схемы в такте Т1, по синхросигналу С принимаются на регистр RG1 и сразу после обработки в комбинационной схеме CC1 принимаются на второй регистр RG2 по синхросигналу C_del и передаются на выход OUT в том же такте Т1. Основными причинами разброса моментов поступления синхроимпульсов являются разница в длинах проводников, по которым они распространяются и нагрузок на их источники – буферные тактовые повторители. Задержка повторителя, нагруженного на один элемент, естественно меньше, чем у нагруженного на десяток, даже если не учитывать емкостную нагрузку ведущих к ним проводников (wire load). К способам уменьшения этого разброса относятся: трассировка каждого яруса ветвей дерева синхросигналов проводниками одинаковой длины и ширины, повышение нагрузочных возможностей тактовых буферных повторителей ( см.рис.7.12) и применение специальных элементов (узлов), обеспечивающих автоподстройку фаз синхросигналов.  Рис.7.11. Задержка синхросигнала(C_DEL) в цепи разводки синхросигналов приводит к неправильной работе схемы Б) Нестабильность и искажение формы синхросигнала (ClockFidelity,ClockJitter). Это параметр динамический. Временная диаграмма тактового сигнала должна иметь минимум искажений формы(ClockFidelity) и не «дрожать» (Clock Jitter). Реальная форма синхросигнала частотой в несколько сотен мегагерц далека от идеальной прямоугольной, рисуемой в курсовых проектах студентами. Она скорее напоминает синусоиду с наложенным на нее шумом помех и наводок. Так как порог срабатывания триггеров имеет разброс, пологий фронт синхросигналов также может служить источником разброса моментов срабатывания запоминающих элементов схемы. Дрожь синхроимпульсов (ClockJitter–динамический разброс моментов их поступления) определяется такими факторами, как наводки, нестабильность питания за счет изменения на каждом такте количества переключаемых элементов и т.п. На высоких частотах проводники ведут себя как длинные линии с индуктивной и емкостной составляющими и важно избегать отражений сигналов на их концах– правильно их терминировать, используя либо резисторы с параметрами, равными волновому сопротивлению линии, либо специальные терминирующие элементы, применять защиту от помех –экранирование и т.п. Цепь разводки синхросигналов Основные идеи процесса трассировки (разводки) синхросигналов в схеме сводятся к следующим. Строится граф -дерево разводки синхросигналов (рис.7.12). Все конечные вершины графа должны быть равноудаленными от корня дерева (места поступления синхросигнала в схему). Каждой вершине сопоставляется буфер–повторитель. Количество буферов (тактовых буферов) на пути от вершины к каждому синхронизируемому элементу должно быть одинаковым. На каждом ярусе дерева разводки все узлы должны быть одинаково нагружены, т.к. задержки слабо нагруженных тактовых буферов примерно вдвое меньше, чем у максимально нагруженных.  Рис.7.12. Дерево разводки синхросигналов Проектирование систем синхронизации и разводка синхросигналов по конструктиву микросхемы БИС выполняется опытными специалистами с использованием специальных подсистем САПР типа компиляторов синхросигналов– (clockcompiler). Проектировщикам предлагается также набор специальных узлов, с помощью которых может проводиться коррекция расфазирования синхросигналов и если необходимо, умножение или понижение их частоты. Эти узлы в зарубежной терминологии называются :цифровыми схемами управления синхросигналами ( DCM–DigitalClockManager),узлами согласования фазы сигнала( PLL–PhaseLockedLoop),узлами согласования задержек(DLL–DelayLockedLoop) и т.п.[2,3]). Помимо использования таких узлов, проектировщик может выделять в проекте отдельные области локальной синхронизации (такт– домены–clockdomain),малый размер которых упрощает задачу разводки и использовать в них быстрые локальные синхросигналы (Local clock) вместо медленных глобальных (Global clock). 7.1.4. Полезная и вспомогательная часть такта Среди методов повышения быстродействия схем были отмечены такие, как балансировка конвейера и уменьшение длины критического пути в комбинационных частях схем . Но повышение тактовой частоты не беспредельно. Помимо ограничений типа конечной скорости света, существуют и дополнительные факторы, ограничивающие пределы уменьшения тактового периода-периода синхросигнала. На рис.7.13. определены два временных параметра, соблюдение которых необходимо для обеспечения правильной работы триггеров синхронных схем. А) Время предустановки данныхTsu (Tsetup)–минимальный интервал времени перед активным фронтом синхросигнала, в течение которого входной сигнал данных должен быть стабилен. Б) Время выдержки или удержания данных Th (Thold)–минимальный интервал времени после активного фронта синхросигнала, в течение которого входной сигнал данных должен оставаться стабилен.  Рис.7.13. Необходимые минимальные времена предустановки Tsu и удержанияTh данных IN относительно синхросигнала C в D-триггере Обозначим длительность такта – периода синхросигнала– как Тc. Разделим длительность такта Tc на две части: полезную Tlogic и вспомогательную Tseq. Вспомогательная часть Tseq– это то время, которое минимально необходимо для правильной работы триггеров . Для длительности вспомогательной (Tseq ) части такта имеем |