ДИИДС лаб.раб №3 Послед. схемы. Лабораторная работа 3 Часть Триггеры Цель изучение типов триггеров и их функций. Продолжительность лабораторной работы 4 часа

Скачать 1.8 Mb. Скачать 1.8 Mb.

|

|

| № | Две реализации | операция |

| 1 | последовательную и параллельную | И |

| 2 | последовательную и конвейерную | ИЛИ |

| 3 | параллельную и конвейерную | И-НЕ |

| 4 | последовательную и параллельную | ИЛИ-НЕ |

| 5 | последовательную и конвейерную | + |

| 6 | параллельную и конвейерную | nor |

| 7 | параллельную и конвейерную | И-не |

| 8 | последовательную и параллельную | ИЛИ-не |

| 9 | последовательную и конвейерную | ИЛИ |

| 10 | последовательную и параллельную | xor |

| 11 | параллельную и конвейерную | + |

| 12 | последовательную и конвейерную | + |

| 13 | параллельную и конвейерную | И-НЕ |

| 14 | последовательную и параллельную | ИЛИ-НЕ |

| 15 | последовательную и конвейерную | И |

| 16 | параллельною и конвейерную | ИЛИ |

| 17 | параллельную и конвейерную | XOR |

| 18 | последовательную и параллельную | ИЛИ-не |

| 19 | последовательную и конвейерную | + |

7.2. Схемотехника ПЛИС типа FPGA

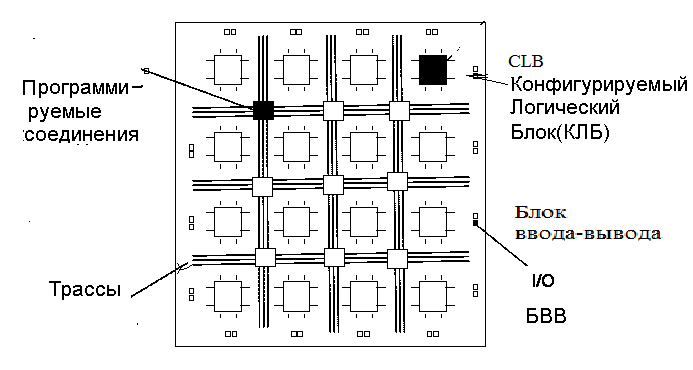

FPGA (Field Programmable Gate Array)–это другой тип ПЛИС. На площади кристалла микросхемы ПЛИС (рис.7.8) типа FPGA размещена матрица из множества программируемых функциональных блоков и множество программируемых соединений (PM–Programmable Interconnections). Функциональные логические блоки в ПЛИС типа FPGA называются конфигурируемыми логическими блоками (КЛБ), а в англоязычной литературе CLB–Сonfigurable Logic Block. В свою очередь КЛБ состоят из логических ячеек (ЛЯ).

Рис. 7.8. Структура ПЛИС типа FPGA

По периметру микросхемы размещены блоки ввода–вывода сигналов (IOB–Input Output Block). В отличие от ПЛИС типа CPLD функциональные блоки FPGA имеют другую организацию и логические возможности, а трассировочные ресурсы более разнообразны, т.к. состоят из линий разной длины и коммутаторов.

7.2.2. Логическая ячейка ПЛИС типа FPGA

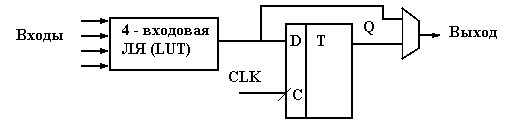

Конфигурируемый Логический блок (КЛБ) образован из нескольких секций–slice, которые в свою очередь состоят обычно из двух логических ячеек (ЛЯ).Логическая ячейка является базовым логическим элементом ПЛИС типа FPGA(рис.7.9).Она состоит из 4–6 входовой (в зависимости от типа FPGA) схемы, выполняющей логическую функцию– логической таблицы (ЛТ,ЛУТ) по английски– LUT–Luc Up Table), реализуемую с помощью постоянного запоминающего устройства( ПЗУ), D–триггера (DFF–D–Flip Flop), дополнительной управляющей логики и схемы ускорения переноса,используемой при построении сумматоров. Часто для всей логической ячейки используется то же наименование ЛУТ (LUT) как и для логисекой таблицы.

Рис. 7.9. Упрощенная структура четырехвходовой логической ячейки

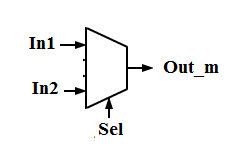

Обычно, как уже отмечалось, логическая функция ячейки ПЛИС типа FPGA реализуется таблично с помощью Постоянного Запоминающего Устройства( ПЗУ). ПЗУ после записи хранит записанную в него информацию. Каждому информационному слову сопоставлен его адрес. C помощью ПЗУ емкостью в 16 одноразрядных слов (16 х 1) можно реализовать любую булевскую функцию от четырех аргументов, записав в ПЗУ таблицу истинности этой функции, а при обращении к ПЗУ в качестве адреса использовать набор значений аргументов( четырехразрядный вектор или четырехразрядное двоичное число. В качестве примера в табл.7..1 представлена таблица истинности логической функции мультиплексора 2–1, имеющего три входа: in1, in2 и sel и один выход– out_m (рис.7.10, а также см.гл.3, раздел мультиплексор). При sel=0 мультиплексор пропускает на выход сигнал с входа in1, а при sel=1 с входа in2.

Рис. 7.10. УГО мультиплексора 2-1(ANSI)

Эта функция реализуется при занесении в ПЗУ ЛЯ емкостью 16 х 1 соответствующей табл.7..1 информации. Старший разряд адреса, обозначенный как Х4 в данном случае, при реализации функции трех аргументов с помощью ПЗУ с четырехразрядным адресом, не задействован и равен 0, что позволяет обращаться только к первым восьми ячейкам ПЗУ. Например мультиплексор 2-1 должен передавать на выход out_m значение сигнала 1 при in1=1, in2=0 и управляющем сигнале sel=0.

Соответственно комбинация 0100 рассматриваемая как номер строки табл.7.1 или как адрес ячейки ПЗУ дает 1. Помимо настройки на выполнение основной функции – четырехвходового логического элемента, логическая ячейка может настраиваться при программировании ПЛИС на выполнение другой функции, например 16 разрядного регистра сдвига. ПЗУ в этом варианте настройки ЛЯ используется по прямому назначению как ЗУ.

Таблица 7.1. Реализация логической функции мультиплексора 2–1.с помощью ПЗУ 16х1

| Значения входных сигналов, которые формируют адрес ячейки памяти X4 in1 in2 sel | Содержимое ячейки определяет значение выхода out_m |

| 0 0 0 0 | 0 |

| 0 0 0 1 | 0 |

| 0 0 1 0 | 0 |

| 0 0 1 1 | 0 |

| 0 1 0 0 | 1 |

| 0 1 0 1 | 0 |

| 0 1 1 0 | 1 |

| 0 1 1 1 | 1 |

В логической ячейке используются программируемые D–триггеры (рис. 7.9). При программировании ПЛИС можно задать различные режимы работы такого триггера, такие как триггер–защелка(D–Latch),синхронный D–триггер(FD), D–триггер с начальным сбросом (FDR) или начальной установкой (FDS), с записью по фронту или спаду синхросигнала, с разрешением(FDE) записи и т.п. Как уже отмечалось, пара ЛЯ обьединяется в секцию(slice), где также имеются узлы ускорения переноса, позволяющие ускорить и упростить реализацию арифметических операций. На рис.7.11 дано упрощенное представление секции, состоящей из двух ЛЯ.

Задание 2. Проект логической функции на LUT4 FPGA.

Используя пользовательские блоки DEEDS в библиотеке FPGA (см. Каталог SEXEM_LIB_DEEDS) спроектируйте и проверьте проект логической функции(ниже опреации обозначены так:&-и, не, | или)

№ Логическая функция

1. Y = A & B & C | D

2. Y = A & B & C | D

3. Y = A | B & C | D

4 Y = A & B| C | D

5 Y = A & B & C & D

6 Y = A & B & C | D

7 Y = A & B & C | D

8 Y = A& B & C | D

9 Y = A& B& C | D

10 Y = A& B& C & D

11. Y = A + B & C | D

12. Y = A & B & C + D

13. Y = A + B + C | D

14 Y = A & B| C | D

`15 Y = A & B & C xor D

16 Y = A xor B & C | D

17 Y = A nor B & C | D

18 Y = A& B & C xor D

19 Y = A nor B& C | D

20 Y = A xor B& C & D

21 Y = A & B & C xor D

22 Y = A xor B & C | D

23 Y = A nor B & C | D

24 Y = A& B & C xor D

25 Y = A nor B& C | D

26 Y = A xor B& C & D

Приложение 7.1.

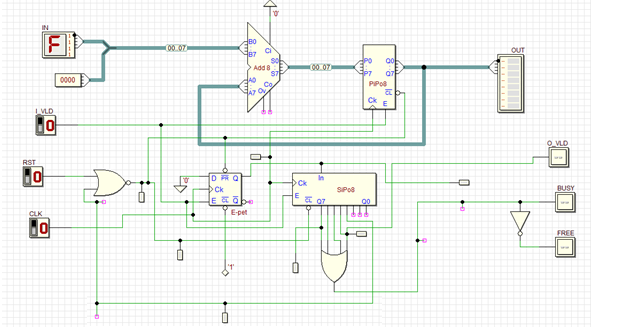

Примеры последовательной и параллельной реализации и моделирования устройства сложения четырех четырехразрядных чисел.

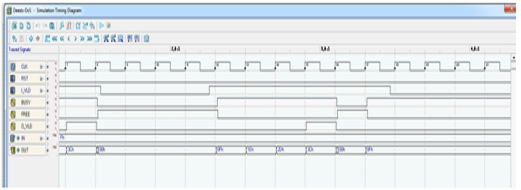

Последовательный вариант(в устройстве управления вырабатываются сигналы : input and output valid, busy and free)

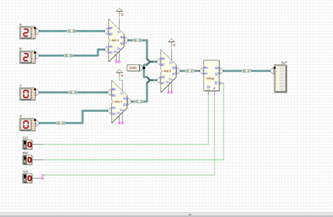

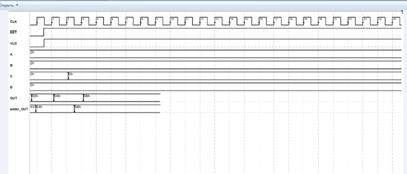

Параллельная реализация устройства(дополнительные сигналы: input and output valid)

СПИСОК РЕКОМЕНДУЕМОЙ ЛИТЕРАТУРЫ

Основная

1.https://www.digitalelectronicsdeeds.com Официальный сайт разработчиков система моделирования Deeds

2.https://www.digitalelectronicsdeeds.com/demos/demopage_comb.html

На сайте представлены примеры проектов с пояснениями.

3. https://www.digitalelectronicsdeeds.com/learningmaterials/labtopics.html

Представлены англоязычные описания нескольких десятков лабораторных работ по разделам схемотехники, теории автоматов и микропроцессорных систем.

4.Новиков Ю.В. Введение в цифровую схемотехнику. Учебное пособие.

–М: Бином. 2007.

5.Харрис Д.М., Харрис С.Л . Цифровая схемотехника и архитектура компьютера. Электронная версия книги может быть загружена с сайта http://easyelectronics.ru/files/Book/digital-design-and-computer-architecture-russian-translation.pdf

6. Угрюмов Е.П. Цифровая схемотехника. Учебное пособие. Издание 3. СПБ.:BXB Петербург, 2010.

Дополнительная

7.Потемкин И.С. Функциональные узлы цифровой автоматики.

–М.: Энергоатомиздат,1988.

8. Петровский И.И. и др. - Логические ИС Кр1533, Кр1554. Справочник.

–М.:БИНОМ, 1993.

9. Поляков А.К. ЯЗЫКИ VHDL и VERILOG В ПРОЕКТИРОВАНИИ ЦИФРОВОЙ АППАРАТУРЫ НА ПЛИС.–М.: Изд.Дом МЭИ,2012.