Лабораторная работа 3 Разработка схем цос на плис типа fpga

Скачать 420.5 Kb. Скачать 420.5 Kb.

|

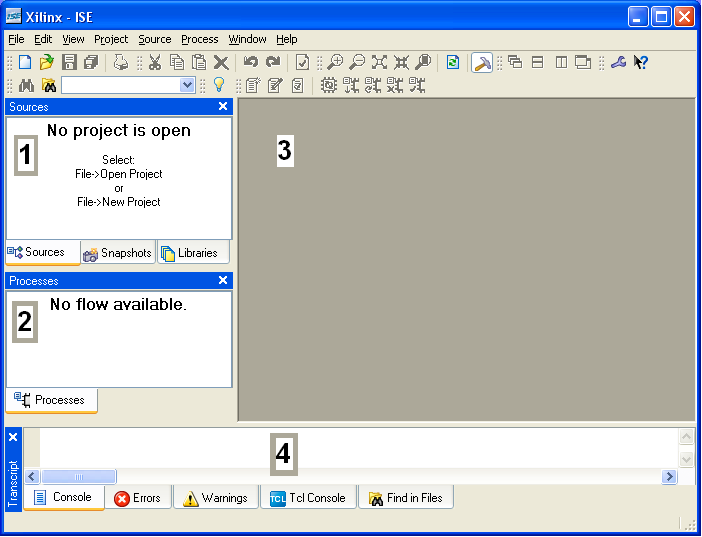

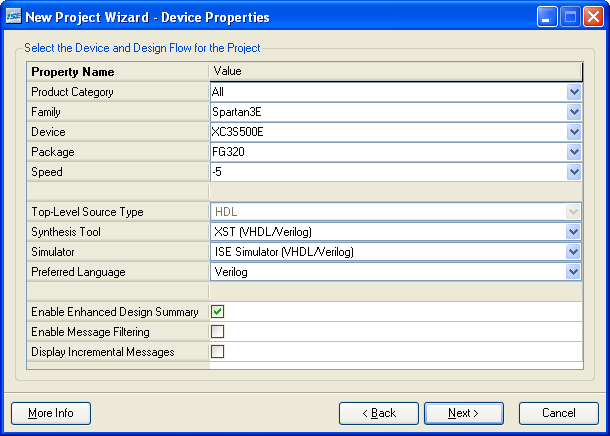

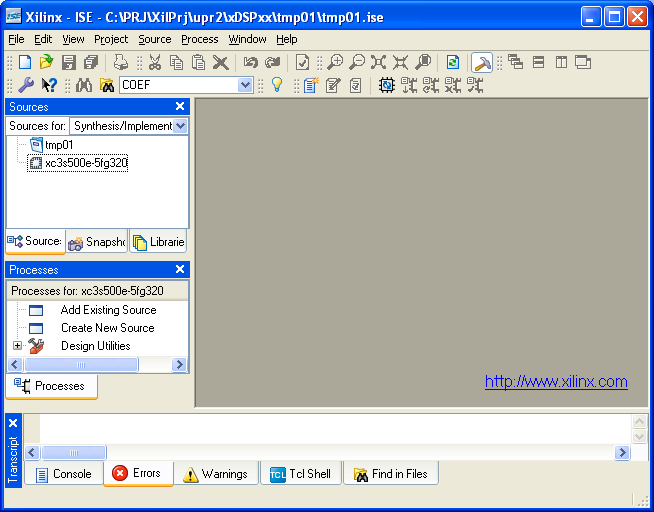

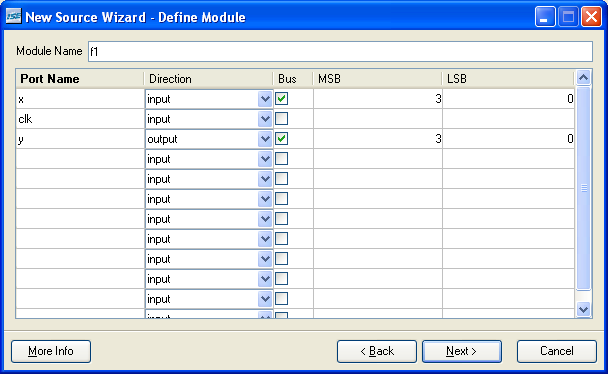

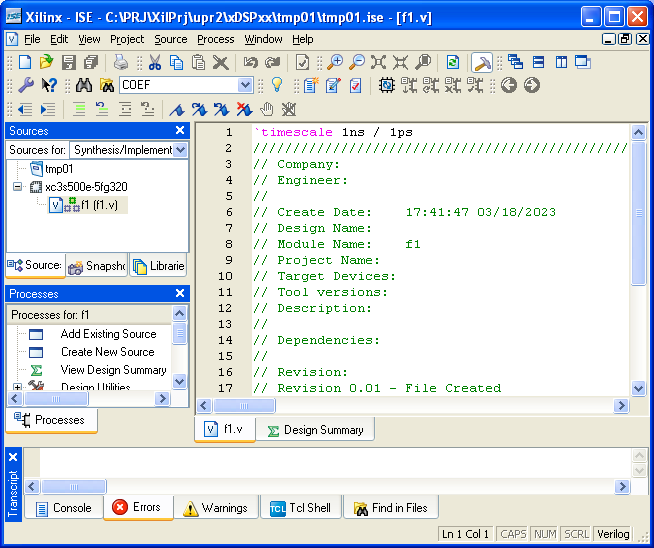

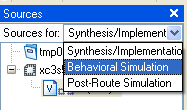

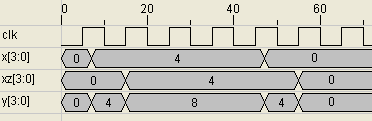

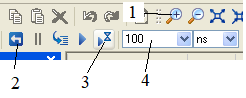

Лабораторная работа № 3Разработка схем ЦОС на ПЛИС типа FPGA.Цель работы: изучение основных принципов построения схем цифровой обработки сигналов на ПЛИС типа FPGA, а также изучение основных приемов работы с системой проектирования ISE. Основные приемы выполнения работы. Основные методы работы в системе проектирования ISEПрограммные средства ISE представляют собой систему сквозного проектирования, которая реализует все этапы создания цифрового устройства на базе ПЛИС, включая программирование кристалла: разработка проекта, синтез, моделирование, трассировка и загрузка в кристалл. Управляющая оболочка пакета ISE Навигатор проекта (Project Navigator) управляет всеми процессами проектирования. Запуск всех необходимых программных модулей пакета осуществляется непосредственно в среде Навигатора проекта (см. рис. 1).  Рис. 1 Основное окно Навигатора проекта помимо стандартных элементов управления (основного меню и оперативной панели управления) содержит четыре встроенных окна. В окне исходных модулей Sources (окно 1) отображается иерархическая структура проекта. Каждый тип модуля имеет соответствующее графическое обозначение - пиктограмму. Окно процессов Processes (окно 2) показывает стадии обработки выделенного исходного модуля. Последовательность и содержание этапов определяется типом исходного модуля. В этом же окне указывается информация о дополнительных инструментах, которые могут быть использованы на каждом этапе. Рабочее окно 3 располагается справа. Окно консольных сообщений (окно 4) предназначено для вывода информации о ходе работы с проектом. В процессе работы можно выделить следующие этапы: создание нового проекта (выбор семейства и типа ПЛИС, а также средств синтеза); подготовка описания проектируемого устройства в схемотехнической, алгоритмической или текстовой форме; функциональное моделирование; синтез устройства и др. Исходная информация о проектируемом устройстве может быть представлена в виде принципиальных схем, описаний на языке HDL, диаграмм состояний и библиотек пользователя. Функциональное моделирование устройства производится без учета реальных значений задержек и позволяет проконтролировать соответствие выходных сигналов алгоритмам работы проектируемого устройства. При обнаружении ошибок на любом из этапов (например, логических ошибок на этапе функционального моделирования или при получении неудовлетворительных результатов временного моделирования) следует вернуться на стадию разработки исходных описаний проекта, внести необходимые изменения и повторить последующие этапы. Создание нового проекта. Создание нового проекта инициируется последовательностью команд File New Project, выполняемой из основного меню. При выборе этого пункта меню открывается диалоговая панель, в которой разработчик должен указать имя и расположение проекта на жестком диске. В этом же окне надо также указать тип модуля верхнего уровня, например, HDL. После нажатия клавиши Next в следующем окне надо выбрать семейство ПЛИС, тип кристалла и средства синтеза устройства. Пример заполнения этого окна показан на рис. 2. После ввода необходимых данных нажимается клавиша Next, в последующих окнах можно не задавать никаких данных, после ввода последнего окна в окне исходных модулей Sources появится пиктограмма проекта (см. рис. 3). Создание нового модуля на языке VHDL. Для создания нового модуля можно в Sources щелкнуть правой клавишей мыши на строке проекта (эта строка содержит наименование выбранной микросхемы), а затем в появившемся контекстном меню выбрать New Source (тот же результат можно получить из основного меню, если выполнить: Project New Source).  Рис. 2  Рис. 3 В левой части появившегося окна выбирается тип модуля, допустим это Verilog Module – модуль на языке Verilog, в правой части в строке File Name задается имя файла (например, f1) и нажимается клавиша Next. В новом окне задаются имена входных и выходных сигналов, тип контакта (вход, выход или двунаправленный) и их разрядность, если задается многоразрядный сигнал, то устанавливается флажок Bus. Пример заполнения показан на рис. 4.  Рис. 4 На последнем рисунке задаются внешние сигналы для четырехразрядного фильтра, работающего по синхросигналу clk. После нажатия клавиши Next появляется последнее окно, в котором нажимается клавиша Finish. В результате в окне исходных модулей Sources появляется новый элемент (см. рис. 5). Если убрать ненужные комментарии и добавить необходимое описание, то получится необходимый текст исходного модуля, например: `timescale 1ns / 1ps module f1(x, clk, y); input [3:0] x; input clk; output wire [3:0] y; reg [3:0] xz=0; always @ (posedge clk) begin xz <= x; end assign y = x + xz; endmodule  Рис. 5 После внесения необходимых изменений в текст описания выполняется проверка проекта. Для этого в окне исходных модулей Sources надо выделить нужный файл (в данном случае – f1), а затем в окне Processes надо раскрыть пункт Synthesize – XST. В открывшемся перечне следует выбрать Check Syntax. Если в результате выполнения этого пункта возникли ошибки, их надо устранить и повторить проверку еще раз. Далее может быть выполнено моделирование. Для задания входных сигналов создается тестовый модуль. Для этого надо щелкнуть правой клавишей мыши на строке исходного модуля f1, а затем в появившемся контекстном меню надо выбрать New Source. В левой части появившегося окна выбирается тип модуля – Verilog Test Fixture, в правой части в строке File Name задается имя файла (например, tb1) и нажимается клавиша Next. В следующих окнах указывается связь с исходным модулем и другая информация, здесь можно не выполнять никаких действий. В созданном окне выполняются необходимые изменения. Пример тестового модуля приведен ниже. `timescale 1ns / 1ps //тестовый модуль module tb1_v; reg [3:0] x=0; reg clk; wire [3:0] y; f1 u1(.x(x),.clk(clk),.y(y)); initial begin forever begin clk = 1'b0; #5; clk = 1'b1; #5; end end initial begin assign x = 4'b0000; #7; assign x = 4'b0100; #40; assign x = 4'b0000; #20; end endmodule Если при выполнении выше указанных действий в окне исходных модулей Sources по умолчанию был активизирован режим Synthesis/Implementation, для перехода к моделированию надо выбрать режим Behavioral Simulation (см. рис. 6).  Рис. 6 Моделирование будет выполняться в программе ISE Simulator, эта программа задается при создании проекта (см. рис. 2, поле Simulator). Если при создании проекта была выбрана другая программа моделирования, то в окне исходных модулей Sources необходимо щелкнуть правой клавишей мыши на строке xc3s500e-5fg320, а затем в появившемся контекстном меню выбрать Properties. После этого в окне Project Properties в поле Simulator надо выбрать ISE Simulator. Для запуска моделирования в окне Sources выделяется файл tb1, а затем в окне Processes надо дважды щелкнуть левой клавишей мыши на строке Simulate Behavioral Model.  Рис. 7 При необходимости, если данная строка отсутствует, надо выбрать закладку Processes и раскрыть пункт Xilinx ISE Simulator. Пример результатов моделирования приведен на рис. 8.  Рис. 8 На рис. 9 показаны часто используемые кнопки. Кнопка 1 позволяет увеличить масштаб диаграммы, кнопка 2 – Restart (подготовка к перезапуску). Кнопка 3 инициирует моделирование в течение времени, указанного в поле 4.  Рис. 9. Кнопки управления моделированием При необходимости, если нужный сигнал отсутствует, в окне Processes надо выбрать закладку Hierarchy и перетащить мышкой требуемый сигнал на диаграмму. После этого можно повторить моделирование последовательным нажатием кнопок 2 и 3 на рис. 9. Порядок выполнения работы1. Разработать нерекурсивный фильтр на ПЛИС на языке Verilog, разрядность данных - 8. Определить реакцию на единичный импульс и единичную последовательность. Определить реакцию фильтра на заданный сигнал.

2. Разработать нерекурсивный фильтр на ПЛИС на языке Verilog, разрядность данных - 8. Определить реакцию на единичный импульс и единичную последовательность. Определить реакцию фильтра на заданный сигнал.

3. Разработать рекурсивный фильтр первого порядка на ПЛИС на языке Verilog, разрядность данных - 8. Определить реакцию на единичный импульс и единичную последовательность. Определить реакцию фильтра на заданный сигнал.

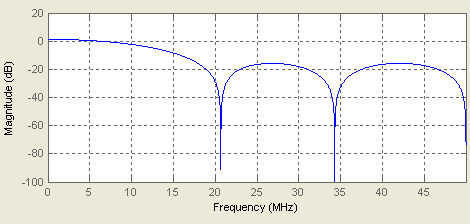

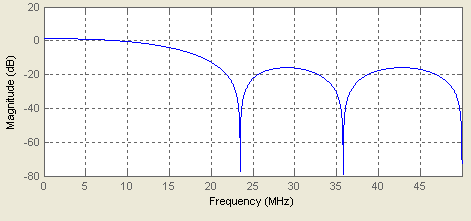

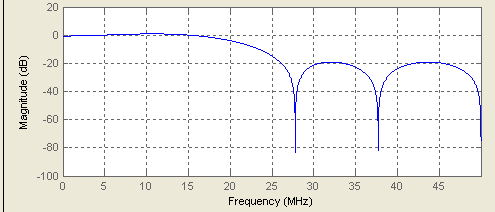

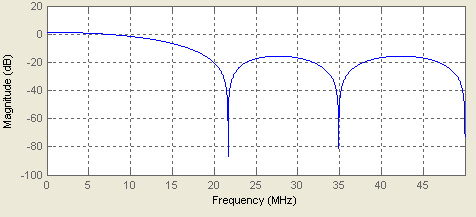

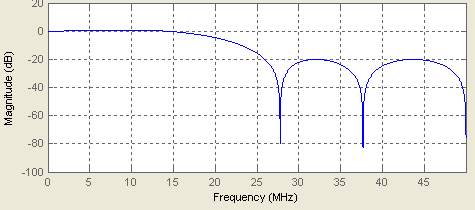

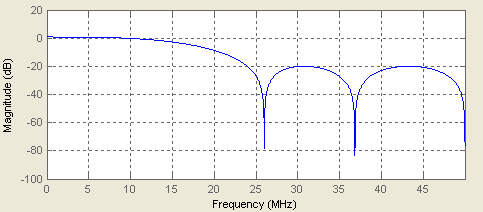

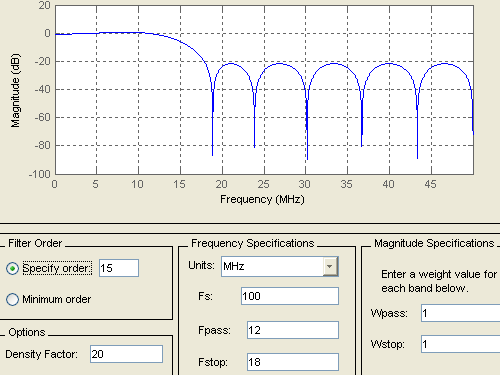

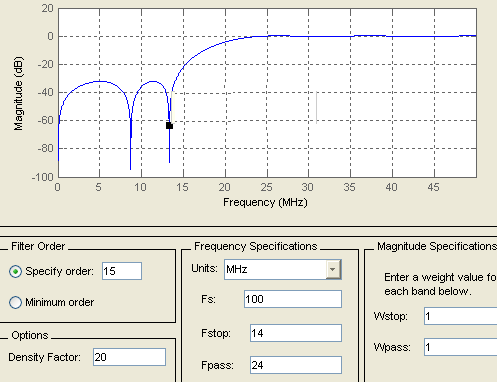

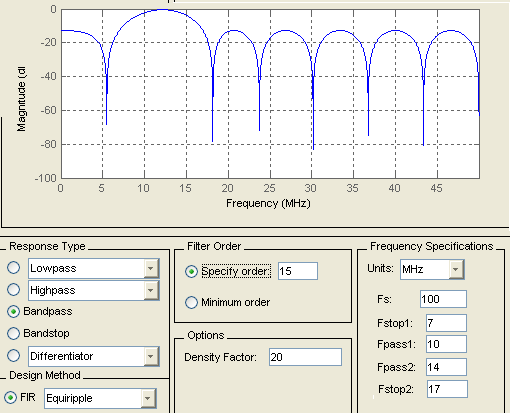

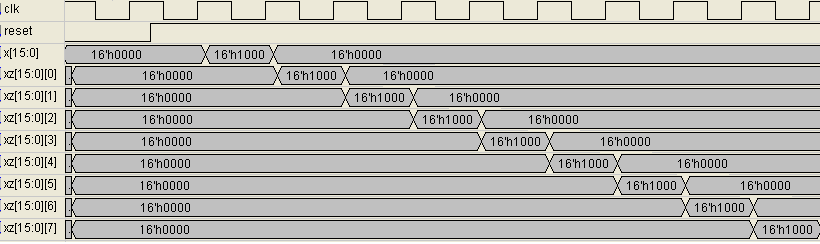

Изменяя a1 и b0 сделать выводы о влиянии этих коэффициентов на работу фильтра. Задать a1 = -0.5, b0 = 0.5, b1 = 0.0. Определить реакцию на единичный импульс, единичную последовательность и прямоугольный импульс различной длительности. 4. Разработать нерекурсивный фильтр нижних частот. Частотные характеристики фильтра задаются в fdatool. Определить реакцию на единичный импульс. Проверить частотные характеристики фильтра. Варианты 1,8 Частота дискретизации Fs=100 Мгц, частота пропускания Fpass=9 Мгц, частота подавления Fstop=18 Мгц, фильтр имеет 7(8) коэффициентов. -0.024458211392255642 0.1385734715904797 0.20432647461212372 0.26273795244659287 0.26273795244659287 0.20432647461212372 0.1385734715904797 -0.024458211392255642  Варианты 2,7 Частота дискретизации Fs=100 Мгц, частота пропускания Fpass=12 Мгц, частота подавления Fstop=21 Мгц, фильтр имеет 7(8) коэффициентов. -0.060775036032251303 0.094885041928497574 0.22177142159044932 0.32426367443483128 0.32426367443483128 0.22177142159044932 0.094885041928497574 -0.060775036032251303  Варианты 3,10 Частота дискретизации Fs=100 Мгц, частота пропускания Fpass=17Мгц, частота подавления Fstop=28 Мгц, фильтр имеет 7(8) коэффициентов. -0.1029966339098423 -0.022633193118672734 0.18956286604654826 0.40142756341436198 0.40142756341436198 0.18956286604654826 -0.022633193118672734 -0.1029966339098423  Варианты 4,9 Частота дискретизации Fs=100 Мгц, частота пропускания Fpass=10 Мгц, частота подавления Fstop=19 Мгц, фильтр имеет 7(8) коэффициентов. -0.038645752774681554 0.12608229298259332 0.21239603218007624 0.28323565416535013 0.28323565416535013 0.21239603218007624 0.12608229298259332 -0.038645752774681554  Варианты 5,12 Частота дискретизации Fs=100 Мгц, частота пропускания Fpass=16 Мгц, частота подавления Fstop=26 Мгц, фильтр имеет 7(8) коэффициентов. -0.024458211392255642 0.1385734715904797 0.20432647461212372 0.26273795244659287 0.26273795244659287 0.20432647461212372 0.1385734715904797 -0.024458211392255642  Варианты 6,11 Частота дискретизации Fs=100 Мгц, частота пропускания Fpass=12 Мгц, частота подавления Fstop=24 Мгц, фильтр имеет 7(8) коэффициентов. -0.058116432908280218 0.049430803026937656 0.20936548340988409 0.34953467616723588 0.34953467616723588 0.20936548340988409 0.049430803026937656 -0.058116432908280218  5. Разработать нерекурсивный фильтр нижних частот. Частотные характеристики фильтра задаются в fdatool. Определить реакцию на единичный импульс. Проверить частотные характеристики фильтра. Варианты 1-12 Частота дискретизации Fs=100 Мгц, частота пропускания Fpass=12Мгц, частота подавления Fstop=18 Мгц, фильтр имеет 15(16) коэффициентов. 0.037059570118627934 -0.02307320394269835 -0.052956774526219129 -0.062069563249109824 -0.017519265429228749 0.083952385419489794 0.20538459563162348 0.28813463217040336 0.28813463217040336 0.20538459563162348 0.083952385419489794 -0.017519265429228749 -0.062069563249109824 -0.052956774526219129 -0.02307320394269835 0.037059570118627934  6. Разработать нерекурсивный фильтр высоких частот. Частотные характеристики фильтра задаются в fdatool. Определить реакцию на единичный импульс. Проверить частотные характеристики фильтра. Варианты 1-12 Частота дискретизации Fs=100 Мгц, частота подавления Fstop=14 Мгц, частота пропускания Fpass=24Мгц, фильтр имеет 15(16) коэффициентов. 0.017425690480098226 -0.0060410075547963783 -0.037948478513453787 -0.03481532541025964 0.036865329587026013 0.11464314902818995 0.045582703094050298 -0.52418449504105036 0.52418449504105036 -0.045582703094050298 -0.11464314902818995 -0.036865329587026013 0.03481532541025964 0.037948478513453787 0.0060410075547963783 -0.017425690480098226  7. Разработать полосовой фильтр. Частотные характеристики фильтра задаются в fdatool. Определить реакцию на единичный импульс. Проверить частотные характеристики фильтра. Варианты 1-12  0.11624549922712731 -0.020790206504145009 -0.073891791891143851 -0.1177347608815346 -0.11345647456159967 -0.050813727213856463 0.03987313582326811 0.10544954752035379 0.10544954752035379 0.03987313582326811 -0.050813727213856463 -0.11345647456159967 -0.1177347608815346 -0.073891791891143851 -0.020790206504145009 0.11624549922712731 ПРИЛОЖЕНИЕ Пример схемы на языке Verilog: Y(n) = 0.75*x(n) + 0.25*x(n-1)`timescale 1ns / 1ps module f2(x, clk, y); // внешние сигналы input [7:0] x; input clk; output reg [7:0] y; reg [7:0] x75=0,xz25b=0,xz=0; // внутренние wire [7:0] x25,x5,xz25; // сигналы always @ (posedge clk) begin x75 <= x5+x25; // 0.75*x(n) xz25b <= xz25; // 0.25*x(n-1) y <= x75 + xz25b; xz <= x; end assign x5 = {x[7],x[7:1]}; // 0.5*x(n) assign x25 = {x[7],x[7],x[7:2]}; // 0.25*x(n) assign xz25 = {xz[7],xz[7],xz[7:2]}; endmodule Нерекурсивный фильтр. Входной буфер reg signed [15:0] xz [0 : 7]; // двумерный массив xz always @ (posedge clk ) // 8 16-разрядных чисел if (!in_reset_n) // сброс xz[0], xz[1],…, xz[7] for (i = 0; i < 8; i = i + 8'd1) // xz[i] <= #1 0; else // сдвиг xz[1]<-xz[0], xz[2]<-xz[1],…, xz[7]<-xz[6], begin // xz[0] <- x; выполняется одновременно for (i = 1; i < 8; i = i + 8'd1) xz[i] <= xz[i - 1]; // xz [0] <= x; // end  Нерекурсивный фильтр. Задание коэффициентов wire signed [20:0] b[0 : 3]; // двумерный массив assign b[0] = 21'h1f58fb; assign b[1] = 21'h1c3fd; assign b[2] = 21'h3622b; assign b[3] = 21'h4ae1a; Вычисление yn Фильтр имеет симметричные коэффициенты: b0=bM-1, b1=bM-2, … reg signed [15:0] xz [0 : 7]; // двумерный массив xz reg signed [16:0] xzsum[0 : 3]; // сумм для сим коэф-тов reg signed [37:0] bxx[0 : 3]; // Рез умнож на коэфф-ты reg signed [38:0] s0[0 : 1]; // частичные суммы reg signed [39:0] s1; // always @ (posedge clk ) for (i = 0; i < 4; i = i + 8'd1) begin xzsum[i] <= #1 xz[i] + xz[7 - i]; bxx[i] <= #1 xzsum[i] * b[i]; end // xzsum[0] <= #1 xz[0]+xz[7]; xzsum[1] <= #1 xz[1]+xz[6]; // xzsum[2] <= #1 xz[2]+xz[5]; xzsum[3] <= #1 xz[3]+xz[4]; // bxx[0] <= #1 xzsum[0]*b[0]; bxx[1] <= #1 xzsum[1]*b[1]; // bxx[2] <= #1 xzsum[2]*b[2]; bxx[3] <= #1 xzsum[3]*b[3]; s0[0] <= bxx[0] + bxx[1]; s0[1] <= bxx[2] + bxx[3]; s1 <= s0[0] + s0[1]; // Чтение входного сигнала из файла reg signed [15:0] roms [100:0]; initial $readmemh("c:/PRJ/…sin01.txt", roms); reg [15:0] addr2=0; reg signed [15:0] rs=0, qsin=0; always @ (posedge clk) begin if ((reset == 1'b0) || (addr2 == 16'd099)) addr2 <= 9'b000000000; else addr2 <= addr2 + 9'b000000001; rs <= (roms[addr2]); qsin <= rs; x <= qsin; // end Запись результатов в файл integer handle1,i,i0; initial begin handle1 = $fopen("Z:/nerfxx/… b11.txt"); i0=0; #2000 for (i = 0; i < 1150; i = i + 1) begin // $fwrite(handle1," %d %d %d %d ", i, x, y, f1.b[i0]); i0=i0+1; if(i0 > 3)i0=0; $fwrite(handle1,"\n"); #10; end #10; $fclose(handle1); end Заголовок модуля `timescale 1ns / 1ps // КИХ фильтр module f07u ( output [15:0] y, // выход данных input clk, in_reset_n,// input signed [15:0] x // вход данных, ); Включение компонента в проектируемое устройство // .наименование контакта(имя сигнала) f07u f1 (.in_reset_n(reset), .clk(clk), .x(x), .y(y)); |