Реакции процессора на внешний сигнал запроса прерывания и сигнал готовности подсистем. Отчёт_3_ЛР_Фомин (1). Лабораторная работа 3. Реакции процессора на внешний сигнал запроса прерывания и сигнал готовности подсистем Фомин Е. Н. 19в2

Скачать 1.13 Mb. Скачать 1.13 Mb.

|

|

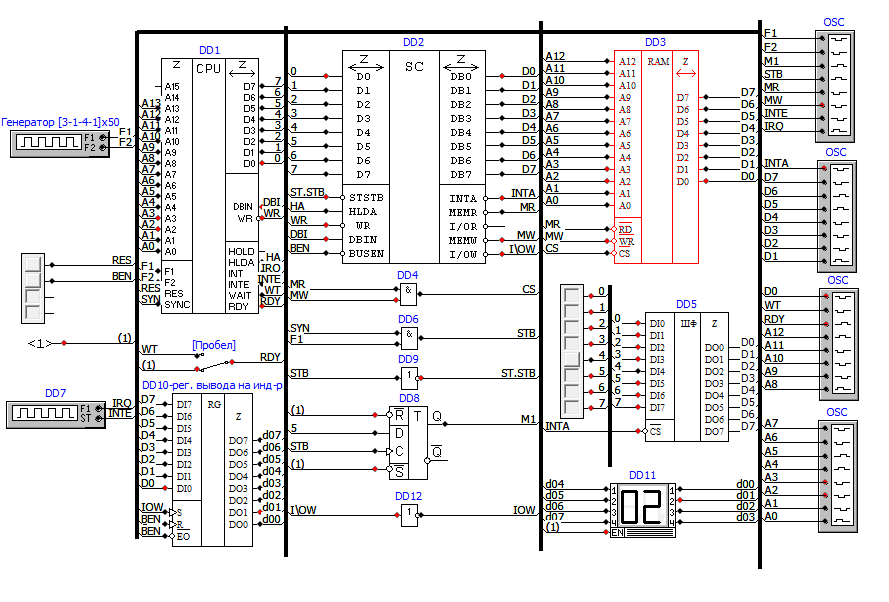

НИЖЕГОРОДСКИЙ ГОСУДАРСТВЕННЫЙ ТЕХНИЧЕСКИЙ УНИВЕРСИТЕТ Лабораторная работа №3. Реакции процессора на внешний сигнал запроса прерывания и сигнал готовности подсистем Выполнил: Фомин Е.Н. 19-В-2 Принял: Киселев Ю.Н. Н.Новгород 2021 г. Цель работы Изучение реакции процессора на внешние сигналы прерывания INT и READY (готовность подсистем) путем получения и исследование временных диаграмм, которые формирует процессор КР580ВМ80А при выполнении перехода на программу прерывания, анализ данных на ШД и ША в циклах перехода; исследование реакции на сигнал готовности подсистем Ready. Задача Написать программу, которая позволит исследовать реакцию процессора на внешний сигнал прерывания; произвести наблюдение и фиксацию временных диаграмм сигналов управления, сигналов шин данных и адреса в процессорных циклах с помощью логических анализаторов; снятие битовой информации по осциллограммам; исследование временных диаграмм, которые процессор формирует при получении внешних сигналов прерывания и сигнала готовности подсистем.  Схема Микро-ЭВМ Листинг Мнемоника LXI SP,0100h MVI A,01h OUT 01h EI NOP MVI A,03h OUT 01h JMP 0003h SKIP 28h MVI A,02h OUT 01h RET

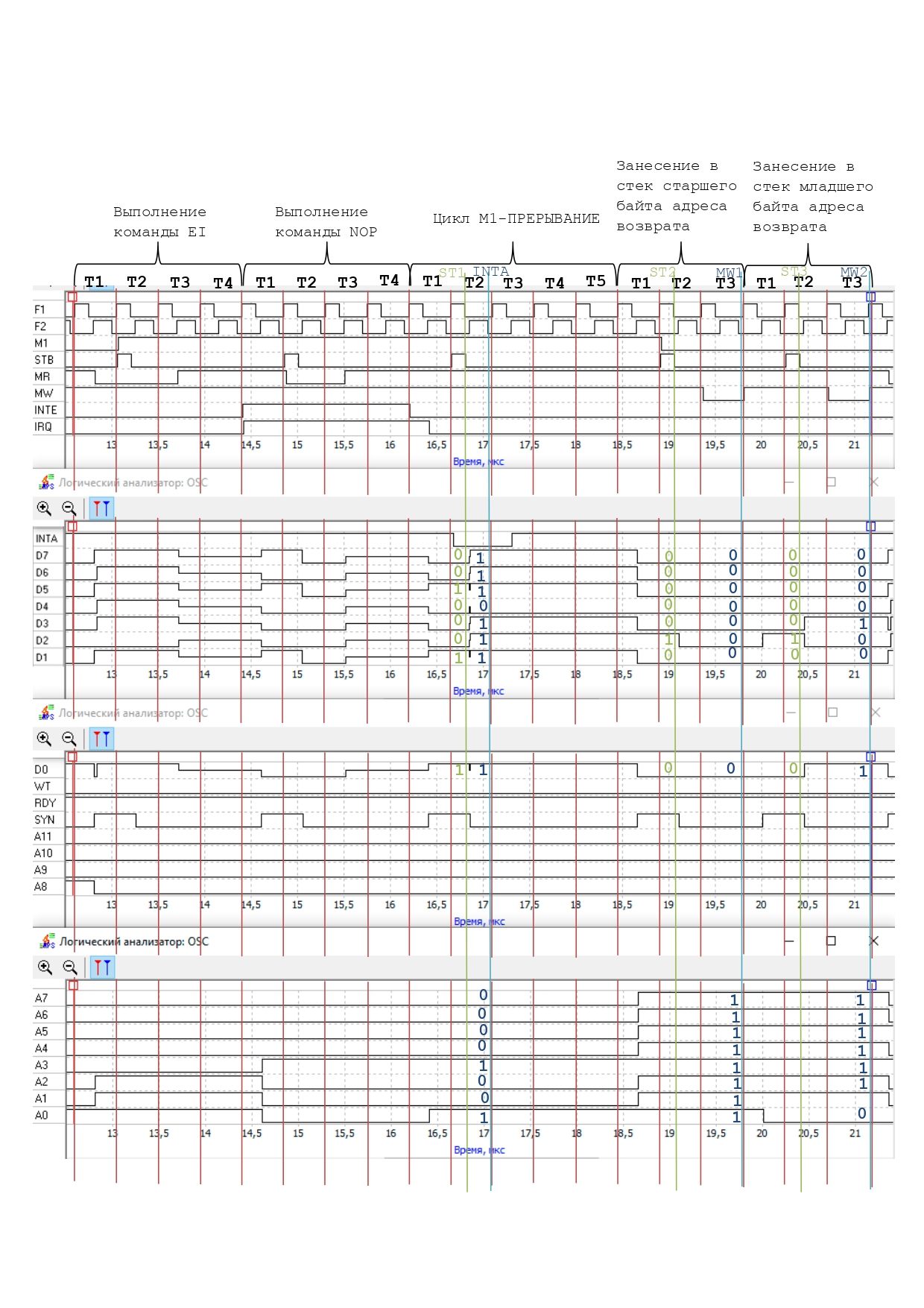

В данном случае можно не использовать команду JMP, так как подпрограмма занимает только 5 байт памяти и не использует адреса 0030h и больше, которые относятся к RST 6. Если подпрограмма будет больше, то необходимо её хранить на участках памяти, не связанных с командами RST, и использовать команду JMP в ячейке памяти, в которую позволяет перейти команда RST (например, для RST 5 – ячейка с адресом 0028h). Чтобы задать вектор прерывания RST 5 был использован элемент «Блок 8», на котором задан КОП в двоичной системе счисления.  Цикл M1-прерывание состоит из 5 тактов: Т1 - сброс триггера INTE, выдача адреса следующей операции на ША; Т2 - формирование внешним устройством байта вектора; Т3 – процессор принимает байт вектора; Т4 – дешифрация команды; Т5 – подготовка адреса вершины стека. Занесение в стек старшего байта адреса возврата: Т1 – выдача на ША адреса вершины стека; Т2 – формирование нового адреса вершины стека; Т3 – занесение в стек старшего байта адреса возврата. Занесение в стек младшего байта адреса возврата: Т1 – выдача на ША адреса вершины стека; Т2 – формирование нового адреса вершины стека; Т3 – занесение в стек младшего байта адреса возврата. Результаты считывания данных с ШД

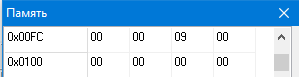

ST1 – Байт состояния цикла «Прерывание» INTA – Значение вектора прерывания, сформированного внешним устройством. ST2 – Запись в стек старшего байта регистра PC. MW1 – Старший байт адреса возврата. ST3 - Запись в стек младшего байта регистра PC. MW2 – Младший байт адреса возврата. Результаты считывания данных с ША

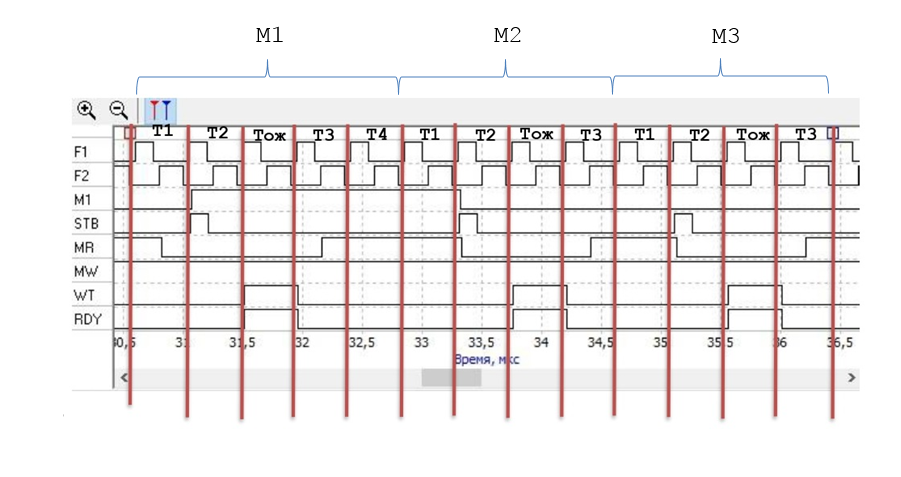

По адресу 11111111 (FFh) записан старший байт адреса. По адресу 11111110 (FEh) записан младший байт адреса.  В схеме для формирования сигнала на вход INT микропроцессора используется генератор одиночного импульса DD7, который получает сигнал запуска с выхода INTE (выход триггера разрешения прерывания) процессора. Генератор формирует выходной сигнал запроса прерывания с управляемой длительностью. Поскольку процессор устанавливает INTE в лог.1 после выполнения команды EI - разрешение прерывания, запрос прерывания появляется после выполнения этой команды. При поступлении запроса прерывания процессор завершает выполнение текущей команды и переходит к исполнению цикла M1 Прерывание. Реакция процессора на сигнал READY на примере команды RET  Введение такта ожидания увеличивает длительность сигнала обращения к памяти (регистрам). Также увеличивается длительность состояний адреса и сигналов управления. Это дает более благоприятные условия для чтения или записи содержимого ячейки памяти (регистра). Тем самым мы удовлетворяем требованиям более медленных устройств. Также учитывается задержка распространения сигналов от блока ЦП к конкретному узлу. В такте Т2 процессор проверяет значение сигналов на входах READY и HOLD. Так как сигналы WAIT и READY связаны и имеют значение 0, процессор вместо такта Т3 выполняет такты Т -ожидания готовности, проверяя в каждом такте состояние входа READY, а также выдает сигнал высокого уровня на линию WAIT, подтверждающий режим ожидания (переключение сигнала на линии WAIT осуществляется фронтом импульса F1). Во время анализа сигналов READY и HOLD в Тож WAIT=1=READY. Сигнал READY=1 предшествует спаду импульса F2, поэтому линия WAIT переводится в состояние низкого потенциала, и процессор переходит в состояние Т3. Таким образом, соединение линий READY и WAIT позволяет ввести один такт ожидания готовности в каждый цикл. Вывод В результате выполнения лабораторной работы были изучены реакции процессора на внешние сигналы прерывания INT и READY (готовность подсистем) путем получения и исследование временных диаграмм; проанализированы данные на ШД и ША в циклах перехода; исследованы реакции на сигнал готовности подсистем Ready. |