Лабораторная работа 6 автоматическая генерация топологии с языка высокого уровня счетчика с произвольным коэффициентом счета

Скачать 89.69 Kb. Скачать 89.69 Kb.

|

|

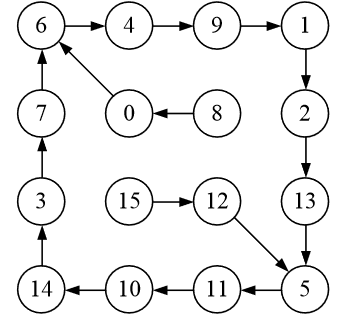

ЛАБОРАТОРНАЯ РАБОТА №6 АВТОМАТИЧЕСКАЯ ГЕНЕРАЦИЯ ТОПОЛОГИИ С ЯЗЫКА ВЫСОКОГО УРОВНЯ СЧЕТЧИКА С ПРОИЗВОЛЬНЫМ КОЭФФИЦИЕНТОМ СЧЕТА. Цель работы: необходимо разработать на вентильном уровне счетчик с произвольным коэффициентом счета согласно варианту. Написать структурное описания счетчика на языке высокого уровня (Verilog HDL). Произвести синтез топологии с языка высокого уровня. Подать тестовые воздействия для проверки правильности синтеза. Вариант 15 Исходные данные: Счетная последовательность №1:  Рисунок 1 - Счетная последовательность. Таблица 1 – Вариант задания

Cоставим входные и выходные функции с помощью карт Карно и соответствующих таблиц состояний для каждого из триггеров и минимизируем их. Для начала составим таблицу переходов состояний по нашей счетной последовательности: Таблица 2 - Таблица переходов состояний.

Составляем карты Карно.

Таблица 3 - Сигнал AJ.

Полученная функция:  Таблица 4 - Сигнал AK.

Полученная функция:

Таблица 5 - Сигнал BS.

Полученная функция:  . .Таблица 6 - Сигнал BR.

Полученная функция:  . .

Таблица 7 - Сигнал CJ.

Полученная функция:  . .Таблица 8 - Сигнал CK.

Полученная функция:

Таблица 9 - Сигнал DD.

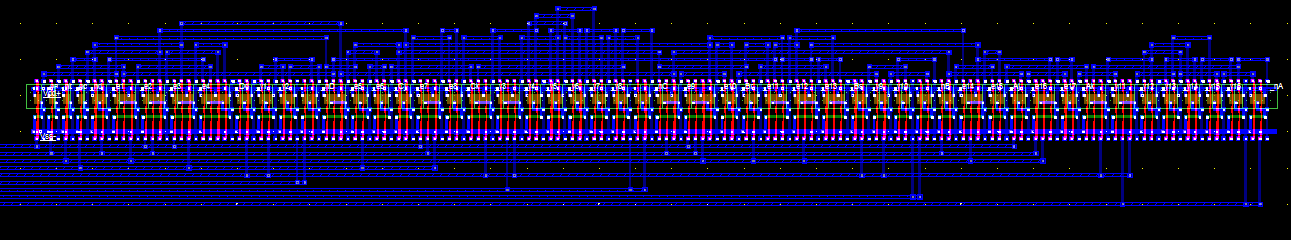

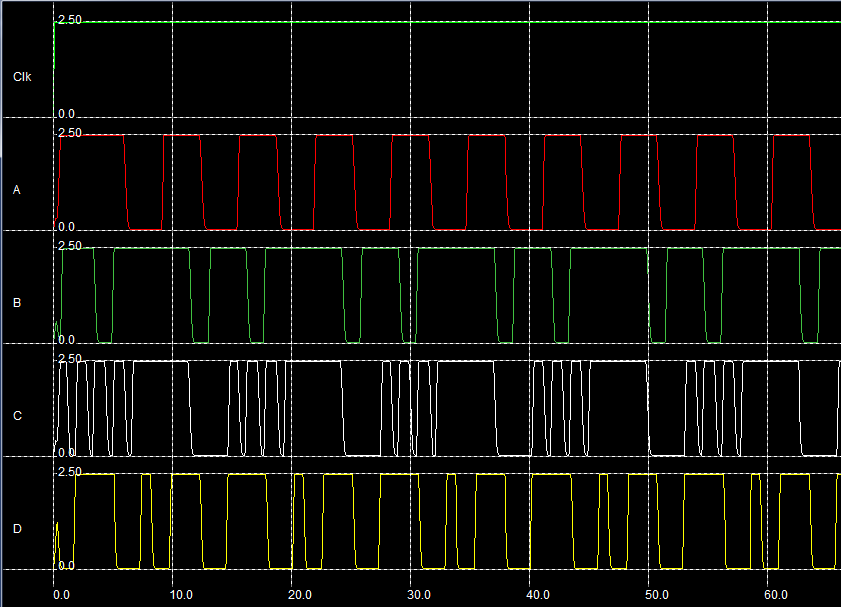

Полученная функция:  Опишем счетчик на языке Verilog: module counter(A, B, C, D, a, b, c, d, Clk); input Clk; input a; input b; input c; input d; output A; output B; output C; output D; wire e1, e2, e3, e4, e5, e6, e7, e8, e9, e10, e11, e12, e13, e14, e15, e16, e17; wire y1, y2, y3, y4, y5, y6, y7, y8, y9, y10, y11, y12, y13, y14, y15, y16; wire A, B, C, D, nA, nB, nC, nD, Dd, Cj, Ck, Br, Bs, Aj, Ak; //инверторы not (na, a); not (nb, b); not (nc, c); not (nd, d); //D-триггер 1 разряд nand (e1, nc, b); nand (e2, na, nb, c); nand (e3, a, b, nd); nand (e4, a, nc, d); nand (Dd, e1, e2, e3, e4); nand (y1, Dd, Clk); nand (y2, y1, Clk); nand (D, y1, nD); nand (nD, D, y2); //JK-триггер 2 разряд nand (e5, na, nb, nc); nand (e6, na, d); nand (Cj, e5, e6); nand (e7, na, nd); nand (e8, a, b, d); nand (Ck, e7, e8); nand (y3, Cj, nC, Clk); nand (y4, Ck, C, Clk); nand (y5, y6, y3); nand (y6, y5, y4); nand (y7, y3, y5); nand (y8, y4, y6); nand (C, y7, nC); nand (nC, y8, C); //RS-триггер 3 разряд nand (e9, na, b, nc); nand (e10, a, b, c, nd); nand (Br, e9, e10); nand (e11, na, c); nand (e12, na, nb, nd); nand (e13, nb, c, nd); nand (Bs, e11, e12, e13); nand (y9, Bs, Clk); nand (y10, Br, Clk); nand (B, nB, y9); nand (nB, B, y10); //JK-триггер 1 разряд nand (e14, b, nc); nand (e15, nb, c, nd); nand (Aj, e14, e15); nand (e16, a, nc); nand (e17, b, c, nd); nand (Ak, e16, e17); nand (y11, Aj, nA, Clk); nand (y12, Ak, A, Clk); nand (y13, y14, y11); nand (y14, y13, y12); nand (y15, y11, y13); nand (y16, y12, y14); nand (A, y15, nA); nand (nA, y16, A); endmodule Скомпилируем написанный код в программе Microwind и получим топологию нашего счетчика:  Рисунок 2 - Топология счетчика. Запустим моделирование и проверим правильность работы счетчика:  Рисунок 3 - Результаты моделирования. Вывод: Такой способ проектирования показал себя очень удобным с той точки зрения, что собирать схему вручную не нужно, достаточно написать код для нее. При этой схема получится без ошибок, а ошибки, допущенные в коде, программа сама поможет исправить, указав на них при проектировании. | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||