|

Лекции по схемотехнике ЭВМ. Лекция Базовые понятия цифровой электроники версия для печати и pda в лекции рассказывается о базовых терминах цифровой электроники, о цифровых сигналах, об уровнях представления цифровых устройств, об их электрических и временных параметрах

15. Лекция: Разработка более сложных цифровых устройств: версия для печати и PDA

В лекции подробно рассматриваются примеры разработки сравнительно сложных цифровых устройств — логического анализатора и генератора аналоговых сигналов, начиная от анализа функций устройств и выделения основных узлов до проектирования принципиальных схем узлов и устройства в целом.

|

|

|

| Разработка логического анализатора

Логический анализатор — это контрольно-измерительный прибор, предназначенный для запоминания (фиксации) и последующего анализа (например, просмотра на экране) временных диаграмм большого количества цифровых сигналов. Логические анализаторы используются при динамической отладке различных цифровых устройств и систем, а также при контроле их работы. Совершенно незаменимы они при разработке и отладке различных микропроцессорных систем, контроллеров, компьютеров, где используется большое количество многоразрядных шин цифровых сигналов. Именно логические анализаторы позволяют разработчику увидеть те временные диаграммы, которые он рисует на бумаге при проектировании своего устройства, причем увидеть их в реальном масштабе времени, посмотреть, как работает устройство на своей нормальной рабочей скорости.

Логический анализатор по своему назначению близок к осциллографу, так как он также позволяет наблюдать на экране временные диаграммы сигналов. Но существуют и существенные отличия логического анализатора от обычного (не цифрового) осциллографа:

Логический анализатор работает только с цифровыми, то есть двухуровневыми (реже трехуровневыми) сигналами, а осциллограф — с аналоговыми сигналами, имеющими бесконечно большое число разрешенных уровней.

Логический анализатор имеет большое количество входных линий (обычно от 16 до 64), то есть позволяет одновременно фиксировать множество входных сигналов, а осциллографы обычно позволяют одновременно увидеть не более четырех входных сигналов.

Логический анализатор работает в режиме однократного запоминания временных диаграмм (как запоминающий осциллограф). То есть анализатор запоминает состояния входных сигналов в течение заданного времени (называемого окном регистрации), а затем дает возможность анализировать зафиксированные последовательности. Осциллограф же работает обычно в режиме непрерывной развертки, то есть он не запоминает формы входного сигнала и позволяет наблюдать только повторяющиеся, периодические сигналы.

Логический анализатор предусматривает возможность так называемой предпусковой регистрации. Эта возможность предусматривается и в цифровых осциллографах, но ее нет в аналоговых осциллографах.

Рассмотрим подробнее, что такое предпусковая регистрация.

Процесс регистрации входных сигналов (или отображения их на экране в обычном осциллографе) всегда должен быть привязан к какому-то моменту времени, к какому-то внешнему событию, называемому запуском. Иначе разобраться в отображаемых сигналах будет совершенно невозможно. Например, в осциллографах моментом запуска обычно является момент превышения входным исследуемым сигналом установленного порога. Сигналом запуска может служить и специальный внешний синхронизирующий сигнал. В логических анализаторах в качестве запуска обычно используется момент появления на входах заданного уровня или заданной последовательности одного или нескольких входных сигналов.

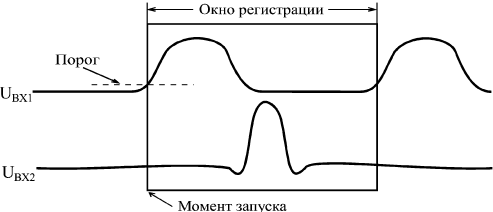

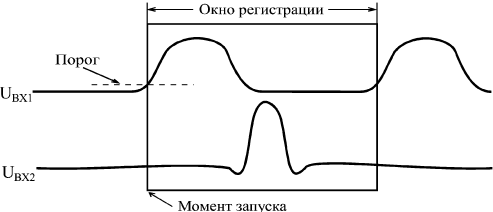

В обычных осциллографах отображение формы входного сигнала (или входных сигналов) начинается в момент запуска, то есть на экране видно только то, что происходило со входными сигналами после момента запуска. Такая регистрация может быть названа послепусковой. Можно также сказать, что точка запуска всегда находится в начале окна регистрации (рис. 15.1).

Рис. 15.1. Послепусковая регистрация в аналоговых осциллографах

В логических анализаторах (и в цифровых осциллографах) существует возможность увидеть и зафиксировать не только то, что было после запуска, но еще и то, что происходило в течение определенного времени до момента запуска. Именно эта регистрация до момента запуска и называется предпусковой регистрацией. В этом случае точка запуска может находиться и в начале, и в середине, и в конце окна регистрации (рис. 15.2). Понятно, что такая возможность очень удобна, так как, выбирая величину длительности предпусковой регистрации, можно увидеть те события, временная привязка к началу которых затруднена или попросту невозможна. Длительность (глубина) предпусковой регистрации может быть постоянной (например, равной половине длительности окна регистрации) или переменной (то есть задаваться пользователем в пределах от нуля до полной длительности окна регистрации). При переменной глубине предпусковой регистрации точка запуска может располагаться в любой точке окна регистрации — от его начала до конца.

С точки зрения схемотехники, логический анализатор представляет собой быстродействующую буферную оперативную память, работающую в периодическом режиме. Буфер этот однонаправленный: сначала в буферную память с большой тактовой частотой последовательно записываются состояния нескольких входных сигналов, а затем эта информация последовательно читается из буфера. Таким образом, адреса буферной памяти могут перебираться одним и тем же счетчиком как в режиме записи, так и в режиме чтения. Структура таких буферов уже рассматривалась.

Рис. 15.2. Предпусковая регистрация в логических анализаторах и цифровых осциллографах

Главные особенности логического анализатора, по сравнению со стандартной структурой информационного буфера на основе оперативной памяти, следующие:

большое число разрядов шины данных (то есть входных сигналов, каналов регистрации анализатора);

необходимость обеспечения режима предпусковой регистрации;

необходимость временной привязки процесса регистрации (записи в память) к состояниям входных сигналов (обеспечение запуска).

Первая из этих особенностей приводит к тому, что данные при чтении приходится считывать не все сразу, а по очереди (особенно при числе разрядов больше 32). Обычно данные требуется читать по 8 или по 16 разрядов. В результате усложняется та часть схемы буферной памяти, которая отвечает за чтение данных.

Вторая особенность требует существенного усложнения схемы счетчика, перебирающего адреса буферной памяти.

Наконец, третья особенность требует усложнения схемы управления работой информационного буфера.

Логические анализаторы делятся на синхронные (или анализаторы логических состояний) и асинхронные (или анализаторы временных диаграмм). Синхронные анализаторы работают от тактового генератора исследуемой схемы и фиксируют только временные сдвиги, кратные его периоду, а следовательно, выявляют только нарушения в логике работы схемы. Асинхронные анализаторы работают от собственного внутреннего тактового генератора, поэтому они позволяют измерять абсолютные значения временных сдвигов между сигналами и могут выявлять ошибки из-за неправильно рассчитанных задержек, из-за емкостных эффектов и т.д. Они обычно делаются гораздо более быстрыми, чем синхронные анализаторы (рассчитываются на предельно возможную частоту регистрации). В идеале, логический анализатор должен обеспечивать оба эти режима работы, то есть работать как от своего внутреннего тактового генератора с разными тактовыми частотами, так и от внешнего тактового сигнала. Иначе говоря, тактовый генератор анализатора должен быть также достаточно сложным.

Сформулируем исходные данные для проектирования логического анализатора. В данном случае нам важно не получить рекордные характеристики, а всего лишь продемонстрировать принципы разработки подобных схем на основе буферной памяти. Пусть количество входных линий анализатора (каналов регистрации) равно 32, количество регистрируемых состояний — 4096, максимальная тактовая частота — 10 МГц, тактовый генератор — внутренний с изменяемой частотой или внешний, запуск — по положительному или отрицательному фронту (синхропереходу) на одной из 8 входных линий, глубина предпусковой регистрации — задается программно. Будем также считать, что данные из памяти читаются порциями по 8 разрядов.

Таким образом, буферная оперативная память анализатора должна иметь объем 128 Кбит при организации 4Кх32. Помимо оперативной памяти, анализатор должен включать в себя счетчик для перебора адресов с количеством разрядов не менее 12. В структуре анализатора должен быть также внутренний тактовый генератор с программно изменяемой частотой и возможностью подключения внешнего тактового сигнала. Наконец, необходимо наличие схемы запуска анализатора, которая будет выбирать одну из 8 входных линий и полярность синхроперехода (положительный или отрицательный фронт).

Память целесообразно выполнить на многоразрядных микросхемах ОЗУ (для снижения количества микросхем). Требования к быстродействию памяти в данном случае не слишком высоки (при максимальной тактовой частоте 10 МГц в течение 100 нс необходимо успеть переключить счетчик адресов и записать входную информацию в ОЗУ). Микросхем памяти, способных обеспечить такую скорость работы, достаточно много.

От счетчика адресов памяти требуется максимальное быстродействие (можно взять, например, микросхемы синхронных счетчиков КР531ИЕ17, которые достаточно легко каскадируются без потери быстродействия). Кроме простого перебора адресов, счетчик должен также обеспечивать предпусковую регистрацию. Остановимся на этом несколько подробнее.

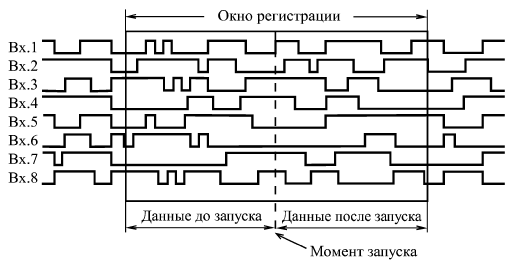

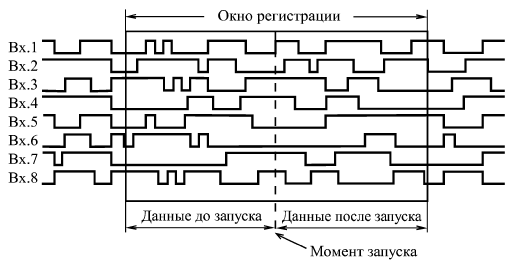

Для того чтобы реализовать предпусковую регистрацию, необходимо обеспечить непрерывную перезапись по кругу содержимого буферной памяти до момента прихода запуска (рис. 15.3).

Рис. 15.3. Организация предпусковой регистрации

То есть после записи последнего 4095 адреса надо записывать информацию по нулевому адресу. Если мы выбираем глубину предпусковой регистрации N тактов, то надо остановить регистрацию через (4096–N) тактов после момента прихода запуска. После остановки регистрации надо считывать содержимое памяти, начиная с точки остановки, с перебором адресов в том же самом направлении, что и при регистрации. Проведя 4096 операций чтения содержимого памяти, мы получим информацию о состоянии входных сигналов в течение N тактов до запуска и (4096–N) тактов после запуска, то есть моменту прихода запуска будет соответствовать содержимое адреса памяти, считанного N-ым.

Однако все произойдет именно таким образом только в том случае, если от момента начала регистрации до момента прихода запуска логический анализатор успеет зафиксировать N тактов. Иначе, остановив регистрацию через (4096–N), мы не перепишем всю память, и в части его адресов будет находиться предыдущая информация. Чтобы избежать этого, надо запретить реакцию на запуск в течение N тактов после начала регистрации (выдержать своеобразное "мертвое" время). А что будет, если запуск придет в течение этого самого "мертвого" времени? Если исследуемый процесс — периодический (то есть все входные сигналы повторяются через какое-то время), то анализатор среагирует на следующий запуск после окончания "мертвого" времени. Если же исследуемый процесс — однократный, не повторяющийся, то надо начать процесс регистрации заведомо раньше (на "мертвое" время или больше), чем начнется изучаемый процесс (например, если мы исследуем старт компьютера при включении питания).

Рис. 15.4. Временная диаграмма работы счетчиков логического анализатора

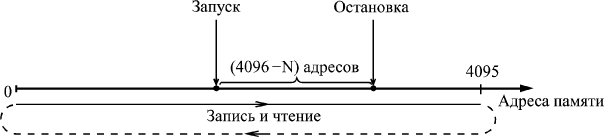

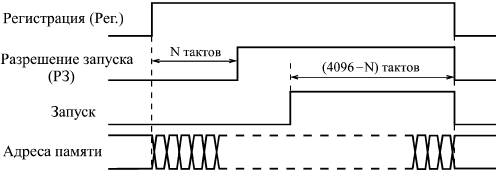

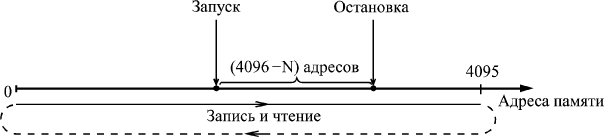

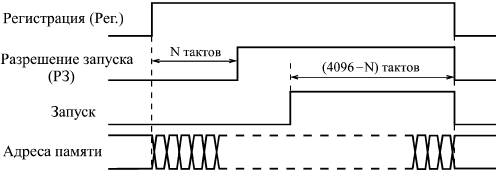

В результате счетчики анализатора должны обеспечивать временную диаграмму, показанную на рис. 15.4.

Адреса памяти начинают перебираться с началом регистрации. В течение N тактов после начала регистрации реакция на запуск запрещается, а затем разрешается. Через (4096–N) тактов после прихода запуска регистрация прекращается.

Отметим, что точно так же может быть реализована предпусковая регистрация в цифровом осциллографе. По сравнению с логическим анализатором, в схему надо будет добавить только один или несколько АЦП и некоторые другие цифро-аналоговые узлы.

Спроектируем схему счетчиков, реализующую приведенную временную диаграмму.

Счетчик, перебирающий адреса памяти, должен быть 12-разрядным, так как 212=4096. Во время регистрации он должен работать в непрерывном режиме, реализуя постоянную перезапись по кругу всей буферной памяти. На этот же счетчик можно возложить функцию отсчета "мертвого" времени (N тактов). Но этот счетчик не может отсчитывать еще и (4096–N) тактов после прихода запуска, так как запуск может прийти в любой момент после окончания "мертвого" времени. Для этого понадобится уже другой счетчик, причем также 12-разрядный.

Этот второй счетчик должен начинать работу только после прихода запуска (по сигналу "Разрешение запуска") и должен отсчитывать всего (4096–N) тактов, после чего завершать регистрацию. То есть получается, что логический анализатор начинает регистрацию по внешнему управляющему сигналу, а заканчивает автоматически через (4096–N) тактов после запуска, о чем должен сообщать вовне сигнал флага окончания регистрации.

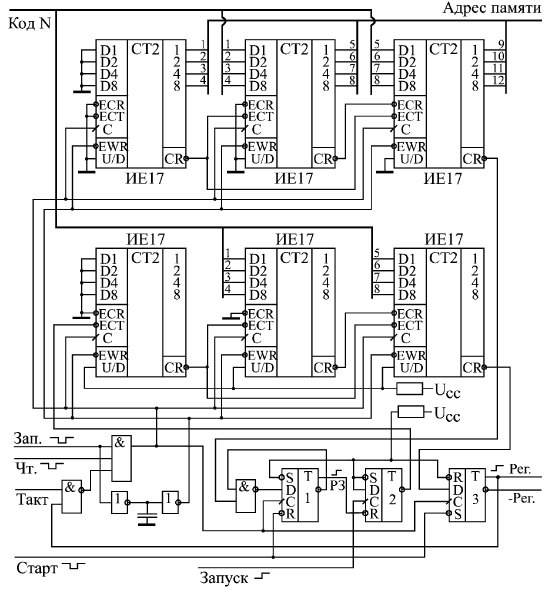

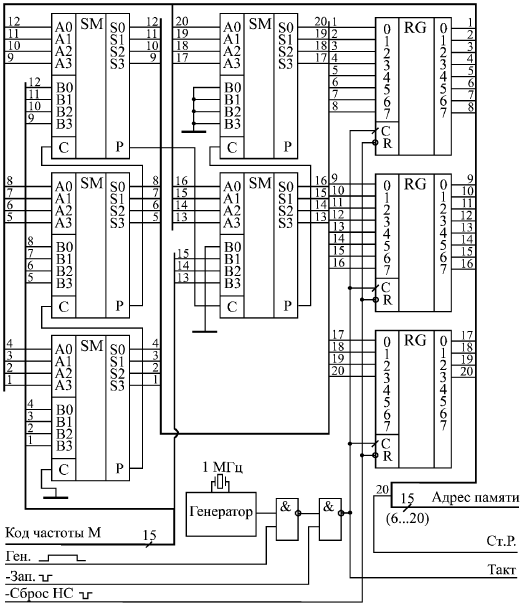

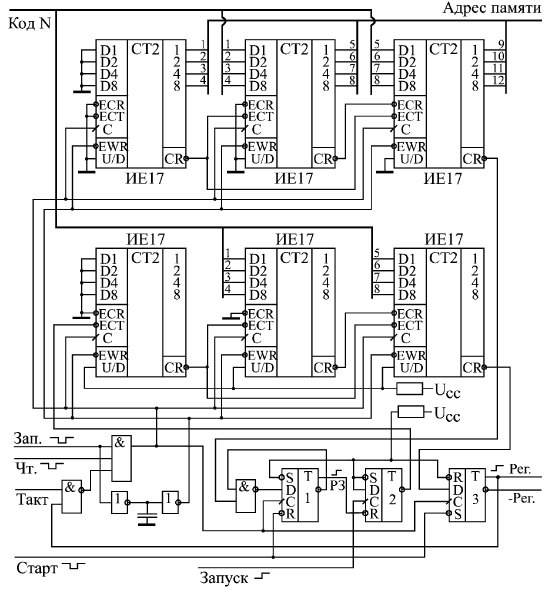

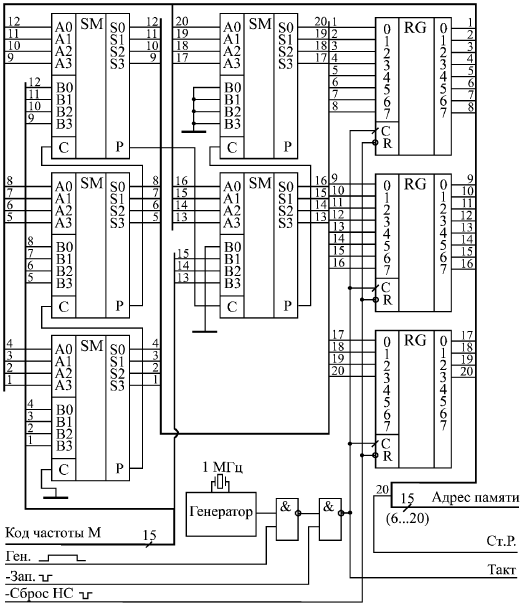

Рис. 15.5. Схема счетчиков логического анализатора

Таким образом, один 12-разрядный счетчик должен отсчитывать N тактов, а другой 12-разрядный счетчик должен отсчитывать (4096–N) тактов. Проще всего организовать такой режим, если в оба счетчика записать до начала работы код N и задать первому счетчику инверсный режим счета, а второму — прямой режим счета. Перебор адресов памяти первым счетчиком начнется с адреса N и будет происходить на уменьшение (а не на увеличение, как на рис. 15.3), однако для работы буферной памяти это не имеет никакого значения.

Сигнал переноса первого счетчика появится через N тактов после начала регистрации. Этот сигнал должен разрешать ожидание запуска (сигнал РЗ на рис. 15.4). Когда же приходит запуск, то разрешается работа второго счетчика, начинающего считать с кода N на увеличение. В результате сигнал переноса второго счетчика появится через (4096–N) тактов после начала его работы. Этот сигнал должен остановить процесс регистрации.

После окончания регистрации должен начаться процесс чтения из памяти. При этом первый счетчик должен перебирать адреса памяти по стробу чтения в том же направлении, что и при записи (то есть в режиме инверсного счета). 4096 последовательно произведенных циклов чтения позволит перебрать все 4096 адресов памяти, причем на N-ом цикле чтения будет прочитан такт, в котором произошел запуск.

Схема счетчиков логического анализатора, реализующая описанный алгоритм, приведена на рис. 15.5.

Два 12-разрядных счетчика реализованы на шести микросхемах ИЕ17. Первый счетчик (на рисунке вверху) работает в режиме инверсного счета, второй (на рисунке внизу) — в режиме прямого счета. Перед началом работы в оба счетчика по внешнему сигналу "–Зап." записывается код N. Причем четыре младших разряда 12-разрядного кода N равны нулю, а записываются только 8 старших разрядов. Это приводит к тому, что глубина предпусковой регистрации может задаваться с точностью до 16 тактов и принимать значения из ряда: 0, 16, 32, 48, 64,..., 4080. При записи на входы счетчиков –EWR и С поступают отрицательные сигналы, причем сигнал –EWR задержан относительно сигнала С на двух инверторах и (при необходимости) на конденсаторе. В результате положительный фронт сигнала С приходит тогда, когда сигнал –EWR равен нулю, что и требуется для записи.

На вход С обоих счетчиков могут приходить еще два сигнала: строб чтения из памяти "–Чт." и тактовый сигнал "Такт". Сигнал "Такт" приходит при регистрации (в режиме записи в память), а сигнал "–Чт." поступает при чтении из памяти зарегистрированной информации.

После того как в оба счетчика записан код N, необходимо начать регистрацию по внешнему сигналу "–Старт". Этот сигнал сбрасывает в нуль триггеры 1 и 2 и устанавливает в единицу триггер 3. Выходной сигнал триггера 3 разрешает регистрацию (сигнал "Рег." на рис. 15.4), то есть разрешает прохождение тактовых импульсов на входы счетчиков С. Это приводит к тому, что начинает работу первый счетчик, а второму счетчику работа запрещается по входу -ECT выходным сигналом триггера 2.

Первый счетчик, выходной код которого используется как адрес памяти, отсчитывает N тактов в инверсном режиме и вырабатывает сигнал переноса -CR. Этим сигналом перебрасывается в единицу триггер 1. Затем первый счетчик продолжает перебирать адреса памяти по кругу, а запись нулей в триггер 1 запрещается элементом 2И-НЕ на входе триггера. Выходной сигнал триггера 1 (сигнал РЗ на рис. 15.4) разрешает работу триггера 2 и тем самым разрешает реакцию схемы на сигнал запуска "Запуск" (положительный фронт).

После прихода сигнал "Запуск" перебрасывается в единицу триггер 2, разрешая работу второго счетчика. Первый счетчик в это время продолжает считать. Второй счетчик начинает свой счет с кода N, досчитывает в режиме прямого счета до 4096 и своим сигналом переноса –CR перебрасывает в нуль триггер 3. Это приводит к запрету поступления тактовых импульсов на вход С счетчиков и к остановке регистрации.

После этого может начаться чтение записанной информации по стробу "–Чт.". По заднему (положительному) фронту этого сигнала первый счетчик будет перебирать адреса памяти в инверсном режиме. Второй счетчик также будет считать, но это не имеет никакого значения. После 4096 циклов чтения вся информация из памяти будет прочитана, и схема будет готова к новой регистрации.

Перейдем теперь к проектированию других узлов логического анализатора.

Как уже отмечалось, тактовый сигнал анализатора может быть как внутренним (от внутреннего тактового генератора), так и внешним (от исследуемой схемы). Для повышения универсальности анализатора целесообразно обеспечить его работу на нескольких тактовых частотах. Большие частоты будут использоваться для анализа быстрых процессов, а малые частоты — для анализа длительных процессов. Тактовая частота не должна при этом принимать слишком много значений. Вполне достаточно ряда нескольких частот, различающихся вдвое.

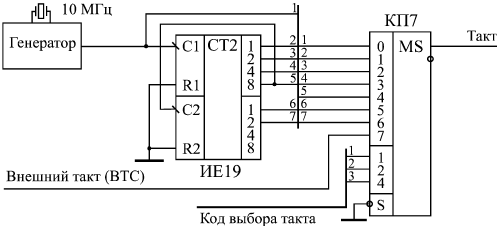

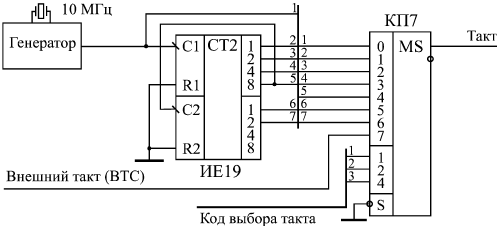

Пример схемы тактового генератора для логического анализатора приведен на рис. 15.6.

Рис. 15.6. Тактовый генератор логического анализатора

Тактовый генератор анализатора выполнен на кварцевом генераторе, 6-разрядном счетчике (ИЕ19) и 8-канальном мультиплексоре (КП7). Он может выдавать на выход ряд тактовых частот, различающихся в 2 раза (период 100, 200, 400, 800, 1600, 3200, 6400 нс) или внешний тактовый сигнал ВТС. То есть он позволяет реализовать как синхронный, так и асинхронный режим работы логического анализатора. Счетчик может быть применен асинхронный (ИЕ19), так как каждый его выход используется самостоятельно, независимо от других. Выбор канала мультиплексора (вида тактового сигнала) осуществляется 3-разрядным кодом выбора такта, причем код 111 будет соответствовать внешнему тактовому сигналу.

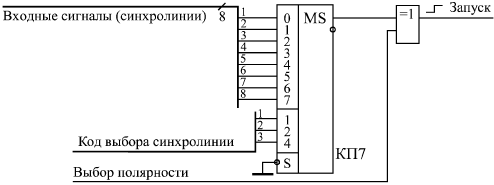

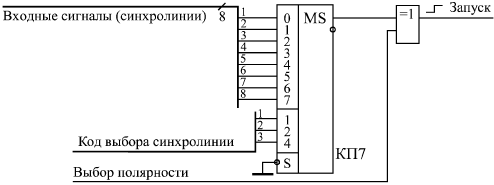

Схема запуска анализатора должна обеспечивать выбор положительного или отрицательного фронта (синхроперехода) на одной из 8 входных линий анализатора. Выходным сигналом запуска является положительный фронт (см. рис. 15.5). Для выбора одного из восьми входных сигналов удобно использовать 8-канальный мультиплексор (КП7), а для выбора полярности перехода можно применить элемент Исключающее ИЛИ, включенный в режиме управляемого инвертора. Схема запуска получается очень простой (рис. 15.7). Выбор входного сигнала, по которому будет производиться запуск, осуществляется 3-разрядным управляющим кодом выбора синхролинии. Выбор полярности перехода производится внешним сигналом выбора полярности, причем единица на этом входе соответствует отрицательному фронту, а нуль — положительному фронту.

Рис. 15.7. Схема запуска логического анализатора

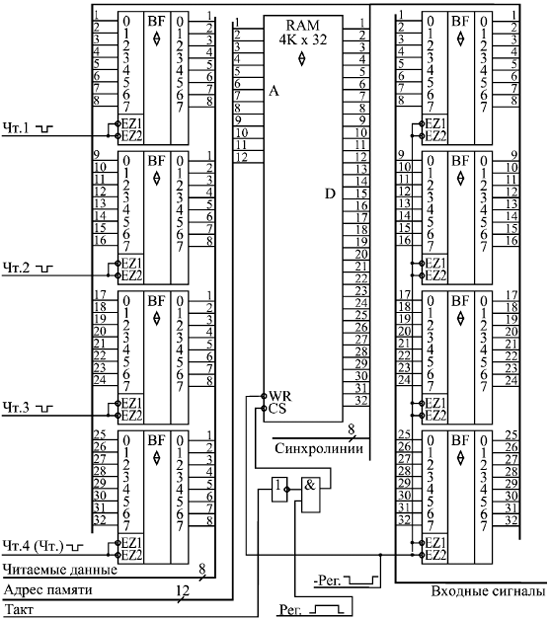

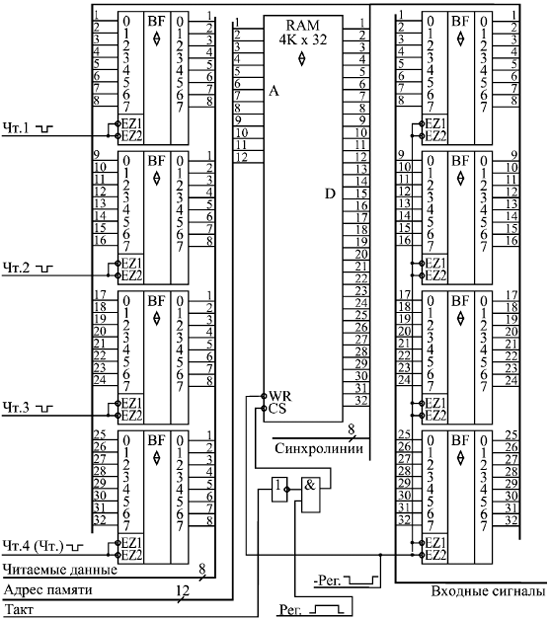

Наконец, последний узел логического анализатора — это память с буферами данных. Память должна иметь организацию 4Кх32, для чего придется использовать 4 микросхемы, так как обычно микросхемы оперативной памяти бывают 8-разрядные. Шина данных таких микросхем двунаправленная, поэтому требуется применение буферов для данных. Память должна работать в режиме записи при регистрации и в режиме чтения при чтении информации, зарегистрированной логическим анализатором. Для упрощения схемы целесообразно использовать нетактируемые микросхемы памяти.

В режиме записи сигнал –CS памяти должен представлять собой отрицательные импульсы на каждый адрес памяти, а сигнал –WR должен быть постоянно активным (нулевым). Отметим, что некоторые микросхемы памяти (например, КР541РУ2) могут записывать информацию и при постоянных нулевых уровнях обоих сигналов -CS и -WR при изменении только адресов памяти. Использование таких микросхем еще более упрощает схему.

В режиме чтения сигнал –CS должен быть постоянно активным (нулевым), а сигнал –WR должен быть постоянно равен единице. Смена читаемой информации будет производиться только сменой адресов памяти.

Для чтения информации из памяти порциями по 8 разрядов надо применить четыре 8-разрядных однонаправленных буфера (типа АП5). Каждый из них будет открываться своим стробом чтения и выдавать на общую 8-разрядную шину данных по 8 разрядов читаемой из памяти информации. Таким образом, чтение 32 разрядов из одного адреса памяти потребует четырех циклов чтения из логического анализатора. Смена адреса памяти должна происходить после последнего из этих четырех циклов чтения. То есть для чтения всего объема памяти потребуется 16384 циклов чтения по 8 разрядов из логического анализатора.

Помимо буфера чтения необходимо применить также входной 32-разрядный буфер, который будет пропускать входные (регистрируемые) сигналы на память в режиме регистрации и будет закрываться после окончания регистрации. Назначение этого буфера состоит в том, чтобы не выдавать на входные линии логического анализатора читаемую из памяти по двунаправленной шине данных информацию. Этот буфер также можно построить на микросхемах однонаправленных буферов типа АП5.

Рис. 15.8. Схема памяти логического анализатора

В результате схема памяти логического анализатора будет иметь вид, показанный на рис. 15.8.

Объединение четырех микросхем памяти производится стандартным образом: объединяются одноименные разряды адреса, сигналы –CS и –WR всех микросхем. На входы –CS подается сигнал, равный нулю при отсутствии регистрации (нулевой сигнал "Рег.") и равный инверсному тактовому сигналу при регистрации (отрицательному импульсу на каждый адрес памяти). Минимальная длительность импульса -WR равна в режиме записи половине периода тактового сигнала с частотой 10 МГц, то есть 50 нс, поэтому память должна успевать за это время записать информацию. На входы –WR подается сигнал "-Рег.", равный нулю при регистрации и единице при отсутствии регистрации. Если память может записывать информацию при постоянных нулевых сигналах -CS и -WR, то на вход –CS можно постоянно подать нулевой уровень.

Четыре микросхемы АП5 входного буфера (справа по рисунку) управляются сигналом "-Рег.": они открываются на все время регистрации и закрываются, когда регистрации нет.

Четыре микросхемы АП5 буфера чтения открываются на чтение (выдают 8-разрядные читаемые данные) каждая свои стробом чтения: "–Чт.1" ... "–Чт.4". При этом сигнал "–Чт.4" (его задний фронт) используется для переключения счетчиков адреса памяти при чтении (см. сигнал "–Чт." на рис. 15.6). Для чтения информации из одного адреса памяти нужно последовательно подать сигналы "–Чт.1" ... "-Чт.4", после чего адрес переключится на следующий.

В качестве синхролиний для запуска анализатора (см. рис. 15.7) используются восемь разрядов данных памяти. В режиме регистрации на них приходят 8 входных сигналов логического анализатора.

Таким образом, схема логического анализатора спроектирована полностью.

Сформулируем теперь порядок управления этой схемой. Управлять ею может, например, компьютер или контроллер, который будет отображать, обрабатывать и хранить зарегистрированные последовательности входных сигналов.

Перед началом регистрации необходимо записать в счетчики анализатора код N (количество тактов предпусковой регистрации) по сигналу записи "-Зап." (см. рис. 15.5). Необходимо также установить 7-разрядный управляющий код, который определит режим работы анализатора. Три разряда этого кода задают тип тактового сигнала анализатора (см. рис. 15.6). Три разряда выбирают номер входного сигнала (из восьми возможных), на котором фронт будет служить запуском, а последний седьмой разряд определит полярность этого фронта, синхроперехода (см. рис. 15.7). После этого можно начинать регистрацию по сигналу "–Старт" (см. рис. 15.5). Анализатор отсчитает "мертвое" время, зафиксирует приход синхроперехода (запуск) и остановит регистрацию через нужное количество тактов после запуска. Узнать о том, что регистрация завершилась, можно, исходя из анализа сигнала "Рег." (см. рис. 15.5). Затем можно начинать чтение из буферной памяти анализатора по стробам "–Чт.1" ... "–Чт.4" (см. рис. 15.8). Когда информация из всех 4096 адресов па мяти будет прочитана, анализатор снова будет готов к регистрации.

Разработка генератора аналоговых сигналов

Цифровые генераторы (или, как их еще называют, синтезаторы) аналоговых сигналов произвольной формы часто используются при отладке различных аналоговых и аналого-цифровых устройств и систем. Они позволяют не только получить сигналы разных стандартных и нестандартных форм, но и обеспечить высокую точность задания амплитуды и частоты сигнала, не достижимые в случае обычных аналоговых генераторов. Цифровые генераторы работают обычно под управлением компьютеров или контроллеров, что обуславливает большие удобства пользователя и широкие возможности по заданию разнообразных форм сигналов и по их хранению.

Мы будем разрабатывать довольно простой генератор, рассчитанный на звуковой диапазон частот выходного сигнала 20 Гц ... 20 кГц (период от 50 мкс до 50 мс). Генератор должен формировать сигналы произвольной формы с амплитудой, задаваемой управляющим кодом. Генератор должен работать в режиме автоматической (периодической) генерации, а также в режиме разовой генерации с остановкой генерации после окончания одного периода выходного сигнала. Управление работой генератора должно быть полностью цифровым.

Отметим, что в реальности сигналы сложной формы, как правило, бывают низкочастотными. Они встречаются, например, при виброиспытаниях, в медицинской технике, в сейсмической технике и т.д. Высокочастотные сигналы обычно имеют довольно простую форму, например, синусоидальную. Поэтому наш простой генератор, рассчитанный на невысокие частоты, будет, тем не менее, удовлетворять требованиям довольно широкого спектра применений.

Разработку генератора мы начнем "с конца", то есть с того выходного сигнала, который он должен формировать.

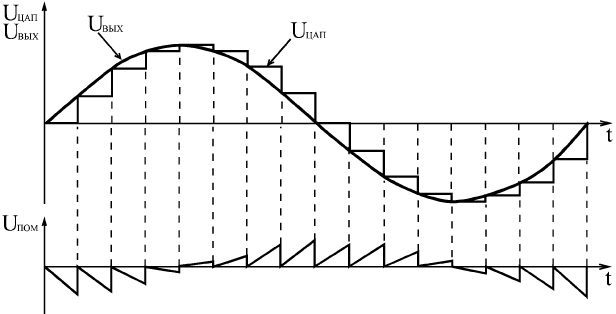

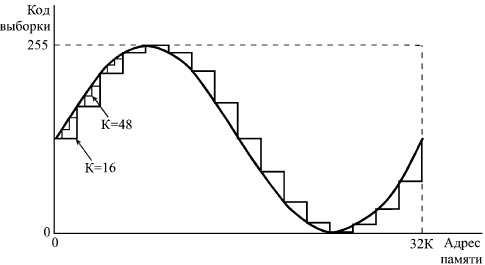

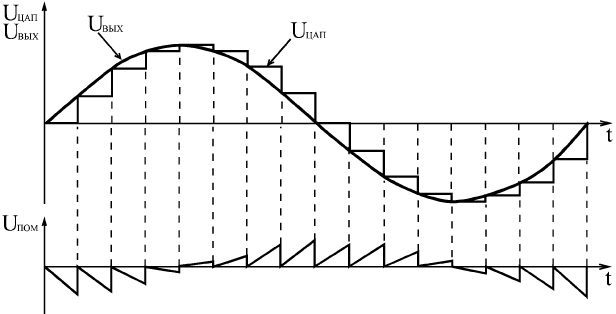

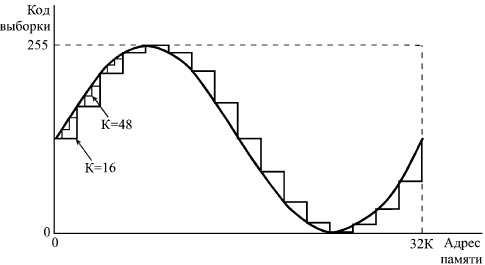

Как уже отмечалось в лекции 13 , выходной сигнал ЦАП UЦАП представляет собой ступенчатую функцию, которую можно представить в виде суммы идеального ("гладкого") аналогового сигнала UВЫХ и пилообразного сигнала помехи UПОМ (рис. 15.9).

Сигнал помехи UПОМ имеет основную частоту, равную частоте поступления входных кодов на ЦАП. Для сглаживания ступенек выходного сигнала ЦАП и приближения его к идеальному сигналу UВЫХ можно применить простой аналоговый фильтр низкой частоты (ФНЧ), который должен существенно ослаблять сигнал помехи, но не ослаблять полезный выходной сигнал генератора. В примере на рис. 15.9 частота полезного сигнала в 16 раз меньше частоты сигнала помехи, поэтому задача фильтрации не слишком сложна. Однако от генератора сигналов произвольной формы может понадобиться синтез выходных сигналов с крутыми фронтами (например, прямоугольных или пилообразных сигналов). В этом случае применение такого выходного фильтра низкой частоты может исказить выходные сигналы, затянув их фронты. Поэтому целесообразно предусмотреть два выхода генератора: один с низкочастотной фильтрацией, а другой без нее.

Рис. 15.9. Цифровая генерация аналогового сигнала

Помимо фильтра низкой частоты, выходной узел генератора сигналов должен содержать схему задания амплитуды выходного сигнала. В случае использования оперативной памяти для хранения кодов выборок выходного сигнала, схема задания амплитуды может и отсутствовать. При этом в память необходимо заносить коды выборок сигнала с нужной амплитудой. Однако такой подход не слишком удобен, так как он требует пересчета всех кодов выборок для каждой новой амплитуды сигнала выбранной формы. Гораздо удобнее сделать так, чтобы в памяти всегда хранились коды выборок сигнала с максимально возможной амплитудой, а выходной сигнал с ЦАП ослаблялся управляемым аттенюатором в нужное количество раз.

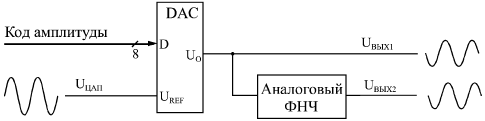

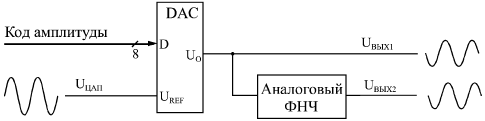

В результате схема выходного узла генератора аналоговых сигналов будет включать в себя еще и управляемый аттенюатор, рассмотренный в разделе 7.1 (рис. 15.10).

Рис. 15.10. Схема выходного узла генератора

Аналоговый фильтр нижней частоты должен иметь коэффициент передачи в полосе пропускания, равный единице и частоту среза, обеспечивающую эффективное подавление сигнала помехи. Тип схемы фильтра и его порядок не слишком важны. Для удобства пользователя целесообразно сделать фильтр неинвертирующим, чтобы выходные сигналы на обоих выходах генератора (UВЫХ1 и UВЫХ2) были одной полярности. Аттенюатор управляется 8-разрядным кодом амплитуды, что обеспечивает коэффициент деления сигнала от 1/256 до 1. Если амплитуда исходного сигнала UЦАП равна 10 В, то амплитуда выходного сигнала (UВЫХ1 и UВЫХ2) может быть задана с точностью около 40 мВ. Увеличение разрядности кода амплитуды потребовало бы принятия специальных мер, так как слишком малые аналоговые сигналы сильно искажаются шумами и помехами по цепям питания. ЦАП необходимо применять умножающий с биполярным выходом, чтобы обрабатывать как положительные, так и отрицательные выходные сигналы.

Теперь переходим к проектированию собственно цифровой части генератора.

Как уже отмечалось ранее, основной узел генератора должен представлять собой буферную оперативную память с периодическим режимом работы. Причем буфер этот должен быть однонаправленным. Перед началом работы в буфер заносится массив кодов выборок синтезируемого сигнала, а во время работы генератора адреса памяти опрашиваются в нужном темпе, и выходные коды памяти подаются на ЦАП, формирующий аналоговый сигнал UЦАП. Проблема состоит в выборе нужного объема памяти и в способе перебора адресов для обеспечения нужной частоты выходного сигнала. Память может также быть постоянной (ПЗУ), если необходимо формировать одну или несколько постоянных форм сигналов. В этом случае операция записи в память исключается, но проблема выбора способа перебора адресов памяти остается.

Существует два основных способа перебора адресов памяти генератора аналоговых сигналов, каждый из которых имеет свои достоинства и недостатки.

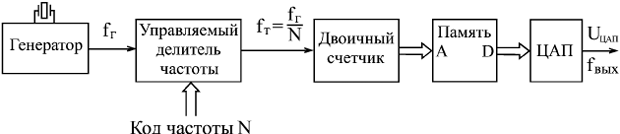

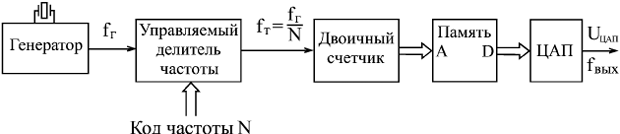

Рис. 15.11. Опрос памяти с помощью двоичного счетчика

Первый, простейший способ предусматривает перебор адресов памяти генератора с помощью обычного двоичного счетчика. В данном случае, опрашиваются все адреса памяти подряд. Изменение частоты аналогового выходного сигнала генератора производится с помощью изменения тактовой частоты этого счетчика, для чего используется тот или иной управляемый делитель частоты опорного кварцевого генератора (рис. 15.11). Частота выходного сигнала будет определяться при таком решении по формуле fвых = fГ/(N2n), где fГ — частота задающего кварцевого генератора, N — управляющий код делителя частоты, n — разрядность счетчика (разрядность шины адреса памяти).

Главное достоинство данного подхода состоит в том, что при изменении частоты выходного сигнала не меняется точность воспроизведения формы выходного сигнала. Ведь точность воспроизведения формы аналогового сигнала зависит в первую очередь от количества выборок, приходящихся на период выходного сигнала, а здесь оно постоянно и равно количеству адресов памяти. Например, если память имеет 1К адресов, то выходной сигнал при любой частоте будет задаваться с помощью 1024 точек, и он всегда будет иметь 1024 ступеньки.

Однако данное решение имеет и серьезные недостатки. Основной его недостаток состоит в том, что частота сигнала помехи в данном случае прямо пропорциональна частоте выходного аналогового сигнала генератора (она больше частоты выходного сигнала во столько раз, сколько адресов имеет память). Например, при 1К адресов памяти частота сигнала помехи в 1024 раз больше частоты выходного сигнала, и при изменении частоты выходного сигнала в 1000 раз также в 1000 раз будет изменяться частота сигнала помехи. Отфильтровать такую помеху переменной частоты чрезвычайно трудно, если не невозможно, так как требуется применение фильтра с частотой среза, изменяемой в очень широких пределах.

Другой существенный недостаток данного метода связан с высокими требованиями к быстродействию ЦАП. Например, если максимальная частота выходного аналогового сигнала генератора должна быть 20 кГц, а память имеет 1К адресов, то ЦАП должен успевать работать с частотой более 20 МГц, то есть иметь время установления менее 50 нс. При большей частоте выходного сигнала и при большем объеме памяти требования к быстродействию ЦАП будут еще выше. И с такой же скоростью должна работать буферная память, то есть требования к быстродействию памяти также велики.

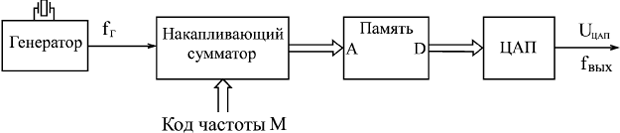

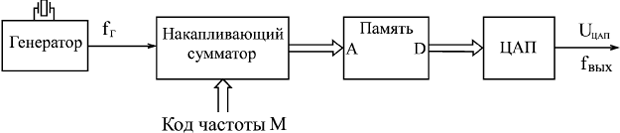

Второй возможный способ перебора адресов памяти генератора аналоговых сигналов состоит в применении накапливающего сумматора с переменным шагом суммирования (рис. 15.12).

Рис. 15.12. Опрос памяти с помощью накапливающего сумматора

В память, как и в предыдущем случае, заносится массив кодов выборок периода требуемого сигнала. Но при генерации опрашиваются не все адреса памяти подряд, а только адреса с шагом, задаваемым входным кодом накапливающего сумматора M (см. раздел 4.2.1). Чем больше этот шаг, тем быстрее будет пройден весь объем памяти и тем больше будет частота выходного сигнала генератора. И, соответственно, чем меньше шаг, тем больше времени потребуется на опрос всех адресов памяти, тем меньше будет частота выходного сигнала генератора.

При изменении шага опроса памяти изменяется и количество выборок на период выходного сигнала, что приводит к изменению точности воспроизведения формы сигнала. Количество выборок К на период выходного сигнала вычисляется по формуле К = 2n/M, где n — количество разрядов адреса памяти, М — управляющий код накапливающего сумматора. А частота выходного аналогового сигнала определяется формулой fВЫХ = fГ M/2n, где fГ — частота задающего кварцевого генератора. То есть выходная частота прямо пропорциональна управляющему коду M, а не обратно пропорциональна, как в предыдущем случае.

Главное достоинство данного подхода состоит в том, что сигнал помехи на выходе всегда имеет одну и ту же частоту, равную частоте задающего кварцевого генератора fГ, независимо от частоты выходного аналогового сигнала. Поэтому такую помеху легко отфильтровать, никакой перестройки частоты среза фильтра не требуется.

Другое важное достоинство данного решения состоит в том, что по мере роста частоты выходного сигнала генератор сам пропорционально уменьшает количество выборок на период выходного сигнала, поэтому требования к быстродействию ЦАП, формирующего выходной сигнал, не слишком жесткие. ЦАП может быть в несколько раз более медленным, чем в предыдущем случае, при такой же максимальной выходной частоте. Или, можно сказать и так, при том же самом ЦАП генератор может выдавать выходные сигналы с гораздо более высокой частотой. Точно так же снижаются и требования к быстродействию памяти. Это приводит к тому, что объем памяти в данном случае может быть гораздо больше, чем в предыдущем.

Но ничто не дается даром, поэтому данный метод имеет и существенный недостаток. С ростом частоты выходного сигнала его форма будет передаваться все более грубо, ступеньки будут все больше. На рис. 15.13 приведен пример воспроизведения формы синусоидального сигнала, записанного в память объемом 32Кх8 для двух разных шагов наращивания адреса М (количество выборок на период К = 16 и К = 48). Понятно, что точность воспроизведения формы сигнала сильно зависит от кода М. Это может привести к тому, что некоторые фрагменты сигналов сложной формы могут быть пропущены. К тому же в случае, когда количество выборок на период выходного сигнала К не равно целому числу, периоды выходного сигнала будут несколько отличаться один от другого. Смягчает этот недостаток уже упоминавшееся обстоятельство, что в природе сигналы сложной формы обычно низкочастотные, а именно низкочастотные сигналы воспроизводятся при данном методе наиболее точно.

Рис. 15.13. Опрос памяти с разными шагами (количество выборок на период К = 16 и К = 48)

Исходя из всех этих соображений, останавливаем свой выбор именно на этом, втором методе.

Примем для дальнейшего проектирования, что минимальное количество выборок на период выходного сигнала будет равно 32, а максимальное будет равно количеству адресов памяти. Так как от генератора требуется большой диапазон выходных частот (частоты могут различаться в 1000 раз), объем памяти должен быть большим. Если минимальное количество выборок на период равно 32, то максимальное количество выборок на период потребуется в тысячу раз больше, то есть 32000. Поэтому количество адресов памяти не должно быть меньше 32000. Возьмем память с количеством адресов, равным 32К.

Количество разрядов данных памяти, определяющее точность задания величины выборок выходного сигнала, не стоит брать слишком большим. Ведь на формируемый аналоговый сигнал будут накладываться помехи от цифровой части схемы, поэтому чрезмерно точное задание величин выборок выходного сигнала окажется попросту излишним. Поэтому выберем количество разрядов данных памяти равным 8, то есть память будет иметь организацию 32Кх15.

Спроектируем накапливающий сумматор для генератора аналоговых сигналов.

Как уже отмечалось, частота выходного аналогового сигнала прямо пропорциональна управляющему коду накапливающего сумматора М. Абсолютная погрешность установки частоты составит 0,5/М. Поэтому для малых частот погрешность установки частоты будет максимальной. Например, если коду М = 1 будет соответствовать частота 20 Гц, то следующее разрешенное значение частоты будет равно 40 Гц (при М = 2). Это не слишком удобно, хорошо бы иметь точность установки частоты не ниже хотя бы 10% во всем частотном диапазоне. Возьмем, например, абсолютную погрешность установки частоты 0,5 Гц. Значит, при М = 1 генератор должен выдавать частоту 1 Гц. Такие низкие частоты мы можем просто не использовать, зато частота 20 Гц (при М = 20) будет иметь точность установки 2,5%. Разрешенные значения частот вблизи 20 Гц составят при этом 19 Гц, 20 Гц, 21 Гц.

Выберем теперь величину тактовой частоты накапливающего сумматора (то есть частоты задающего кварцевого генератора). Максимальная частота выходного сигнала нашего генератора должна быть равна 20 кГц, при этом на период выходного сигнала должно приходиться 32 выборки. То есть тактовая частота накапливающего сумматора должна быть не менее 20 кГц • 32 = 640 кГц. Выберем с запасом тактовую частоту равной 1 МГц. Максимальная частота выходного аналогового сигнала при 32 выборках на период будет при этом составлять 1 МГц/32 = 31,25 кГц.

Количество разрядов накапливающего сумматора должно быть таким, чтобы он обеспечивал весь выбранный частотный диапазон. Нетрудно подсчитать, что нам потребуется 20-разрядный накапливающий сумматор (так как 220 = 1048576), то есть при тактовой частоте 1 МГц минимальный период выходного сигнала составит 1048576 тактов или чуть более одной секунды, что примерно соответствует частоте выходного сигнала в 1 Гц.

Если использовать 4-разрядные микросхемы полных сумматоров (ИМ3 или ИМ6), то для построения 20-разрядного сумматора потребуется 5 микросхем сумматоров. Для запоминания выходного кода сумматоров надо будет использовать три микросхемы 8-разрядных регистров, причем регистры эти должны быть со входом сброса (например, ИР35) для начального сброса накапливающего сумматора.

Получившаяся в итоге схема накапливающего сумматора приведена на рис. 15.14. В качестве тактового сигнала она использует в режиме генерации сигнал с кварцевого генератора частотой 1 МГц (разрешающий сигнал "Ген."), а в режиме записи в память кодов выборок — строб записи в память "-Зап.". На входы адреса памяти подаются сигналы 15 старших выходных разрядов накапливающего сумматора, а 5 младших разрядов накапливающего сумматора не используются. Код частоты М подается на 15 младших входных разрядов накапливающего сумматора, а на старшие 5 разрядов поданы нулевые сигналы. В результате при максимальном коде М=32767 накапливающий сумматор будет переполняться за 32 такта (выходная частота 31,25 кГц), а при минимальном коде М=1 — за 1048576 тактов (выходная частота около 1 Гц).

Рис. 15.14. Накапливающий сумматор генератора аналоговых сигналов

Перед началом записи в память накапливающий сумматор должен быть сброшен в нуль сигналом "–Сброс НС". Во время записи в память каждый строб записи "–Зап." должен увеличивать на единицу адрес памяти, поэтому код частоты М должен быть установлен в данном режиме равным 32 (двоичный код 100000).

Условия правильной работы накапливающего сумматора следующие. За период тактового генератора должны успеть сработать регистр и сумматор. В нашем случае это условие довольно легко выполняется, так как период тактового генератора 1 мкс. Но при построении более высокочастотных генераторов аналоговых сигналов требуется более высокая тактовая частота, и при этом может уже сказаться накопление задержек переноса пяти микросхем сумматоров. При тактовой частоте больше 10 МГц это уже может вызвать большие проблемы. Точно так же за период следования стробов записи в памяти "-Зап." должны успевать срабатывать регистр и сумматоры. Это условие обычно значительно проще выполнить, чем первое.

Посмотрим, какой будет частота сигнала помехи и какой должна быть частота среза выходного аналогового низкочастотного фильтра (см. рис. 15.10). При управляющем коде частоты М больше или равном 32 каждый тактовый импульс будет вызывать изменение адреса памяти. Поэтому частота помехи будет равна частоте тактового генератора (1 МГц). Это соответствует частоте выходного сигнала, большей 32 Гц. Однако нам надо обеспечить нижнюю частоту выходного аналогового сигнала 20 Гц.

Если код частоты М будет лежать в пределах от 16 до 31, то адрес памяти будет изменяться не реже одного раза на два такта тактового генератора. Частота помехи будет не менее 500 кГц. То есть при частоте выходного сигнала, большей 16 Гц, частота сигнала помехи будет в пределах от 500 кГц до 1 МГц. Максимальная частота выходного аналогового сигнала равна 31,25 кГц. Значит, частота среза фильтра должна быть такой, чтобы сильно ослаблять частоты, большие 500 кГц, но не искажать частоты, меньшие 31,25 кГц. Эти частоты различаются в 16 раз, поэтому фильтр построить не слишком сложно.

В результате мы получаем, что выбранная схема накапливающего сумматора обеспечивает диапазон частот выходного аналогового сигнала от 16 Гц до 31,25 кГц, причем погрешность установки частоты составляет 0,5 Гц во всем частотном диапазоне. Количество выборок сигнала на период будет изменяться от 32 на верхнем краю частотного диапазона до 32К на нижнем краю частотного диапазона. Это вполне удовлетворяет требованиям к генератору, сформулированным в начале данного раздела.

Переходим теперь к проектированию схемы управления для генератора аналоговых сигналов.

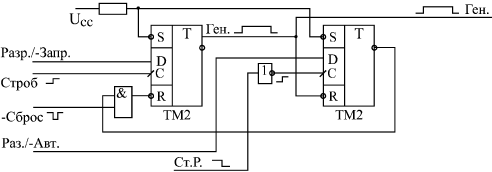

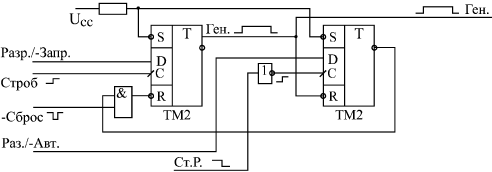

Схема управления генератора должна обеспечивать два режима работы: режим записи в память и режим генерации. Причем генерация может быть как автоматическая (периодическая), так и разовая. Эти режимы реализуются простой схемой на двух триггерах (рис. 15.15).

Рис. 15.15. Схема управления для генератора аналоговых сигналов

Первый (левый по рисунку) триггер служит для разрешения или запрещения генерации. По внешнему сигналу "Строб" (положительный фронт) в него записывается единица для разрешения генерации или нуль для запрещения генерации. Выходной сигнал "Ген." используется для разрешения тактовых импульсов накапливающего сумматора (см. рис. 15.16) и для управления остальной частью схемы. Перед началом работы генератора этот триггер сбрасывается в нуль внешним сигналом начального сброса "–Сброс".

Второй (правый по рисунку) триггер служит для организации режима разового запуска генератора. При запрете генерации этот триггер сброшен в нуль сигналом "Ген." (единица на инверсном выходе). При разрешении генерации этот триггер срабатывает по отрицательному фронту на старшем разряде накапливающего сумматора (сигнал "Ст.Р." со схемы на рис. 15.16), то есть по переполнению накапливающего сумматора, возникающему после окончания одного периода аналогового сигнала. Если внешний управляющий сигнал "Раз./-Авт." установлен в нуль (автоматический запуск), то ничего не происходит, триггер остается сброшенным. Если же внешний сигнал "Раз./-Авт." установлен в единицу (разовый запуск), то после окончания одного периода выходного аналогового сигнала генератора второй триггер перебросится в единицу (нуль на инверсном выходе) и сбросит тем самым первый триггер, запретив генерацию. Узнать об этом можно, анализируя флаг генерации —сигнал "Ген.". Для нового разрешения генерации надо снова записать единицу в первый триггер.

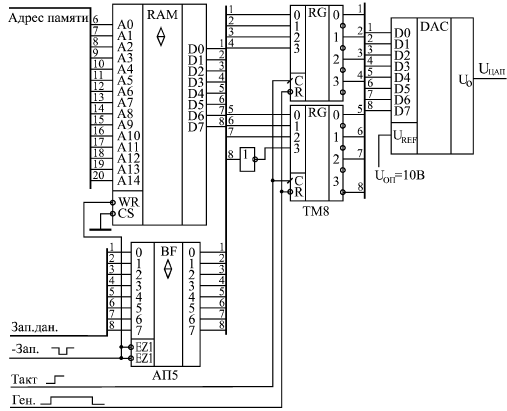

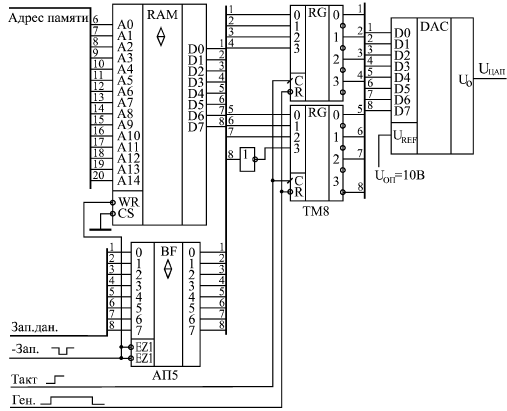

Наконец, последний узел генератора аналоговых сигналов — это память с ЦАП.

Прежде всего надо обеспечить, чтобы ЦАП, формирующий выборки аналогового сигнала по кодам из памяти, выдавал как положительные, так и отрицательные сигналы, то есть был биполярным. Это существенно повысит универсальность генератора. ЦАП должен формировать выходное напряжение (а не выходной ток), что позволит более просто обрабатывать выходной сигнал выходным узлом (см. рис. 15.10). Требования к быстродействию ЦАП в нашем случае невелики: коды всегда поступают на него с периодом в 1 мкс, значит, за это время ЦАП должен успеть установить свое выходное напряжение. Таких ЦАП существует довольно много.

Опорное напряжение ЦАП удобно выбирать равным 10 В, что обеспечит размах выходного сигнала от –10 В до +10 В. При этом шаг изменения выходного сигнала (минимально возможная высота ступеньки) составит 20В/256, то есть около 80 мВ. Но это только для сигнала максимальной амплитуды 10 В. Если же требуется генерация сигнала с амплитудой 1 В (ослабление выходным аттенюатором в 10 раз), то шаг изменения выходного сигнала будет около 8 мВ.

Входной код ЦАП (то есть выходной код буферной памяти) должен фиксироваться в параллельном регистре, чтобы все разряды этого кода подавались на входы ЦАП одновременно. В момент отсутствия генерации на выходе ЦАП должно быть нулевое напряжение, поэтому данный регистр должен иметь вход сброса, на который подается сигнал "Ген.". Однако надо учитывать, что при биполярном выходе ЦАП нулевому уровню выходного сигнала соответствует не нулевой код 00000000, а код 10000000 (с единицей в старшем разряде). Поэтому регистр должен сбрасываться не в нуль, а именно в состояние 10000000. При этом просто поставить дополнительный инвертор на старший разряд кода нельзя, так как он внесет задержку и старший разряд кода будет устанавливаться позже остальных разрядов, что может вызвать недопустимо большие выбросы выходного напряжения. Поэтому этот входной регистр ЦАП должен иметь как прямые, так и инверсные выходы (например, ТМ8), причем все разряды, кроме старшего, надо брать с прямых выходов регистра, а старший разряд — с и нверсного выхода. Это обеспечит одновременное изменение всех разрядов кода. Для компенсации инверсии старшего разряда надо дополнительно проинвертировать сигнал старшего разряда на входе регистра.

Память выборок сигнала целесообразно использовать многоразрядную с совмещенной входной и выходной шинами данных, что позволит упростить схему. Микросхемы с организацией 32Кх8 выпускаются многими фирмами. Память лучше брать нетактируемую, чтобы в режиме чтения (при генерации) можно было постоянно подавать на вход –CS сигнал логического нуля. Быстродействие памяти не слишком критично, так как перебор адресов происходит довольно медленно. За период тактового сигнала (1 мкс) в режиме чтения должен успеть сработать регистр накапливающего сумматора, и память должна успеть выдать читаемый код (с задержкой выборки адреса).

Рис. 15.16. Память и ЦАП генератора аналоговых сигналов

Совмещенная шина входных/выходных данных памяти требует применения однонаправленного входного буфера (например, АП5), через который в режиме записи на память будут подаваться записываемые в память коды выборок генерируемого сигнала. Буфер должен открываться тем же сигналом, который подается на вход –WR памяти. Во время генерации буфер должен быть закрыт.

В результате схема буферной памяти с ЦАП для генератора аналоговых сигналов будет выглядеть так, как показано на рис. 15.16.

Перед началом работы в память должны быть записаны коды выборок (8-разрядная шина "Зап. Дан".) по стробу "–Зап.". Данные должны выставляться до начала строба и сниматься после его окончания. Во время строба записи "-Зап." память переходит в режим записи (сигнал –WR), а буфер открывается (сигналы -EZ1 и -EZ2). За счет задержки буфера записываемые данные снимаются со входов данных памяти позже, чем заканчивается сигнал "-Зап.". Поэтому данные записываются в память. По окончании сигнала "-Зап." происходит смена адреса памяти (см. рис. 15.14). Всего должно быть проведено 32К циклов записи для полного заполнения памяти.

Когда начинается генерация (сигнал "Ген."), адреса памяти перебираются накапливающим сумматором, а читаемая из них информация записывается по сигналу "Такт" (см. рис. 15.14) в 8-разрядный регистр (две микросхемы ТМ8), а затем поступает на входы ЦАП. В результате выдача выборок выходного сигнала (UЦАП) задерживается на один такт относительно момента чтения из памяти, но эта задержка, как правило, не имеет никакого значения. После окончания генерации регистр сбрасывается в состояние 10000000, соответствующее нулю выходного сигнала UЦАП. Так как по сигналу начального сброса "–Сброс" (см. рис. 15.15) генерация запрещается, на выходе генератора в этот момент также будет нулевое напряжение.

Таким образом, схема генератора аналоговых сигналов полностью спроектирована.

Сформулируем теперь последовательность действий, которые надо предпринимать для управления работой генератора.

После включения питания надо подать сигнал начального сброса "–Сброс" (см. рис. 15.15), который запретит генерацию и обеспечит нулевой уровень выходного напряжения генератора.

Затем необходимо записать в память массив кодов выборок сигнала требуемой формы. Для этого код частоты надо задать равным 32 и сбросить накапливающий сумматор в нуль сигналом "–СбросНС". После этого надо производить последовательную запись всех 32К кодов по шине записываемых данных Зап.дан., сопровождая их стробами записи "-Зап.".

После окончания записи в память можно запускать генерацию, но перед началом генерации надо сбросить накапливающий сумматор сигналом "–СбросНС", задать режим запуска генерации (разовый или автоматический), а также установить код нужной выходной частоты (см. рис. 15.14 и 15.15). Кроме того, надо задать код амплитуды выходного сигнал (см. рис. 15.10). После этого надо подать положительный сигнал "Разр./-Запр." и сопроводить его стробом (см. рис. 15.15). Если требуется остановить автоматическую генерацию, то нужно установить нулевой сигнал "Разр./-Запр." и сопроводить его стробом. Если же генерация разовая, то узнать о том, продолжается ли она или уже закончилась, можно на основании анализа сигнала "Ген." (см. рис. 15.15).

В заключение отметим, что управление разработанным генератором аналоговых сигналов лучше возложить на компьютер или управляющий интеллектуальный контроллер, что существенно упростит работу с ним.

| |

|

|

Скачать 5.63 Mb.

Скачать 5.63 Mb.