курица. Методические указания по выполнению лабораторных работ для студентов специальности 09. 02. 01 компьютерные системы и комплексы по дисциплине Проектирование цифровых устройств

Скачать 1 Mb. Скачать 1 Mb.

|

|

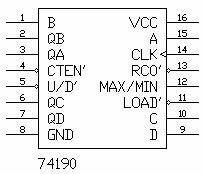

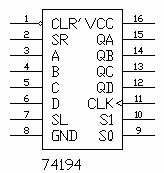

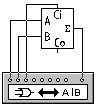

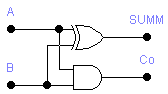

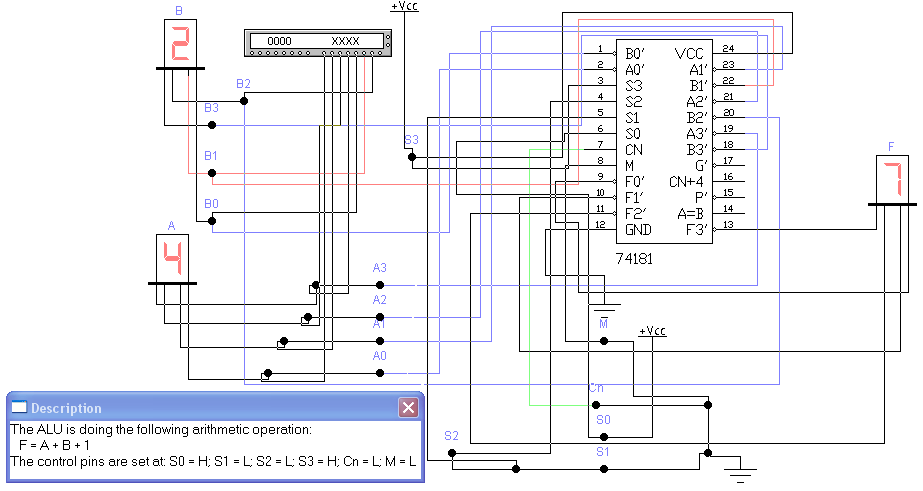

Лабораторная работа № 6 «Мультиплексоры, дешифраторы, сумматоры» Цель работы: изучить алгоритмы работы этих схем {модуль 2 глава 5}. 1. Мультиплексор 74151. Выбрать из библиотеки Digital (библиотека MUX) интегральную схему мультиплексора MUX 74151 [1-of-8 Data Sel/Mux]. Данная интегральная схема содержит: восемь входов – D0…D7; адресные входы А, В и С (С является старшим битом адреса); прямой выход – Y и инверсный выход – W. Питание микросхемы: 8 (GND) – общий провод, 16 (VCC) – +5 В. Примечание: выход G! не использовать. 1.1. Задание: 1.1.1. Соберите схему включения мультиплексора. На выходы Y и W подключите светодиоды. Поочередно на один из входов D0, D1, .., D7подайте сигнал и проверьте работу мультиплексора. Результаты занесите в таблицу: АдресДанныеВыходCBAD0D1D2D3D4D5D6D7YW0000ххххххх01ххххххх1001…………………………………1111.1.2. Воспользуйтесь мультиплексором как универсальным логическим элементом и на основе его постройте схему: а) выполняющую операцию дизъюнкции трех переменных (у=А+В+С). Соберите схему и проверьте её работу; б) выполняющую операцию конъюнкции с отрицанием ( 2. Дешифратор 74155. Выберите из библиотеки Digital (библиотека DEC) интегральную схему дешифратора 74155 [Dual 2-to-4 Dec/DEMUX]. ИС 74155 – представляет собой сдвоенный дешифратор 2-4. Данная интегральная схема содержит: входы – А, В, 1С и 2С! (входу А соответствуют младшие биты сигнала); инверсные выходы 1Y0, 1Y1, 1Y2, 1Y3 и 2Y0, 2Y1, 2Y2, 1Y3. Сигналы 1G! и 1С открывают выходы 1Yi, а сигналы 2G! и 2С! – выходы 2Yi. Питание микросхемы: 8 (GND) – общий провод, 16 (VCC) – +5 В. 2.1. Ознакомьтесь с работой дешифратора. 2.2. Задание: 2.2.1. Перепишите таблицу состояний сдвоенного дешифратора 2-4 и проверьте её, собрав схему. П.2.2.2 НЕ ДЕЛАТЬ 2.2.2. На основе дешифратора 2-4 постройте схему дешифратора 3-8. Составьте таблицу состояний и проверьте её на собранной схеме. Таблица состояний дешифратора 74155.  3. Сумматор 4008 Выберите из библиотеки Digital ICs (серия 4ххх) интегральную схему сумматора 4008 [4-bit Binary Full Adder]. ИС представляет собой четырехразрядный сумматор кодов А0…А3 и В0…В3. Выходы S0, S1, S2 и S3. Сигналы СOUT и CIN подключить к общему проводу (земле). Питание микросхемы: 8 (VSS) – общий провод, 16 (VDD) – +5 В. 3.1. Задание: 3.1.1. Соберите схему сумматора, подав на входы А0, А1 и В0, В1 коды слагаемых (А1А0 + В1В0), остальные входы соедините на общий провод. К выходам S0, S1, S2 подключите светодиоды. 3.1.2. Выполните сложение кодов (А1А0 + В1В0) и проверьте результат, используя сумматор: 3.1.3. Соберите схему полусумматора, построенную из элементарных логических элементов, и проверьте его работу. 4. Содержание отчета. 4.1. Таблица состояний и схема включения п. 1.1.1. 4.2. Схемы п. 1.1.2. 4.3. Таблица и схема п. 2.2.1. 4.4. Результаты п. 2.2.2. 4.5. Схема п. 3.1.1 4.6. Схема п. 3.1.3. Лабораторная работа № 7 «Счётчики и сдвиговые регистры» Цель работы: Изучить алгоритмы работы последовательных логических схем, научиться строить счётчики с заданным коэффициентом пересчёта {модуль 2 главы 7-8}. 1. Счётчик 74190.  1.1. Выберите из библиотеки Digital (библиотека Counter) интегральную схему счётчика 74190 (Sync BCD Up/Down Counter). Схема представляет собой двоично-десятичный четырехразрядный реверсивный счётчик с предварительной установкой. Питание микросхемы: 8 (GND) – общий провод, 16 (VCC) – Uпит. Счётчик содержит: выходы QA, QB, QC и QD. Вход В нормальном режиме работы на входы Load (загрузка данных) микросхемы 74190 и CE (разрешение счета) подается напряжение низкого уровня. Если необходимо считать в прямом направлении, то на вывод Up/Down (суммирование/вычитание) подают напряжение низкого уровня. Счетчик последовательно переключается при каждом перепаде напряжения на входе тактовых импульсов Clock с низкого уровня на высокий (положительный фронт). Для счета импульсов в обратном направлении на вывод Up/Down подается напряжение высокого уровня. При программировании микросхемы 74190 необходимый коэффициент в двоично-десятичном коде подается на входы Р0 — Р3, а на вход Load — кратковременный импульс напряжения низкого уровня. Процесс загрузки происходит независимо от тактовых импульсов. Счетчик 74190 может работать как делитель с регулируемым коэффициентом деления, причем возможно параллельное или последовательное включение нескольких счетчиков. Так как в схеме нет отдельного входа сброса данных, то при необходимости в счетчик следует загружать нули. Если при счете в прямом направлении значение достигает 9 или в обратном направлении — 0, то на выходе 12 формируется напряжение высокого уровня. В нормальном режиме работы микросхемы 74190 на выходе RC будет напряжение высокого уровня. Если на вход CE (разрешение тактовых импульсов) поступает напряжение низкого уровня, а на выводе 12 напряжение высокого уровня, то на выходе RC при следующем отрицательном фронте тактового импульса установится напряжение низкого уровня и останется на нем до тех пор, пока тактовый импульс снова не перейдет на высокий уровень напряжения. Это позволяет упростить каскадное включение нескольких счетчиков микросхемы 74190, если соединить выход RC одной ступени с входом CE следующей ступени при параллельном соединении входов тактовых импульсов. Состояние входа CE (разрешение тактовых импульсов) микросхемы 74190, который активизируется при низком уровне напряжения и может изменяться лишь тогда, когда на вход тактовых импульсов подается напряжение высокого уровня. 1.2. Задание: 1.2.1. Соберите схему счётчика. На вход CLK от генератора слова задайте последовательность импульсов 1-0. На выходы Qi и MAX/MIN подключите светодиоды. Проверьте процесс счёта, реверсирования. В каких случаях возникает сигнал MAX/MIN? 1.2.2. Задав необходимый код на входы предустановки А и В, реализуйте счётчик, считывающий 6 импульсов до заполнения. Проверьте его работу. 1.2.3. Синтезируйте схему счётчика, считывающего от 0 до 5, используя ИС 74190 и необходимый логический элемент. Четырехразрядный универсальный сдвиговый регистр 74194.  2.1. Выберите из библиотеки Digital (библиотека > Shift Regs) интегральную схему сдвигового регистра 74194 (4 - bit Bidrectional). Питание микросхемы: 8 (GND) – общий провод, 16 (VCC) – Uпит. Регистр имеет последовательные входы данных SR и SL; четыре параллельных входа A, B, C и D; четыре выхода QА, QВ, QС и QD. Данные на выходах появляются при перепаде с 1 на 0 тактового импульса на входе CLK. Вход 2.2. Задание: 2.2.1. Занесите в регистр параллельный код 1111, на вход SR подайте «0». Перейдите в режим сдвига влево и пронаблюдайте, как при сдвиге единицы постепенно заменяются нулями. 2.2.2. Занесите в регистр параллельный 1010, на вход SR подайте «1», перейдите в режим сдвига вправо. Какой будет результат? 2.2.3. Занесите в регистр последовательный код 0100 через вход SR, осуществите сдвиг кода. 2.2.4. Повторите п. 2.2.3., используя вход SL. 2.3. Соберите и проверьте схему преобразователя 8 разрядного параллельного кода в последовательный с побайтовым преобразованием (использовать схемы: регистр 74194, счётчик 74160 и другие необходимые логические ИС). Примечание: На входы LOAD, ENT, ENP счётчика 74160 подайте «1». На параллельные входы регистра 74194 подайте код от генератора слова: 00AA16=0000.0000.1010.1012, затем 00DB16=0000.0000.1101.10112, затем 008816=0000.0000.1000.10002 и пронаблюдайте передачу кода. На вход S0 и На вход CLK регистра 74194 и счётчика 74160 подайте последовательность прямоугольных импульсов от функционального генератора (Function Generator). 3. Содержание отчета. 3.1. Схемные обозначения счётчика 74190, регистра 74194 и описание их работы. 3.2. Схема преобразователя п. 2.3. Лабораторная работа №8 Проектирование цифровых устройств на примере сумматора в пакете Electronics Workbench Цель работы – Изучить работ сумматоров с использованием пакета Electronics Workbench. Арифметические сумматоры Арифметические сумматоры являются составной частью так называемых арифметико-логических устройств (АЛУ) микропроцессоров (МП). Они используются также для формирования физического адреса ячеек памяти в МП с сегментной организацией памяти. В программе EWB арифметические сумматоры представлены в библиотеке Digital двумя базовыми устройствами, показанными на рис. 8.1: полусумматором и полным сумматором. Они имеют следующие назначения выводов: А, В – входы слагаемых, Σ – результат суммирования, Со – выход переноса, Ci – вход переноса. Многоразрядный сумматор создается на базе одного полусумматора и n полных сумматоров. В качестве примера на рис. 8.2 приведена структура трехразрядного сумматора [20]. На входы Al, A2, A3 и Bl, B2, В3 подаются первое и второе слагаемые соответственно, а с выходов S1, S2, S3 снимается результат суммирования. а) б) Рисунок 8.1. Схемы полусумматора (а) и полного сумматора (б)  Рисунок 8.2. Трехразрядный сумматор Для исследования внутренней структуры и логики функционирования сумматоров как нельзя лучше подходит логический преобразователь. После подключения полусумматора к преобразователю согласно рис. 8.3, а последовательно нажимаем кнопки  и в результате получаем таблицу истинности и булево выражение. Сравнивая полученные данные с результатами исследования базовых логических элементов в предыдущем разделе, приходим к выводу, что при подключении вывода (полусумматора к зажиму OUT преобразователя (как показано на рис. 8.3, а) он выполняет функции элемента исключающее ИЛИ. Подключив клемму OUT преобразователя к выходу Со полусумматора и проделав аналогичные действия, приходим к выводу, что в таком включении полусумматор выполняет функции элемента И. Следовательно, эквивалентная схема полусумматора имеет вид, показанный на рис. 8.4. и в результате получаем таблицу истинности и булево выражение. Сравнивая полученные данные с результатами исследования базовых логических элементов в предыдущем разделе, приходим к выводу, что при подключении вывода (полусумматора к зажиму OUT преобразователя (как показано на рис. 8.3, а) он выполняет функции элемента исключающее ИЛИ. Подключив клемму OUT преобразователя к выходу Со полусумматора и проделав аналогичные действия, приходим к выводу, что в таком включении полусумматор выполняет функции элемента И. Следовательно, эквивалентная схема полусумматора имеет вид, показанный на рис. 8.4.Схема включения четырехразрядного АЛУ на базе серийной микросхемы 74181 (отечественный аналог К155ИП3) показана на рис. 8.5. ИМС 74181 обеспечивает 32 функции работы АЛУ в зависимости от состояния управляющих сигналов на входе М и параллельных входах S0...S3, а также допускает наращивание разрядности (вход CN и выход CN<4 для переносов). Если на входе М напряжение высокого уровня, то запрещаются все внутренние переносы, и микросхема будет исполнять логические операции поразрядно. При напряжении низкого уровня на входе М переносы разрешаются, и будут выполняться арифметические операции над двумя четырехразрядными словами. За счёт внутренней схемы управления переносом (СУП) сигнал переноса на выходе Сn+4 появляется при каждом входном сигнале переноса, поступившем на вход Сn. Для организации переноса между корпусами АЛУ, объединяемыми в многоразрядную схему, используются выходы   а) б) Рисунок 8.3. Схемы подключения полусумматора (а) и полного сумматора (б) к логическому преобразователю  Рисунок 8.4. Структура библиотечного полусумматора  Рисунок 8.4. Настройка генератора слова для схемы на рис. 3.13 Контрольные вопросы и задания Чем отличается полусумматор от полного сумматора? Выясните внутреннюю структуру полного сумматора, пользуясь схемой его подключения к логическому преобразователю на рис. 8.3, б и принимая во внимание методику решения аналогичной задачи для полусумматора. Используя опыт работы со схемой на рис. 8.5, подключите ко входам трехразрядного сумматора на рис. 8.2 генератор слова, а к выходам — алфавитно-цифровой индикатор с дешифратором и проверьте правильность его функционирования. 4. Проверьте работу ИМС 74181 в режиме сумматора с переносом (на вход Сn подайте сигнал логического нуля).  Рисунок 8.5. Схема включения ИМС 74181 в режиме сумматора без переноса |