курица. Методические указания по выполнению лабораторных работ для студентов специальности 09. 02. 01 компьютерные системы и комплексы по дисциплине Проектирование цифровых устройств

Скачать 1 Mb. Скачать 1 Mb.

|

|

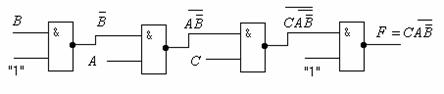

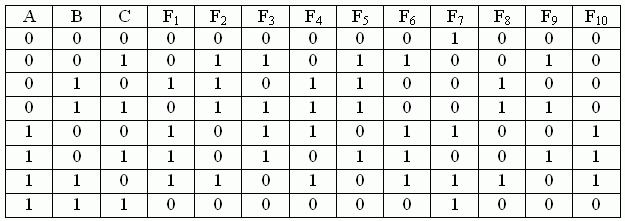

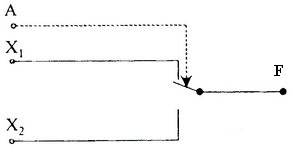

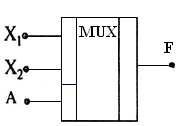

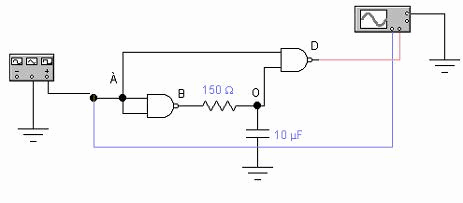

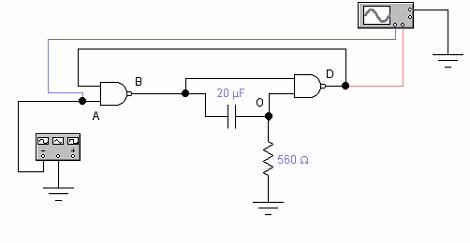

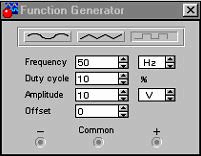

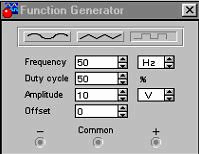

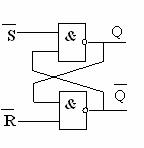

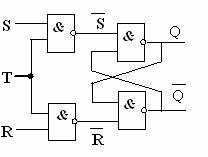

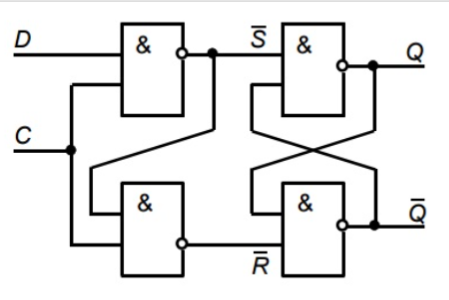

ВариантВыходная комбинацияВариантВыходная комбинация10011110100100111000111010000011100101100001011010000110000001101001101000011010100111110001111110011101000111011001110000011100100110000001100010011011000110111000101100001011Лабораторная работа №4 (4 часа) Исследование комбинационных логических схем Цель работы – научиться реализовывать любые логические функции с помощью элементарных логических схем. Ознакомиться с построением генераторов импульсов, построением формирователей импульсов на основе логических интегральных схем {модуль 2 глава 1}. 1. Реализация простых логических функций. Задание: 1.1. На основании определения логических операций НЕ (инверсии), И (коньюнкции), ИЛИ (дизъюнкции) заполните табл. 4.1. Таблица 4.1 Таблица состояний логических элементов Входные переменныеЗначение выходных функций FАВСНЕИИ-НЕИЛИИЛИ-НЕАВС0000010100111001011101111.2. По результатам таблицы 4.1 нарисуйте принципиальные схемы для реализации функций Для функции 2. Минимизация сложных логических функций и их реализация. 2.1. Пример. Реализуем логическую функцию, представленную в табл. 4.2. Таблица 4.2 Таблица состояний логической функции АВСF0 1 01 1 01 1 11 1 1Остальным комбинациям А, В, С, не указанным в таблице, соответствует значение F = 0. Таблице 4.2. соответствует логическое выражение По правилам алгебры логики проведем минимизацию функции F. Выносим общий множитель за скобки Используя очевидное соотношение но поэтому Для реализации выражения (1) с помощью элементов И-НЕ необходимо исключить операцию дизъюнкции, выразив её по формуле Де Моргана: Выражение (2) может быть получено и другим способом – используя карту Карно. Выражение (2) реализуется в схеме (рис. 1.2).  Рисунок 4.1 Соберите схему (рис. 4.1) и проверьте, что она реализует функцию, заданную в табл. 4.2. 2.2. Задание: Из табл. 1.3 выберите логическую функцию для своего варианта, составьте соответствующее логическое выражение, минимизируйте его и приведите к виду, удобному для схемной реализации. Из типовых элементов И-НЕ соберите схему и проверьте, что она реализует логическую функцию вашего варианта. Таблица 1.3 Таблица вариантов заданий (начиная с 11-го варианта повторяется по кругу)  3. Синтез логических схем. 3.1. Задание. С помощью логического преобразователя синтезируйте и реализуйте схему: Электронного замка, открываемого (F = 1) комбинацией входных сигналов А4А3А2А1, определяющих номер вашего варианта. Например, для варианта 9 замок должен открываться комбинацией 1001. Комбинация 0001 соответствует варианту 1, 0000 соответствует варианту 16. Далее по кругу: 0001 ≡ 17 вариант и т.д. Моделирующую автомат для голосования на примере трех участников. Алгоритм голосования: решение принято (F = 1), когда за него голосует не менее двух человек из трех. «Исключающее ИЛИ» (2 варианта), пользуясь элементами 2И-НЕ схемы К155ЛА3 (7400). Первый вариант имеет более простую запись и реализуется на пяти элементах 2И-НЕ, второй более сложную запись, но требует для реализации только 4 элемента. Одноразрядного компаратора, работающего по алгоритму: F=0, если А1>А2 и F=1, если А1 ≤ А2. Коммутатора сигналов, работающего по алгоритму: F = Х1, если А = 0 и F = Х2, если А = 1. Здесь А – коммутирующий сигнал (адресный вход), В1 и В2 – коммутируемые (информационные) сигналы. Схематически мультиплексор можно изобразить в виде коммутатора, обеспечивающего подключение одного из нескольких входов (их называют информационными) к одному выходу устройства. Кроме информационных входов в мультиплексоре имеются адресные входы и, как правило, разрешающие (стробирующие). Сигналы на адресных входах определяют, какой конкретно информационный канал подключен к выходу. Если между числом информационных входов n и числом адресных входов m действует соотношение n =2m, то такой мультиплексор называют полным, в других случаях мультиплексор называют неполным. В самом простом виде это выглядит так: Рассмотрим функционирование двухвходового мультиплексора (2 → 1), который условно изображён в виде коммутатора, а состояние его входов XI, Х2 и выхода F приведено в таблице: Адресный входВыход F0X11X2  УГО коммутатора на 2 входа на примере мультиплексора приведено ниже.  3.2. С помощью логического преобразователя подтвердите результаты п.п. «г» и «д» (задайте таблицу истинности, на её основе получите минимизированное логическое выражение и постройте схему устройства только на элементах И-НЕ). 4. Укоротитель импульсов. 4.1. Задание: 4.1.1. Соберите схему (рис. 4.1). Зарисуйте осциллограммы в точках А, В, О, D при подаче на вход импульсов от внешнего генератора (соедините канал В осциллографа с выходом D, а к каналу А - поочередно подключите точки А, В, О исследуемой схемы).  Рисунок 4.1 5. Удлинитель импульсов (одновибратор). 5.1. Задание: 5.1.1. Соберите схему одновибратора (рисунок 5.1). Подайте на вход одновибратора импульсы от внешнего генератора. Зарисуйте осциллограммы напряжений в точках А, В, О, D.  Рисунок 5.1  Рисунок 5.2 Параметры функционального генератора: - вид входных сигналов – прямоугольный; - частота – 50 Гц; - амплитуда входных сигналов – 10 В; - скважность – 10%. 6. Схема задержки импульсов. 6.1. Задание: 6.1.1. Синтезируйте схему, обеспечивающую выдачу положительных импульсов постоянной длительности, сдвинутых относительно коротких отрицательных импульсов на некоторое время t. Для этого воспользуйтесь схемами на рисунках 4.1 и 5.1. Постройте диаграммы для характерных точек схемы. 6.1.2. Соберите синтезированную схему и пронаблюдайте её работу. 7. Содержание отчета. 7.1. Результаты выполнения п. 1.1, 1.2. 7.2. Исходное логическое выражение, его минимизация и схемная реализация по п. 2.2. 7.3. Аналогично для п. 3.1 (а – д). 7.4. Пункт 3.2 продемонстрировать при сдаче отчета.  Параметры функционального генератора: - вид входных сигналов – прямоугольный; - частота – 50 Гц; - амплитуда входных сигналов – 10 В. 7.5. Схема рис. 1 и результаты п.п. 4.1.1. 7.6. Схема рис. 2 и результаты п.п. 5.1.1. 7.7. Синтезированная схема задержки и результаты п.п. 6.1.1. Лабораторная работа № 5 «Триггеры» Цель работы: изучить структуру триггеров различных типов и алгоритмы их работы {модуль 2 глава 6}. 1. Триггеры на логических элементах. 1.1. Асинхронный R-S триггер с инверсными входами. Соберите схему триггера на двух логических элементах 2И-НЕ и проверьте таблицу его состояний.  Рисунок 5.1 Для RS-триггера на двух элементах 2И-НЕ справедливы следующие уравнения состояния выхода У:  ; ;Данное уравнение является особым логическим уравнением, которое выражает последующее состояние выхода Y1 в зависимости от входов Х1 и Х2 и предыдущего состояния выхода. Иначе его можно представить в виде: Если S = R = 1, тогда Qn+1 = 0+1·Qn = Qn (хранение). Если S = 0, R = 1, тогда Qn+1 = 1+1·Qn = 1 (установка 1). Если S = 1, R = 0, тогда Qn+1 = 0+0·Qn = 0 (установка 0). На основании изложенного выше заполните таблицу состояний триггера Таблица 1 (Заголовок) tntn+1 1.2. Тактируемый (синхронный) R-S триггер Соберите схему триггера на логических элементах 2И-НЕ и проверьте таблицу его состояний.  Таблица 2 (Заголовок) SRT Соберите схему триггера на логических элементах 2И-НЕ и проверьте таблицу его состояний.  Таблица 3DС № варианта123456Rxyx Соберите схему R-S триггера с инверсными входами, подав на входы R и S коды с генератора слова, а на логический анализатор - входы R, S и выходы Q, Таблица 4 № варианта12345678910R Получите с помощью логического анализатора временные диаграммы для R, S, Q, 2. Интегральные триггеры. 2.1. D-триггер 74175 (триггер-защелка). Выберите из библиотеки Digitalинтегральную схему D-триггера 74175 (Quad D-type FF (clr)) Рисунок – Микросхема 74175 2.1.1. Задание: Исследуйте поведение триггера, воспользовавшись одним из входов Di и соответствующим выходом Qi. В какой момент происходит защелкивание информации? Нарисуйте схему подключения ИС 74175 для записи на выходах её кода, например, Q4Q3Q2Q1 = 0011. Соберите схему с кодом, соответствующим Вашему варианту (номер в журнале в двоичном коде) и зафиксируйте на выходах заданный код. 2.2. JK-триггер 7472. Выберите из библиотеки Digitalинтегральную схему JK-триггера 7472 (AND-gated JK MS-SLV FF (pre, clr)). Данная интегральная схема содержит: входы – J1, J2, J3, К1, К2, К3; выходы – Q и 2.2.1. Ознакомьтесь с работой JK-триггера. Запишите таблицу состояний триггера. Какие строчки таблицы соответствуют работе JK-триггера в качестве RS-триггера и Т-триггера? 2.2.2. Задание: Соберите схему включения триггера 7472. На выходы 3. Содержание отчета. 3.1. Результаты п. 1.1, 1.2., 1.3., 1.4. 3.2. Схема и результаты п. 2.1.1. 3.3. Таблица п. 2.2.1 и пояснение к ней |