0_МПиИСТС_Все главы. Микропроцессоры и интерфейсные средства транспортных средств

Скачать 10.01 Mb. Скачать 10.01 Mb.

|

3.5. Организация памятиХранение информации в памяти микропроцессорных систем может быть организовано различными способами. Наиболее часто реализуются следующие варианты организации памяти:

Использование того или иного способа организации памяти определяется функциями системы, объемом памяти и рядом других факторов. Многие микропроцессоры обеспечивают возможности реализации любого из этих способов. Линейная организация. Это наиболее простой способ организации памяти, при котором формируемый процессором адрес непосредственно поступает на адресную шину, обеспечивая обращение к соответствующей ячейке памяти. В этом случае адрес, который формируется процессором в соответствии с заданным в команде способом адресации (линейный адрес), выдается на системную шину как физический адрес выбираемой ячейки памяти. Сегментная организация. Данный способ обеспечивает разбиение памяти на отдельные сегменты (блоки), обращение к которым реализуется в соответствии с определенными правилами. В первую очередь реализуется разделение памяти на область (сегмент) команд и данных. Область данных может подразделяться на сегмент стека и несколько сегментов обрабатываемых данных. Размер сегментов может быть фиксированным (от 64 Кбайт до 4 Гбайт) или переменным (программируемым).

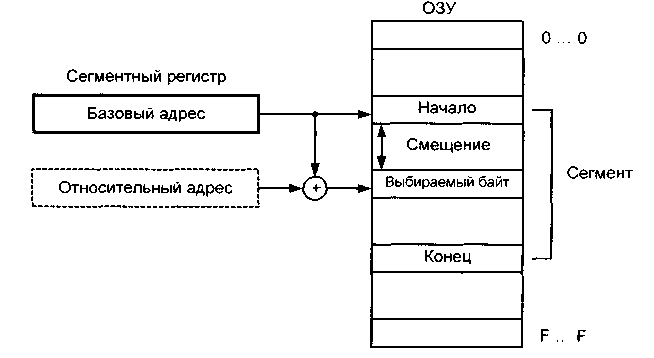

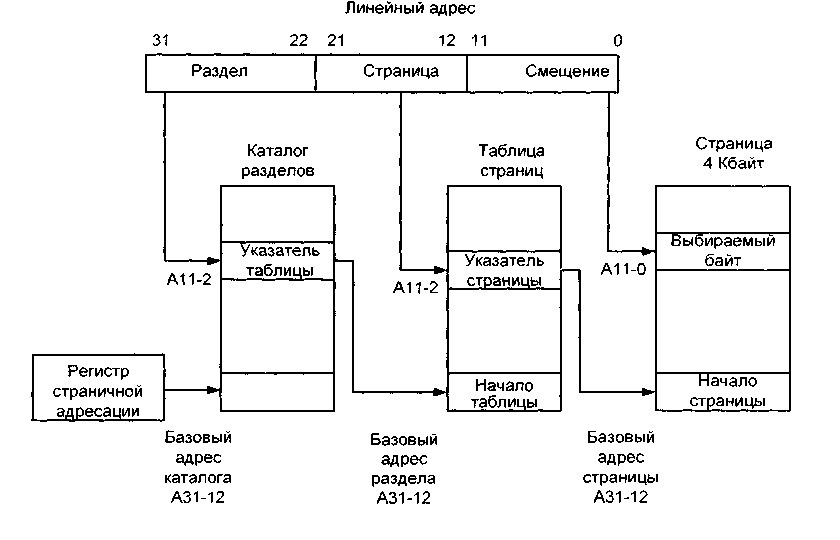

Реализация сегментной адресации обеспечивается с помощью специальных сегментных регистров, в которых хранится базовый (начальный) адрес, определяющий позицию первого байта данного сегмента. В этом случае формируемый при выполнении программы линейный адрес выбираемой команды или операнда является относительным адресом, который определяет их положение в сегменте, начальный адрес которого задается содержимым сегментного регистра (рис. 3.3). Физический адрес при сегментной организации памяти образуется путем арифметического суммирования базового адреса сегмента и относительного адреса операнда (команды). В ряде микропроцессоров, например, в Pentium, обращение к сегментам выполняется согласно определенным правилам, которые обеспечивают защиту сегментов в соответствии с заданной системой привилегий (защищенный режим). В этом случае кроме сегментных регистров для организации обращения к сегментам используются специальные структуры данных - дескрипторы, которые задают базовый адрес и размер сегмента, а также указывают его атрибуты, определяющие возможность доступа к содержимому сегмента. Страничная организация. Этот способ организации памяти предполагает разбиение адресуемых массивов данных или команд на относительно мелкие фрагменты - страницы. Типичный объем страницы составляет 4 Кбайт, хотя в ряде микропроцессоров обеспечивается возможность работы со страницами разного размера - от 256 байт до 4 Мбайт. Страницы могут размещаться в различных местах адресуемого пространства памяти, а их расположение определяется специальными таблицами адресов, которые обычно хранятся в ОЗУ. Страничная организация позволяет наиболее полно использовать имеющийся объем памяти, гак как обеспечивает разбиение информации и ее размещение в любом свободном фрагменте памяти размером не менее одной страницы. При страничной организации реализуется иерархический уровень разбиения информации, аналогичный принятому в печатных изданиях, когда материал разбивается на отдельные части - главы, разделы и подразделы, состоящие из страниц. Такое разбиение отражается в оглавлении печатного издания. В микропроцессорных системах со страничной организацией памяти, функции оглавления выполняют специальные таблицы адресов, которые хранятся в ОЗУ. Обычно реализуется двухступенчатое разбиение типа «раздел-страница», при котором для обращения к соответствующей странице необходимо предварительно определить адрес ее размещения с помощью соответствующих таблиц адресов (рис. 3.4).

При страничной организации памяти формируемый процессором линейный адрес используется для получения физического адреса, который образуется путем трансляции (преобразования) с помощью обращения к соответствующим таблицам адресов. На рис. 3.4 иллюстрируется процесс страничной трансляции 32-разрядного линейного адреса, выполняемый в процессорах Pentium. При этом линейный адрес обеспечивает выбор одного из 1024 разделов, каждый из которых может содержать 1024 страницы емкостью 4 Кбайт. Каталог разделов и таблицы адресов страниц хранятся в ОЗУ системы. Поле "Раздел" линейного адреса задает номер выбираемого раздела в каталоге, базовый адрес которого обычно хранится в специальном регистре страничной адресации. При этом из каталога разделов выбирается базовый адрес одной из 1024 таблиц, в которых хранятся базовые адреса страниц, входящих в соответствующий раздел. Поле "Страница" указывает в этой таблице базовый адрес страницы раздела, к которой производится обращение. Поле «Смещение» определяет позицию выбираемого операнда или команды на данной странице. Таким образом, их физический адрес формируется после процесса трансляции путем суммирования базового адреса страницы, полученного из соответствующей таблицы, и смещения, задаваемого 12 младшими разрядами линейного адреса. При страничной организации памяти часто реализуется ограничение доступа к определенным страницам с использованием системы привилегий, как и при сегментной организации. Во многих процессорах реализуются возможности как сегментной, так и страничной организации памяти. При этом обеспечивается возможность разбиения сегментов на отдельные разделы и страницы, размещаемые в свободных позициях памяти. Рассмотренная реализация страничной организации требует дополнительной памяти для хранения каталога разделов (до 4 Кбайт) и до 1024 таблиц страниц по 4 Кбайт каждая. Кроме того, трансляция адреса требует двух дополнительных циклов обращения к памяти для получения базовых адресов раздела и страницы. Чтобы избежать потерь времени на выборку этих адресов в микропроцессорах обычно имеется специальная память - буфер страничной трансляции, где хранятся базовые адреса страниц, к которым производились последние обращения. При последующих обращениях к этим страницам их базовый адрес выбирается непосредственно из буфера, и не требуется затрат времени на трансляцию адреса. Обычно емкость буфера составляет несколько десятков или сотен базовых адресов. При этом трансляция адреса с обращением к таблицам страниц производится достаточно редко - только в том случае, если базовый адрес страницы отсутствует в буфере, т.е. к данной странице ранее не было обращений, или эти обращения происходили достаточно давно, и ее базовый адрес был замещен адресами других страниц. Таким образом, буфер страничной трансляции обеспечивает страничную адресацию без существенной потери производительности системы. |