МПС РГР АВТ-409 Журкин. Министерство образования и науки российской федерации новосибирский государственный технический университет

Скачать 0.76 Mb. Скачать 0.76 Mb.

|

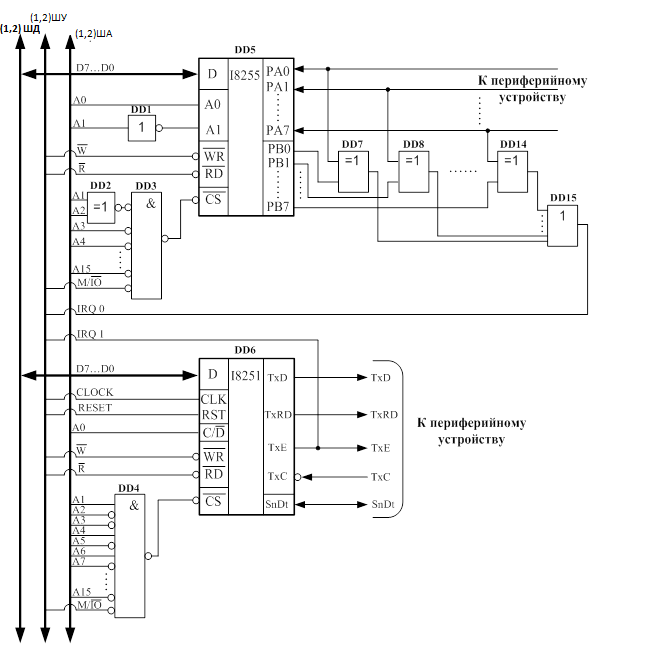

12. Программируемый периферийный интерфейс I8255.Программируемый периферийный интерфейс I8255 представляет собой три канала ввода/вывода A, B и C по 8 бит каждый. Существует три режима работы микросхемы. В режиме 0 три упомянутых канала могут быть независимо друг от друга запрограммированы на ввод или вывод информации. Режим 1 позволяет передавать информацию по каналам A и B, используя отдельные биты канала C для управления обменом данными. В режиме 2 канал A приобретает свойство двунаправленной шины, управляемой опять же отдельными битами канала C. Кроме того, возможны установка и сброс отдельных битов канала C. Микросхема выпускается в 40-выводном DIP-корпусе. Основные особенности микросхемы: 3 канала ввода/вывода, 8 бит каждый; 3 режима работы (1 – статический ввод/вывод, 2 – тактируемый ввод/вывод, 3 – двунаправленный ввод/вывод); раздельное программирование каждого канала на ввод или вывод.  Рис. 7 13. Описание структуры и функционирование.Структурная схема программируемого периферийного адаптера представлена на рис. 1.  Рис.8 ППИ структурно разбит на две группы (A и B). Группа A включает в себя канал A и старшую тетраду канала C. Группа B состоит из канала B и младшей тетрады канала C. Доступ к каналам ввода/вывода и регистру управления осуществляется с помощью логики чтения-записи в соответствии с табл. 6. Таблица 6. Доступ к каналам ввода/вывода и регистру управляющего слова

Назначение этих и остальных выводов микросхемы приведено в табл. 7. Таблица 7. Назначение выводов

Первоначальное включение или подача сигнала высокого уровня на вход сброс RESET микросхемы переключает все каналы (A, B, C) в режим 0, одновременно переводя их в режим ввода. Сброс выполняется только при условии /RD = 0 и /WR = 0. Режим работы и направление передачи для каждого канала задается с помощью записи управляющего слова в регистр управления в соответствии с табл. 8 или 9. Отметим возможность комбинирования режимов работы для разных каналов. К примеру, канал B может быть запрограммирован на вывод в режим 0 для управления различными выключателями и реле, в то время как канал A может быть запрограммирован в режим 1 для ввода с клавиатуры или перфоленты. Таблица 8. Формат управляющего слова для выбора режима работы

Таблица 9. Формат управляющего слова для двунаправленного режима.

Каждый из восьми битов канала C может быть независимо от других установлен или сброшен с помощью специальной команды вывода, посылаемой в регистр управления. Это свойство канала C облегчает программирование в случае, когда биты канала C используется для управления передачей данных по каналам A или B. Формат команды приведен в табл. 10. Работа микросхемы в режиме 1 или 2 характеризуется наличием управляющих сигналов, которые могут вызывать прерывание работы процессора I8086. Команда установки или сброса соответствующего бита канала C позволяет запретить или разрешить выдачу требуемого прерывания. Таблица 10. Оперирование битами

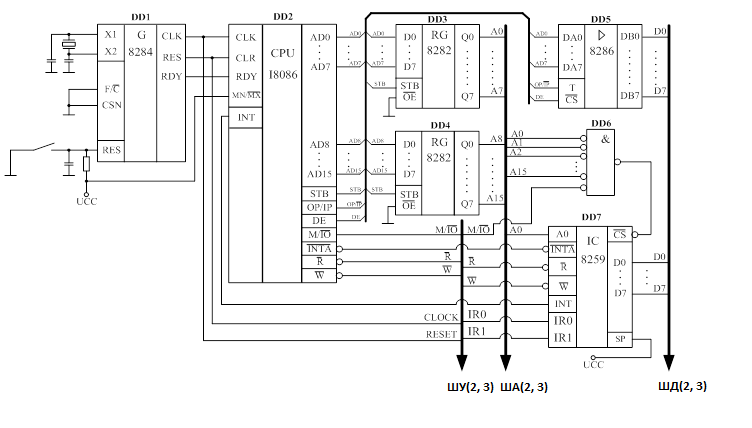

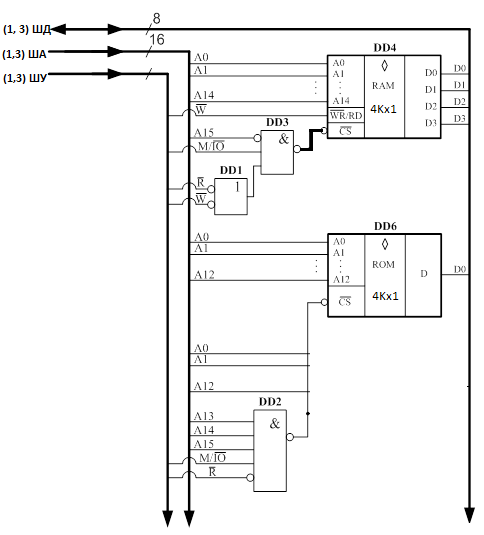

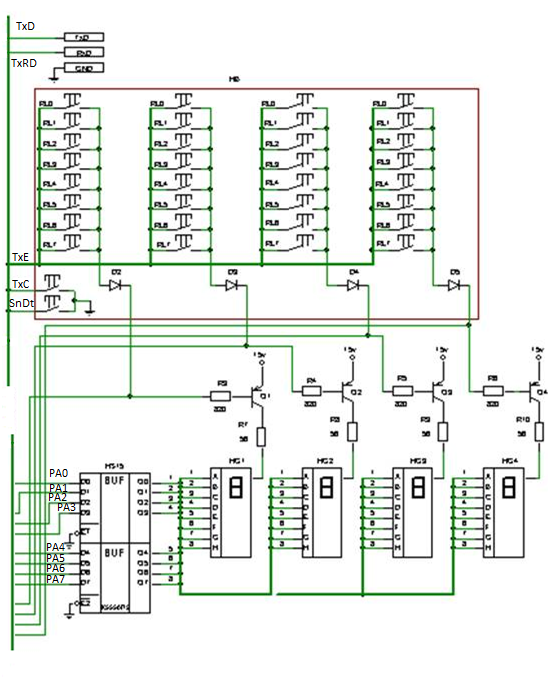

14. Выводы.В ходе выполнения работы была просмотрена и изучена документация на зарубежные микросхемы I8086,I8251, I8255. Были закреплены знания полученные из лекционного курса данного предмета. Приложение 1. Структурная схема МПС Рис. 9. Структурная схема МПС Приложение 2. Функциональная схема МПС Рис. 10. Функциональная схема МПС – часть 1  Рис. 11. Функциональная схема МПС – часть 2  Рис. 12. Функциональная схема МПС – часть 3  Рис. 13. Функциональная схема МПС. Периферийные устройства Приложение 3. Спецификация

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||