Часть III. Описание архитектуры учебной эвм

Скачать 2.15 Mb. Скачать 2.15 Mb.

|

Учебная модель ЭВМ: блок таймеровБлок таймеров включает три однотипных канала таймеров Т1(адрес 1), Т2(адрес 3), Т3 (адрес 5) со своими регистрами управления CT1R(адрес 2), CT2R (адрес 4), CT3R (адрес 6) и общий регистр состояний SR (адрес 0).  Каждый таймер может независимо работать в режиме реверсивного счётчика меток времени. Следует отметить, что длительность такта полагалась (весьма условно!) равной 1 мс, но реально она значительно больше и зависит от машины, на которой работает модель. Например, на моей машине такт таймера равен примерно 0,016 с. Каждый таймер снабжен предделителем с коэффициентом деления от 1 до 99, что позволяет выбирать диапазон измеряемых отрезков времени в широких пределах. Таймеры могут работать как на сложение, так и на вычитание. Переход 99999 => 0 при сложении или 0 => 99999 при вычитании вызывают установку в «1» соответствующего флага переполнения в регистре SR: Т1 – в пятом (младшем) разряде регистра SR, Т2 – в четвёртом разряде, Т3 – в третьем разряде и формирование запроса на прерывание, если прерывание от соответствующего таймера разрешено. При этом счёт в таймере не прекращается. Все шестиразрядные регистры управления таймерами имеют одинаковый формат: разряд 0 (старший) – не используется; разряды 1 и 2 задают коэффициент К деления предделителя от 01 до 99; разряд 3 определяет направление счёта: «0» – инкремент, «1» – декремент; разряд 4, будучи установленным в «1», разрешает формирование запроса на прерывание при переполнении этого таймера; разряд 5 включает («1») или выключает («0») счёт. Сброс флагов переполнения таймеров в регистре SR осуществляется только программно по командам:

Константы кодов этих команд должны выводится по адресу 0 блока таймеров (регистра SR). Пример простой программы: подавать короткий звуковой сигнал каждые 10 сек. Напомним, что такт таймера может изменяться в зависимости от ЭВМ, на которой работает модель. Если считать, что длительность такта составляет 16 мс, то для отсчёта отрезка времени в 10 сек. потребуется 10000 / 16 = 625 тактов.

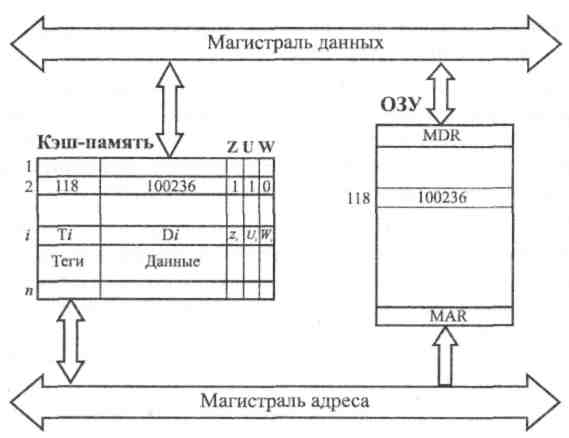

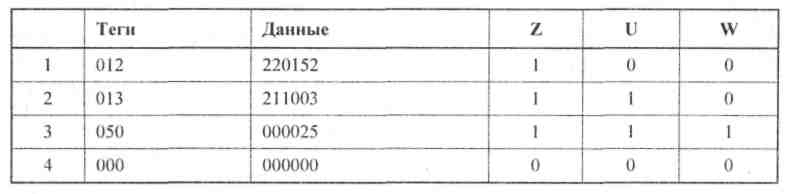

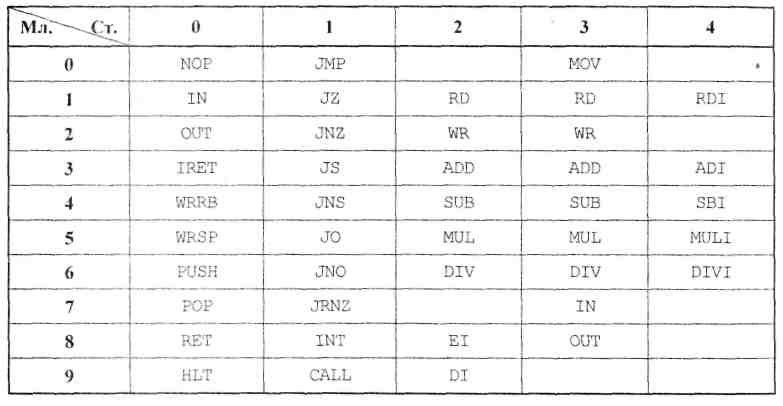

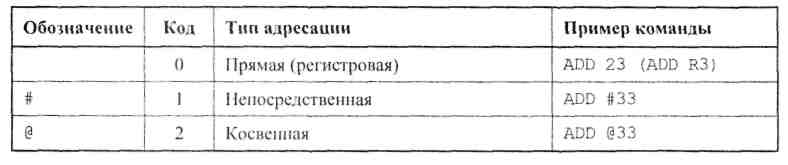

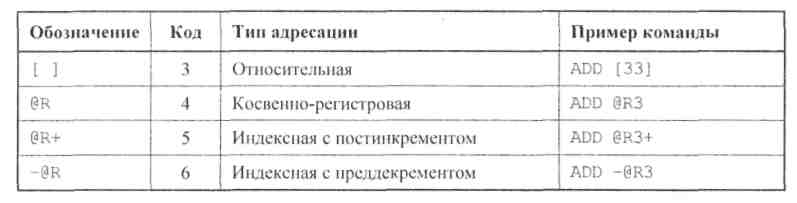

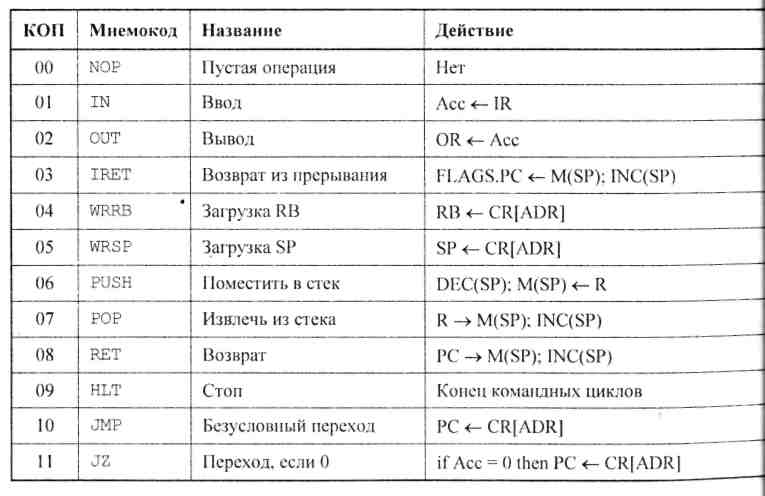

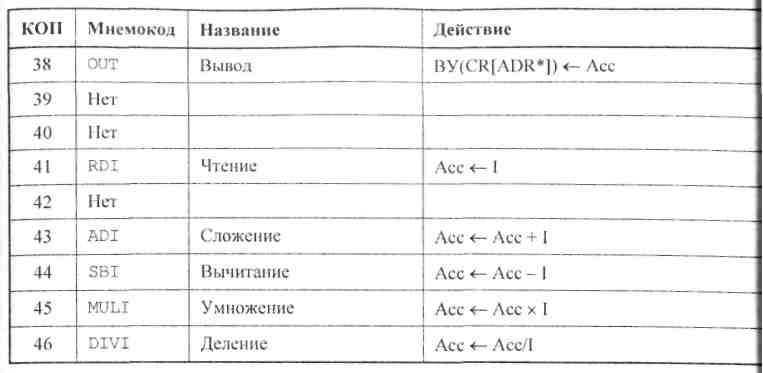

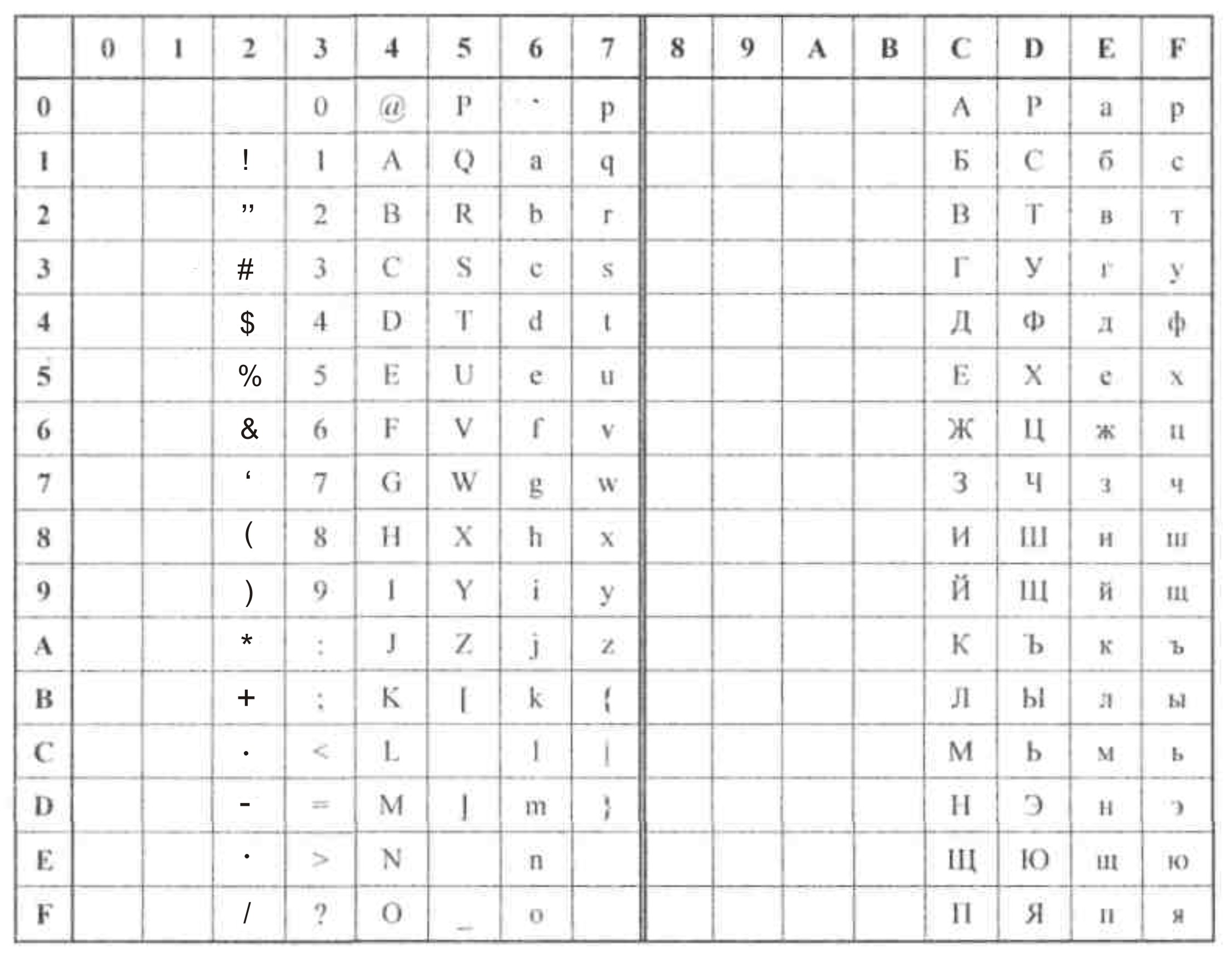

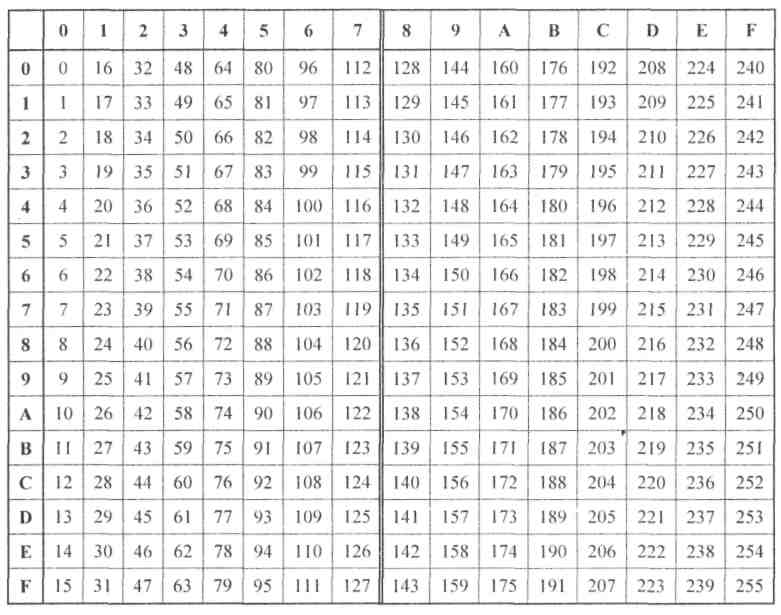

Внимание. Перед запуском этого примера следует подключить к системе не только блок таймеров, но и тоногенератор. 8.6.4. Тоногенератор Тоногенератор предназначен для вывода тона одной заданной частоты и заданной длительности на встроенный динамик ПЭВМ. Модель этого простого внешнего устройства не имеет собственного обозревателя, содержит всего два регистра, доступных только для записи: FR – регистр частоты (адрес 0), в который записывается частота тона звучания в герцах; LR – регистр длительности звучания (адрес 1), в который задаётся время звучания в миллисекундах. Команда вывода числа по этому адресу одновременно с заданием длительности звучания является командой на начало звучания. По умолчанию базовый адрес тоногенератора — 30. Сначала следует записать в FR требуемую частоту тона в герцах, затем в LR — длительность звучания в миллисекундах. Запись числа по адресу регистра LR одновременно является командой на начало звучания. По умолчанию базовый адрес тоногенератора – 30. Использование тоногенератора рассмотрено в примере на странице Блок таймеров. 8.7. Подсистема прерываний В модели учебной ЭВМ предусмотрен механизм векторных внешних прерываний. Внешние устройства формируют запросы на прерывания, которые ступают на входы контроллера прерываний. При подключении ВУ, способного формировать запрос на прерывание, ему ставится в соответствие номер входа контроллера прерываний — вектор прерывания, принимающий значение в диапазоне 0—9. Контроллер передает вектор, соответствующий запросу, процессору, который начинает процедуру обслуживания прерывания. Каждому из возможных в системе прерываний должен соответствовать т.н. обработчик прерывания — подпрограмма, вызываемая при возникновении события конкретного прерывания. Механизм прерываний, реализованный в модели учебной ЭВМ, поддерживает таблицу векторов прерываний, которая создается в оперативной памяти моделью операционной системы (если она используется) или непосредственно пользователем. Номер строки таблицы соответствует вектору прерывания, а элемент таблицы — ячейка памяти, в трех младших разрядах которой размещается начальный адрес подпрограммы, обслуживающей прерывание с этим вектором. Таблица прерываний в рассматриваемой модели жестко фиксирована — занимает ячейки памяти с адресами 100—109. Таким образом, адрес обработчика с вектором 0 должен располагаться в ячейке 100, с вектором 2 — в ячейке 102. При работе с прерываниями не рекомендуется использовать ячейки 100—109 для других целей. Процессор начинает обработку прерывания (если они разрешены), завершив текущую команду. При этом он: Получает от контроллера вектор прерывания. Формирует и помещает в верхушку стека слово, три младших разряда ([3:5]) которого — текущее значение РС (адрес возврата из прерывания), а разряды [1:2] сохраняют десятичный эквивалент шестнадцатеричной цифры, определяющей значение вектора флагов (I, OV, S, Z). Например, если I=1, OV = 0, S = 1, Z= 1, то в разряды [1:2] запишется число 1110 =10112 . Сбрасывает в 0 флаг разрешения прерывания I. Извлекает из таблицы векторов прерываний адрес обработчика, соответствующий обслуживаемому вектору, и помещает его в РС, осуществляя тем самым переход на подпрограмму обработчика прерывания. Таким образом, вызов обработчика прерывания, в отличие от вызова подпрограммы, связан с помещением в стек не только адреса возврата, но и текущего значения вектора флагов. Поэтому последней командой подпрограммы обработчика должна быть команда IRET, которая не только возвращает в РС три младшие разряда ячейки — верхушки стека (как RET), но и восстанавливает те значения флагов, которые были в момент перехода на обработчик прерывания. Не всякое событие, которое может вызвать прерывание, приводит к прерыванию текущей программы. В состав процессора входит программно-доступный флаг I разрешения прерывания. При I = 0 процессор не реагирует на запросы прерываний. После сброса процессора флаг I так же сброшен и все прерывания запрещены. Для того чтобы разрешить прерывания, следует в программе выполнить команду EI (от англ. епаblе interrupt). Выше отмечалось, что при переходе на обработчик прерывания флаг I автоматически сбрасывается, в этом случае прервать обслуживание одного прерывания другим прерыванием нельзя. По команде IRET значение флагов восстанавливается, в т. ч. вновь устанавливается I=1, следовательно, в основной программе прерывания опять разрешены. Если требуется разрешить другие прерывания в обработчике прерывания, достаточно в нем выполнить команду EI. Контроллер прерываний и процессор на аппаратном уровне блокируют попытки запустить прерывание, если его обработчик начал, но не завершил работу. Таким образом, флаг I разрешает или запрещает все прерывания системы. Если требуется выборочно разрешить некоторое подмножество прерываний, используются программно-доступные флаги разрешения прерываний непосредственно на внешних устройствах. Как правило, каждое внешнее устройство, которое может вызвать прерывание, содержит в составе своих регистров разряд флага разрешения прерывания (см. формат регистров CR и CTR на рис. 8.9, 8.13), по умолчанию установленный в 0. Если оставить этот флаг в нуле, то внешнему устройству запрещается формировать запрос контроллеру прерываний. Иногда бывает удобно (например, в режиме отладки) иметь возможность вызвать обработчик прерывания непосредственно из программы. Если использовать для этих целей команду CALL, которая помещает в стек только адрес возврата, то команда IRET, размещенная последней в обработчике, может исказить значения флагов (все они будут сброшены в 0, т. к. команда CALL формирует только три младшие разряда ячейки верхушки стека, оставляя остальные разряды в 000). Поэтому в системах команд многих ЭВМ, в т. ч. и нашей модели, имеют команды вызова прерываний— INT n (в нашей модели n {0, 1, ..., 9}), где n — вектор прерывания. Процессор, выполняя команду, производит те же действия, что и при обработке прерывания с вектором n. Характерно, что с помощью команды INT n можно вызвать обработчик прерывания даже в том случае, когда флаг разрешения прерывания I сброшен. 8.8. Программная модель кэш-памяти К описанной в разд. 8.1 программной модели учебной ЭВМ может быть подключена программная модель кэш-памяти, структура которой в общем виде отображена на рис. 5.2. Конкретная реализация кэш-памяти в описываем программной модели показана на рис. 8.15. Кэш-память содержит N ячеек (в модели N может выбираться из множества {4, 8, 16, 32}), каждая из которых включает трехразрядное поле тега (адреса ОЗУ), шестиразрядное поле данных и три однобитовых признака (флага) Z — признак занятости ячейки; U — признак использования; W — признак записи в ячейку. Таким образом, каждая ячейка кэш-памяти может дублировать одну любую ячейку ОЗУ, причем отмечается ее занятость (в начале работы модели все ячейки кэш-памяти свободны, Zi = 0), факт записи информации в ячейку во время пребывания ее в кэш-памяти, а также использование ячейки (т. е. любое обращение к ней).  Рис. 8.15. Структура модели кэш-памяти Текущее состояние кэш-памяти отображается на экране в отдельном окне в форме таблицы, причем количество строк соответствует выбранному числу ячеек кэш. Столбцы таблицы определяют содержимое полей ячеек, например, так, как показано в табл. 8.3.  Таблица 8.3. Пример текущего состояния кэш-памяти Для настройки параметров кэш-памяти можно воспользоваться диалоговым окном Кэш-память, вызываемым командой Вид | Кэш-память, а затем нажать первую кнопку на панели инструментов открытого окна. После этих действий появится диалоговое окно Параметры кэш-памяти, позволяющее выбрать размер кэш-памяти, способ записи в нее информации и алгоритм замещения ячеек. Напомним, что при сквозной записи при кэш-попадании в процессорных циклах записи осуществляется запись как в ячейку кэш-памяти, так и в ячейку ОЗУ, а при обратной записи — только в ячейку кэш-памяти, причем эта ячейка отмечается битом записи (Wi: =1). При очистке ячеек, отмеченных битом записи, необходимо переписать измененное значение ноля данных соответствующую ячейку ОЗУ. При кэш-промахе следует поместить в кэш-память адресуемую процессором ячейку. При наличии свободных ячеек кэш-памяти требуемое слово помещается в одну из них (в порядке очереди). При отсутствии свободных ячеек следует отыскать ячейку кэш-памяти, содержимое которой можно удалить, записав на его место требуемые данные (команду). Поиск такой ячейки осуществляется с использованием алгоритма замещения строк. В модели реализованы три различных алгоритма замещения строк: случайное замещение, при реализации которого номер ячейки кэш-памяти выбирается случайным образом; очередь, при которой выбор замещаемой ячейки определяется временем пребывания ее в кэш-памяти; бит использования, случайный выбор осуществляется только из тех ячеек, которые имеют нулевое значение флага использования. Напомним, что бит использования устанавливается в 1 при любом обращении к ячейке, однако, как только все биты Uiустановятся в 1, все они тут сбрасываются в 0, так что в кэш всегда ячейки разбиты на два непересекающихся подмножества по значению бита U — те, обращение к которым стоялось относительно недавно {после последнего сброса вектора U) имеют значение U= 1, иные— со значением U = 0 являются "кандидатами на удаление" при использовании алгоритма замещения "бит использования". Если в параметрах кэш-памяти установлен флаг "с учетом бита записи", товсе три алгоритма замещения осуществляют поиск "кандидата на удаление" прежде всего среди тех ячеек, признак записи которых не установлен, а при отсутствии таких ячеек (что крайне маловероятно) — среди всех ячеек кэш-памяти. При снятом флаге "с учетом бита записи" поиск осуществляется всем ячейкам кэш-памяти без учета значения W. Оценка эффективности работы системы с кэш-памятью определяется числом кэш-попаданий по отношению к общему числу обращений к памяти. Учитывая разницу в алгоритмах записи в режимах сквозной и обратной записи, эффективность использования кэш-памяти вычисляется по следующим выражениям (соответственно для сквозной и обратной записи):  (8.2) (8.3) где: K — коэффициент эффективности работы кэш-памяти; SO — общее число обращений к памяти; SK— число кэш-попаданий; S — число обратных записей (в режиме обратной записи). 8.9. Вспомогательные таблицы В данном разделе представлены вспомогательные таблицы (табл. 8.4—8.8) для работы с моделью учебной ЭВМ. Таблица 8.4. Таблица команд учебной ЭВМ  Таблица 8.5. Типы адресации, их коды и обозначение  Таблица 8.5 (окончание)  В табл. 8.6 приняты следующие обозначения: DD — данные, формируемые командой в качестве (второго) .операнда прямо или косвенно адресуемая ячейка памяти или трехразрядный непосредственный операнд; R* — содержимое регистра или косвенно адресуемая через регистр ячейка памяти; ADR* — два младших разряда ADR поля регистра CR; V — адрес памяти, соответствующий вектору прерывания; М(*) — ячейка памяти, прямо или косвенно адресуемая в команде; I — пятиразрядный непосредственный операнд со знаком. Таблица 8.6. Система команд учебной ЭВМ   Таблица 8.6. (продолжение) Таблица 8.6 (окончание)  Таблица 8.7. Таблица кодов ASII (фрагмент]  Таблица 8.8. Перевод НЕХ-кодов в десятичные числа  |