Основы построения схем в пакете Quartus II. Косарев_Цфира2. Основы построения схем в пакете Quartus ii

Скачать 183.8 Kb. Скачать 183.8 Kb.

|

|

| Студент гр.1402 | | Косарев А.М. |

| Преподаватель | | Богданов Д.В. |

Санкт-Петербург

2023

Цель работы:

Изучить минимизацию ПФ с помощью диаграмм Вейча и представить полученную минимизированную функцию в виде схемы Quartus II с помощью блок-диаграмм и на языке Verilog.

Задание:

1. Собрать схему (в графическом и текстовом редакторе), заданную диаграммой Вейча

2. Найти МДНФ переключательной функции.

3. Построить таблицу истинности для заданной функции.

4. Построить временные диаграммы при наличии и отсутствии задержек.

5. Показать результат работы компонента RTL Viewer.

6. Запрограммировать отладочную плату. При этом указать входные сигналы на SW1-4, а выходной на LED2.

Обработка:

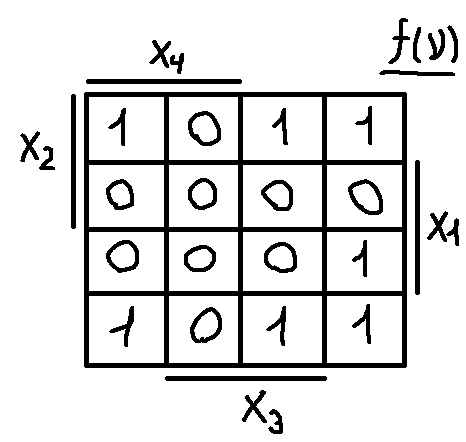

МДНФ:

Таблица истинности:

| X1 | X2 | X3 | X4 |  |  |  |  |  |  |  |  |

| 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 0 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 1 | 0 | 0 | 1 |

| 0 | 0 | 1 | 0 | 1 | 1 | 0 | 1 | 0 | 1 | 0 | 1 |

| 0 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 |

| 0 | 1 | 0 | 0 | 1 | 0 | 1 | 1 | 1 | 1 | 0 | 1 |

| 0 | 1 | 0 | 1 | 1 | 0 | 1 | 0 | 1 | 0 | 0 | 1 |

| 0 | 1 | 1 | 0 | 1 | 0 | 0 | 1 | 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 0 | 0 | 1 | 1 |

| 1 | 0 | 0 | 1 | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 | 0 | 1 | 0 | 1 | 0 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 |

| 1 | 1 | 0 | 0 | 0 | 0 | 1 | 1 | 0 | 0 | 0 | 0 |

| 1 | 1 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 |

| 1 | 1 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 |

| 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

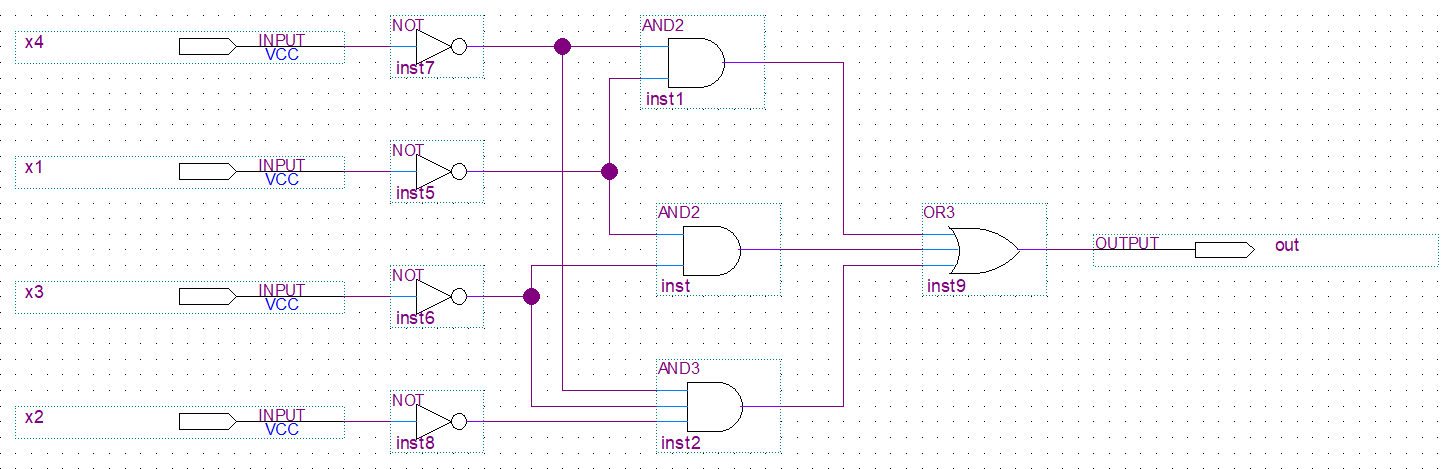

3) Схемы из блок-диаграмм и на Verilog:

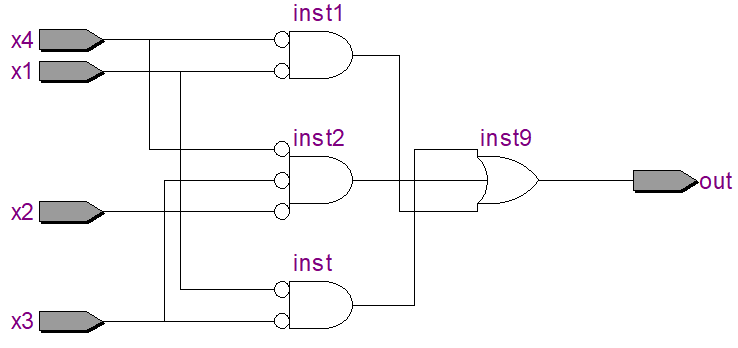

а) Блок-диаграмма:

б) Представление схемы из блок-диаграмм в RTL Viewer:

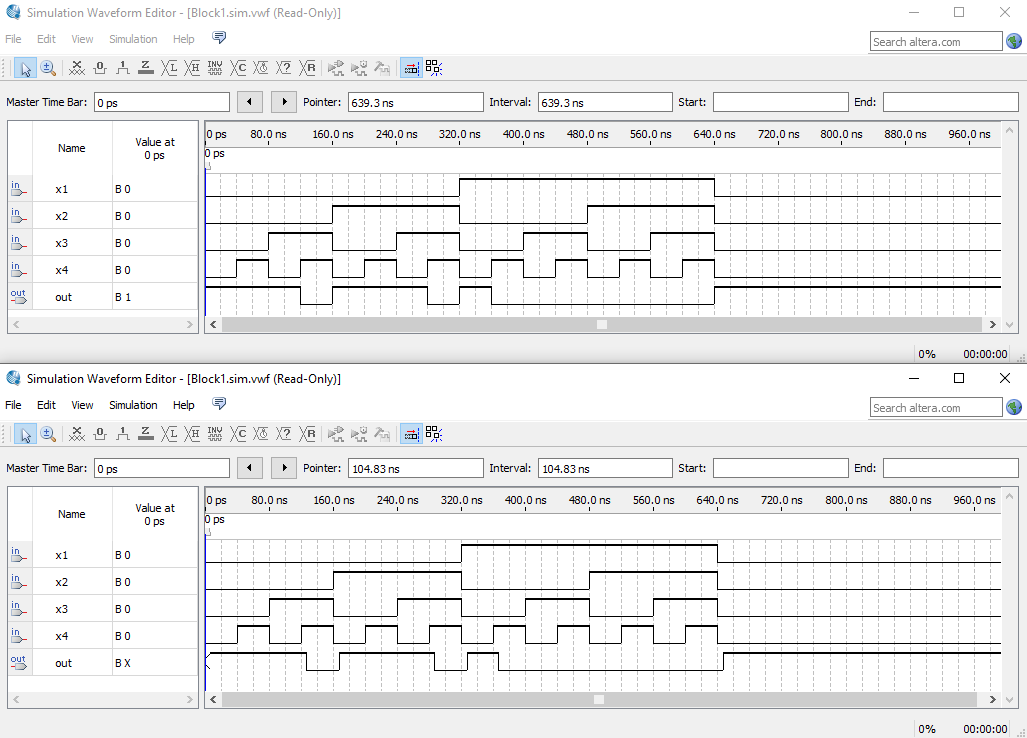

4) Осциллограмма работы схемы из блок-диаграмм без задержек и с задержками соответственно:

5) Схема на Verilog:

module lab2(x1,x2,x3,x4,out);

input x1,x2,x3,x4;

output out;

assign out=((x1)&(x3))|((x4)&(x1))|((x3)&(x2)&(x4));

endmodule

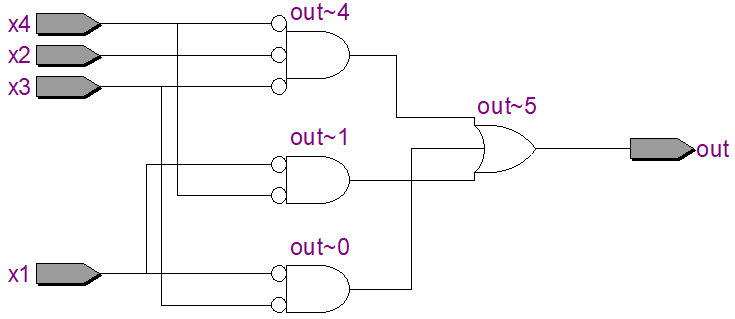

6) Схема на Verilog в RTL

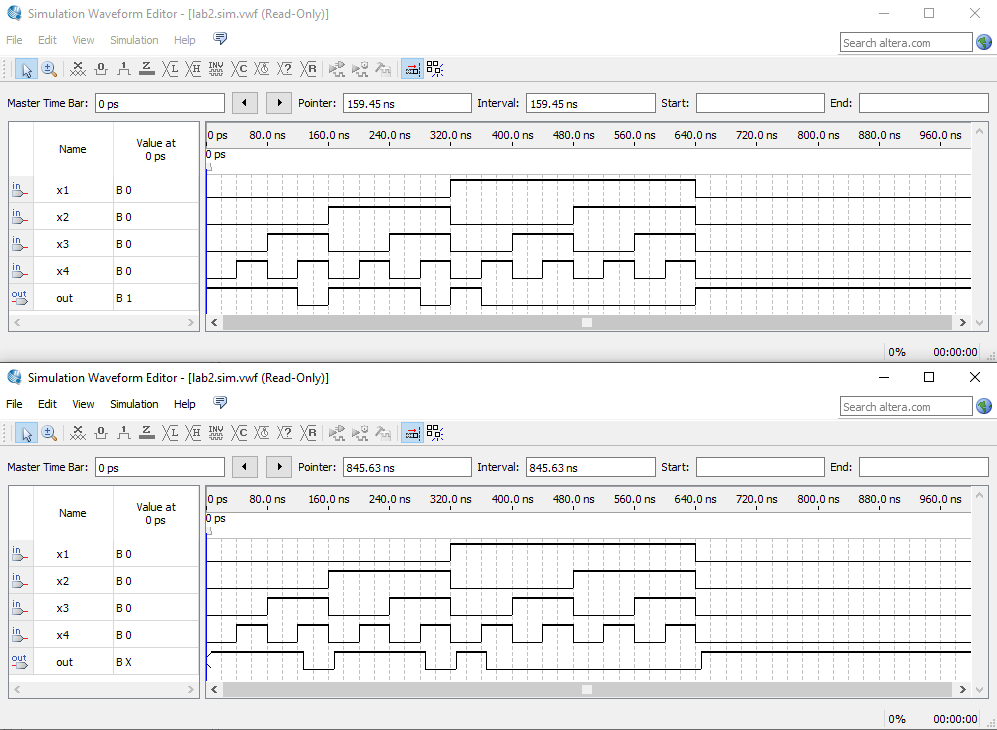

7) Осциллограмма работы схемы на Verilog с без задержек и с их учётом соответственно:

Вывод:

В данной лабораторной работе мы укрепили наши практические навыки минимизирования переключательных функций по диаграммам Вейча, а также укрепили опыт создания схем в среде Quartus II.