Компаратор на Verilog. Отчет по лабораторной работе 2 по дисциплине Схемотехника Тема Компаратор Студент гр. 0363 Барков М. О. Преподаватель

Скачать 257.23 Kb. Скачать 257.23 Kb.

|

|

| Студент гр. 0363 | | Барков М. О. |

| Преподаватель | | Фахми Ш. С |

Санкт-Петербург

2021

Цель работы.

Разработать на языке описания схем Verilog восьмиразрядный компаратор.

Основные теоретические положения.

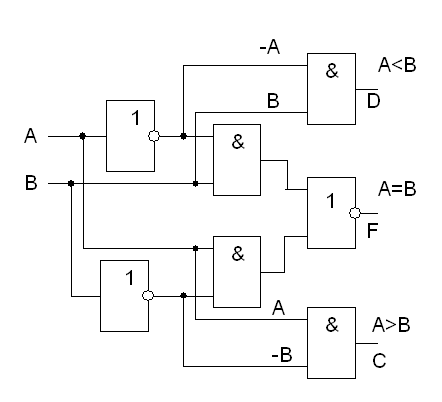

Цифрово́й компара́тор или компара́тор ко́дов логическое устройство с двумя словарными входами, на которые подаются два разных двоичных слова равной в битах длины и обычно с тремя двоичными выходами, на которые выдаётся признак сравнения входных слов, — первое слово больше второго, меньше или слова равны. Может быть построен на логических элементах, работа которых основана на самых различных физических принципах, но современные компараторы обычно представляют собой полупроводниковые электронные устройства работающие в двоичной логике.

Таблица истинности компаратор

| D0 D1 | Y0 | Y1 | YR |

| D0 > D1 | 1 | 0 | 0 |

| D0 < D1 | 0 | 1 | 0 |

| D0 = D1 | ? | ? | 1 |

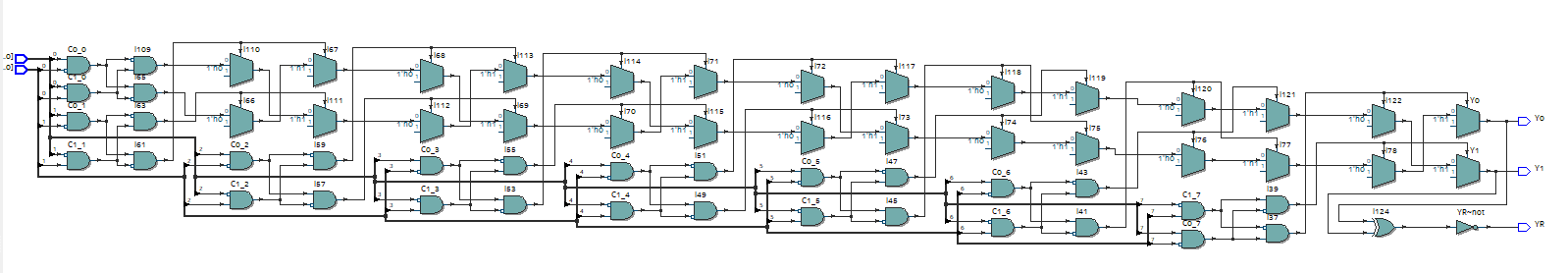

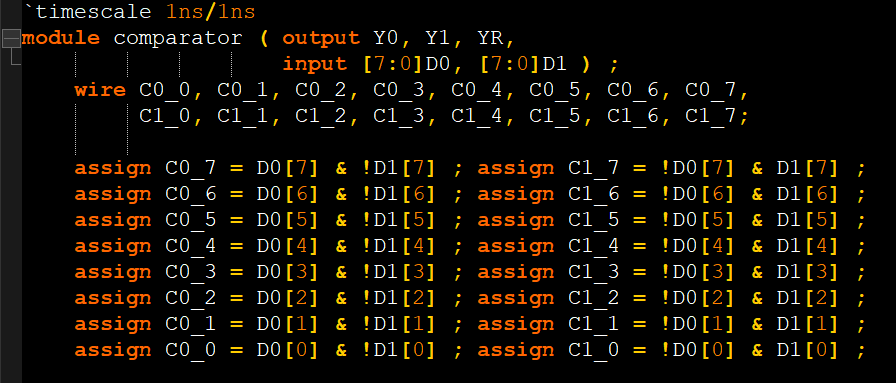

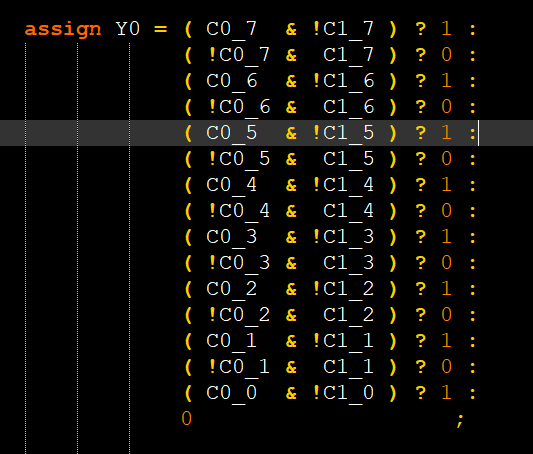

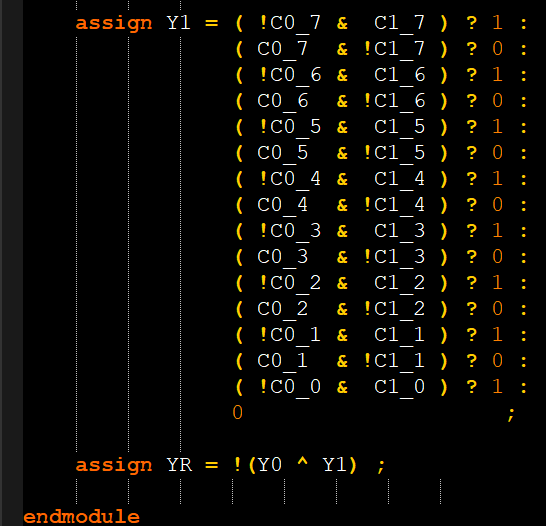

Разработка Verilog кода схемы компаратора

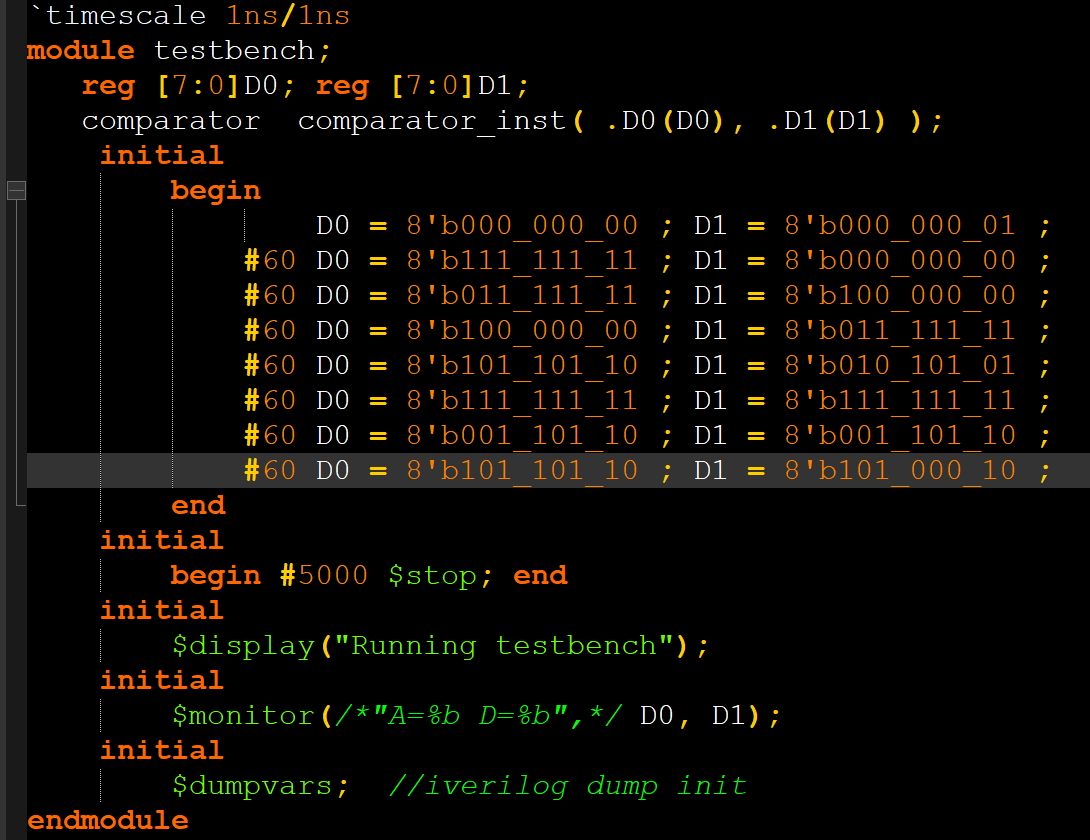

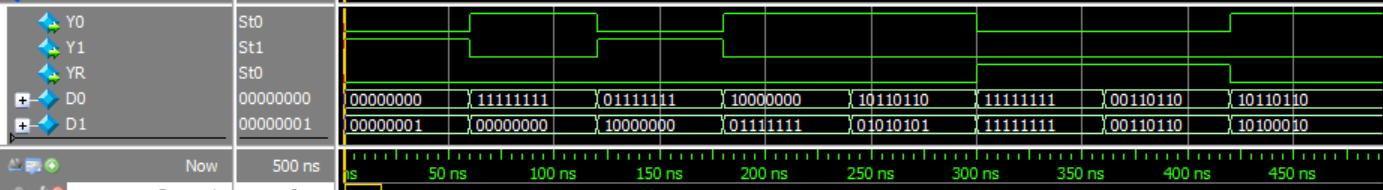

Временная диаграмма компаратора

Примеры использования

Выводы

Используемая литература

http://library.tsilikin.ru/rus-verilog.pdf - документация Verilog HDL на русском языке

Книга по лекциям - Цифровая схемотехника 2013 г. Дэвид М. Харрис и Сара Л. Харрис