Ответы(Схем)11-20. Полным дешифратором называется устройство, имеющее

Скачать 1.11 Mb. Скачать 1.11 Mb.

|

| |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| d0 | 0 | DC | 0 1 | | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| q | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| d1 | q | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| 1 | | 2 | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| | q | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| | | 3 | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| |

| d1d0 | q3q2q1q0 | hex |

| 0 0 | 0 0 0 1 | 1 |

| 0 1 | 0 0 1 0 | 2 |

| 1 0 | 0 1 0 0 | 4 |

| 1 1 | 1 0 0 0 | 8 |

q0

.q1

.q1  d0 . q2

d0 . q2

; q3 d1 d0 .

; q3 d1 d0 .По данным формулам несложно составить схему (Рис. 5.24) и описание на Verilog (Пример 5.4.). В схеме дешифратора для формирования каждого выходного

//Пример 5.10. Дешифратор module v510_dc (a, q); //2

//Пример 5.10. Дешифратор module v510_dc (a, q); //2input [1:0] d; //3

output [3:0] q; //4 assign q[3] = d[1] & d[0] ; //5 assign q[2] = d[1] & d[0] ;//6 assign q[1] = d[1] & d[0] ;//7 assign q[0] = d[1] & d[0] ;//8 endmodule //9

сигнала используется отдельный логический элемент.

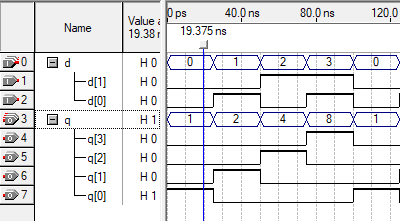

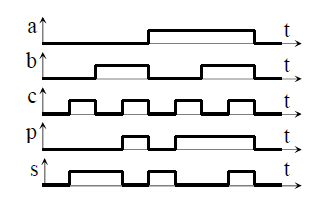

Работа дешифратора должна соответствовать временным диаграммам (Рис. 5.25).

Дешифратор, дополненный общим разрешающим входом, называется дешифратором – демультиплексором

12. Приоритетный шифратор, назначение, принцип работы, синтез (таблица истинности, логические функции, схема, временные диаграммы, описание на языке Verilog) типы, применение.

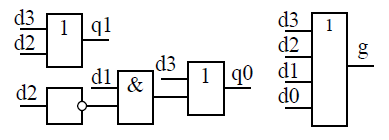

Шифратор (Рис. 5.28) выполняет функцию, противоположную дешифратору, он преобразует сигнал, равный единице только на одном из входов, в двоичный код. При возбуждении одной из входных цепей шифратора на его выходах формируется слово, отображающее номер возбужденной цепи. Полный двоичный шифратор имеет 2Nвходов и Nвыходов. Шифраторы применяют для ввода кода нажатой клавиши, для определения номера устройства, подавшего запрос на прерывание.

| | 1 | q |

| d2 | ||

| | ||

| |

d3 1

d3

&

d2 d1

d3

1

d2 g

1

q0 d1 d0

Рис. 5.28 Обозначение шифратора

Рис. 5.29 Схема шифратора

Таблицу истинности для шифратора в простейшем случае можно получит

Таблица 5.8.

из таблицы 5.6, поменяв местами входы и выходы. В реальных условиях, при воздействии помех, может быть возбуждено несколько входных проводников. Поэтому схему шифратора усложняют, делают ее приоритетной (Таблица 5.8). Приоритетный шифратор вырабатывает на выходе двоичный номер старшего запроса. При наличии всего одного запроса приоритетный шифратор работает так же, как и двоичный. В интегральном исполнении изготавливают,

| d3 | d2 | d1 | d0 | q1 | q0 | g |

| 1 | х | х | х | 1 | 1 | 1 |

| 0 | 1 | х | х | 1 | 0 | 1 |

| 0 | 0 | 1 | х | 0 | 1 | 1 |

| 0 | 0 | 0 | 1 | 0 | 0 | 1 |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 |

как правило, приоритетные шифраторы. В приведенной таблице d3..d0 – входные сигналы, q1..q0 – выходной код, g – выходной сигнал, отмечающий наличие запросов.

По таблице записаны формулы для выходных сигналов, для упрощения

которых, использовано тождество: a a x a x.

Рис. 5.30 Работа приоритетного шифратора

//Пример 5.10. Дешифратор

//Пример 5.10. Дешифратор module v510_dc (a, q,q1); //2

[3:0] d; //3

input [1:0] q; //4

input q1; //5

assign q1 = d[3] | d[2] | d[1] | d[0] ;//6

assign q[1] = d[3] | d[2] ;//7

assign q[0] = d[3] | d[2] & d[1] ;//8

endmodule //9

13. Дешифратор - демультиплекмор, назначение, принцип работы, синтез (таблица истинности, логические функции, схема, временные диаграммы, описание на языке Verilog) типы, применение.

Дешифратор, дополненный общим разрешающим входом, называется дешифратором – демультиплексором (Рис.5.26).

Наличие дополнительных входов разрешения, которых может быть

несколько, позволяет разрешать, или запрещать работу устройства. Для того, чтобы входные сигналы (d1, d0) вызывали изменения выходных сигналов (q3..q0), необходимо подать разрешающий сигнал e=1. В этом случае, как и в предыдущей схеме, на одном из выходов, номер которого определяет адрес, формируется сигнал, равный 1. При е=0 все выходные сигналы запрещены, и равны нулю.

е q0

е q0 q1

q1 q2 q3

q2 q3Рис.5.26

Дешифратор - демультиплексор

a1 a0

Рис.5.27. Пояснение

работы демультиплексора

| е | d 1 | d0 | q3 | q2 | q1 | q0 |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 | 0 | 0 | 0 |

| 0 | 1 | 0 | 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 0 | 0 | 0 | 1 |

| 1 | 0 | 1 | 0 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 | 1 | 0 | 0 |

| 1 | 1 | 1 | 1 | 0 | 0 | 0 |

В названии схемы отражена возможность ее применения в качестве демультиплексора, что поясняет рис. 5.27.

Демультиплексоры выполняют функцию, обратную мультиплексорам, они производят коммутацию одного информационного входного сигнала на 2mвыходов, где m- число адресных входов. При этом в качестве информационного входа демультиплексора используется разрешающий вход «е».

Таблица истинности для дешифратора- демультиплексора (таблица 5.7) позволяет разработать его схему и составить описание.

Выходы и разрешающие входы дешифраторов, выполненных интегрально, могут быть инверсными. Так, например, дешифратор-демультиплексор с инверсными выходами и инверсным разрешающим входом

CSформирует при CS=0 нулевой логический сигнал на одном из выходов, в соответствии с адресом на входах. При CS=1 все выходные сигналы равны 1.

5.10. Дешифратор-Демультиплексор module v510_dc (a, q, e); //2

input [1:0] d; //3

output [3:0] q; //4

assign q[3] = d[1] & d[0] & e ; //5

assign q[2] = d[1] & d[0] & e; //6

assign q[1] = d[1] & d[0] & e;//7

assign q[0] = d[1] & d[0] & e;//8

endmodule //9

Рис. 5.36. Компаратор кодов

Данная логическая функция позволяет составить схему, формирующую признак равенства кодов, а также описание на языке Verilog (Пример 5.13).

Для построения схемы сравнения положительных чисел, представленных в прямом коде без знака, и формирующей признак G, необходимо сравнить коды чисел, начиная со старшего разряда.

Признак G будет равен 1, если в старшем разряде числа А записана 1, а в старшем разряде числа В записан 0, остальные разряды на результат уже не влияют. Если старшие разряды равны, то значение признака будут определять следующие разряды, G=1, если следующий разряд числа А - единица, а числа В - ноль . Рассуждая таким образом можно рассмотреть все разряды чисел и записать логическую функцию.

G A3 B3 E3 A2 B2 E3 E2 A1 B1 E3 E2 E1 A0 B0

Признаки равенства отдельных разрядов определяют очевидные формулы:

E3 ( A3 B3 );

E2 ( A2 B2 );

E1 ( A1 B1 );

E0 ( A0 B0 );

Полученные формулы позволяют составить схему, а также описание компаратора кодов, формирующего признак G – больше. Функциональные возможности языка Verilog позволяют составить компактное и наглядное поведенческое описание, компараторов кодов, в в которых используются операторы сравнения, описанные в главе 3. Операторы сравнения формируют одноразрядные сигналы - результат сравнения векторов (параллельных кодов).

//Пример 5.14. Компаратор module v514_compar ( a, b, e, g, l);

//Пример 5.14. Компаратор module v514_compar ( a, b, e, g, l);input [3:0]a, b; //3

output e, g, l; //4

assign e = a==b; //5

assign g = a>b; //6

ssign l = a

endmodule //8

Поведенческое описание компаратора, формирующего три основных признака отношения кодов – «меньше», «равно» и «больше» (Пример 5.14) составлено в соответствие с обозначением (Рис. 5.36). Входные сигналы компаратора – это 4-ех разрядные коды «а» и «b» , а выходные – признаки отношения кодов: равно «e», больше «g», меньше «l».

Теоретические временные диаграммы, поясняющие работу компаратора кодов, описанного в примере 5,15, приведены на рис. 5.37.

t t t t

t t t tt

Рис. 5.37. Работа компаратора кодов

Анализ постановки задачи

Рис. 5.9.

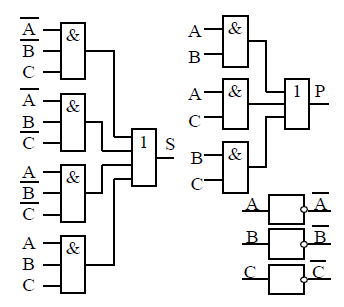

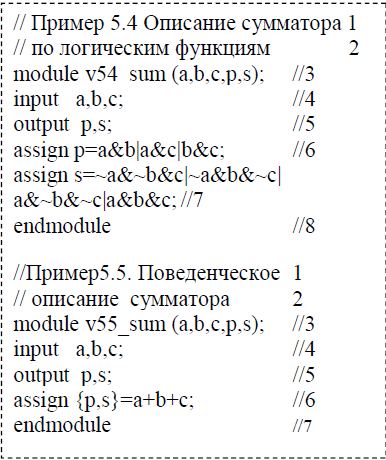

Обозначение сумматора младшего разряда (c) (Рис. 5.9).

Выходами схемы являются сумма для данного разряда (s) и перенос в следующий разряд (p). Сумматор, имеющий три входа, называют также «полным сумматором». Включая параллельно несколько подобных схем можно получить сумматор с произвольным числом разрядов (с последовательным переносом).

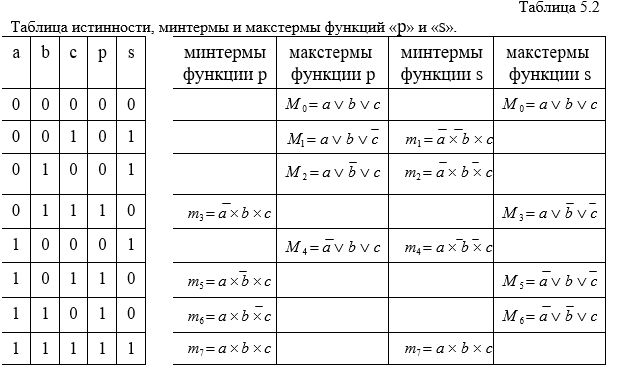

Для рассматриваемого устройства таблица истинности описывает логическую функцию трех переменных, следовательно, количество наборов входных сигналов, или строк таблицы равно 8. При составлении таблицы истинности (Таблица 5.2) учитываем, что значения переноса и суммы образуют двухразрядное двоичное число, равное количеству входных сигналов, равных единице. Если в строке таблицы только один из входов равен 1, то p=0, s=1; если два сигнала равны единице, то p=1, s=0;если три сигнала равны единице, то p=1, s=1.

В дополнение к таблице истинности приведены минтермы и макстермы функций «p» и «s», записанные в соответствии с правилами, рассмотренными в главе 4.

Составление логических функций

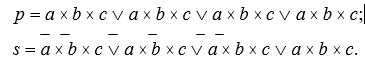

Логические функции в совершенной дизъюнктивной нормальной форме (СДНФ) представляет собой дизъюнкцию всех минтермов, число которых равно числу единиц логической функции в таблице истинности. Минтерм – произведение всех аргументов, записанное с соответствии с двоичным набором, на котором функция равна единице, над аргументами, которые в наборе равны нулю, в произведении ставится инверсия.

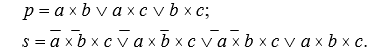

Логические функции для сигналов p и s в СДНФ имеют вид:

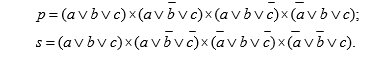

Для получения логических функций в совершенной конъюнктивной нормальной форме (СКНФ) записываются, в скобках, все макстермы и соединяются знаками умножения. Число сомножителей равно числу строк в

таблице истинности, для которых функция равна нулю. Каждый макстерм учитывает двоичный набор, на котором функция равна нулю, над аргументами, равными единице, в дизъюнкции ставится инверсия. Логические функции для сигналов p,sв СКНФ имеют вид:

После минимизации имеем:

Схема устройства строится по минимизированным логическим функциям (Рис. 2.11). В соответствии с постановкой задачи, схема содержит три входных и два выходных терминала (a,b,c,p,s).

Схема сумматора

Для формирования выходного сигнала «s» необходимы инверсные значения входных сигналов, для их формирования используются инверторы (элементы NOT).

//Инкрементор

module v54_inc d,c,q,p);

input [3:0] d; //3

input c ; //4

output [3:0] q; //5

output p; //6

assign {p,q} = d+c;//7

endmodule //8

| Преобразование двоичного кода в код Грея | Преобразование кода Грея в двоичный код |

|  |

Для обратного преобразования кода Грея в двоичный код старшие разряды также совпадают, но каждый следующий двоичный разряд двоичного кода получается суммированием по модулю два всех предыдущих разрядов кода Грея.

//Дополнительный код

module grey (a, r);

input [3:0] a;

output [3:0] r;

assign r = 1’h0 – a;

endmodule

//Обратный код

module grey (a, r);

input [3:0] a;

output [3:0] r;

assign r = 1’hF – a;

endmodule

//Код Гея

module grey (b, g);

input [3:0] b;

output [3:0] g;

assign g[3]=b[3];

assign g[2] = b[3]^b[2];

assign g[1] = b[2]^b[1];

assign g[0] = b[1]^b[0];

endmodule

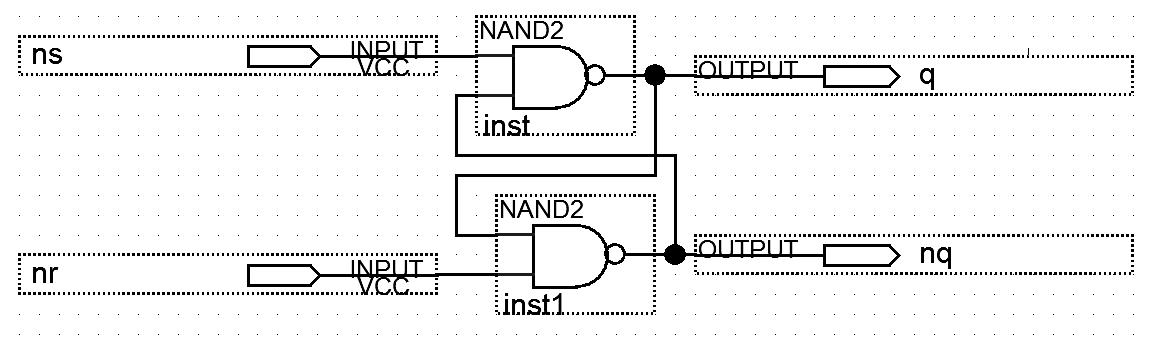

20. Статический асинхронный RS – триггер с установочными входами, назначение, пояснение принципа работы по схеме, таблица истинности, временные диаграммы.

Триггер - элемент памяти для хранения одного бита информации, устройство с двумя устойчивыми состояниями, Основу триггера составляет запоминающая ячейка из двух инвертирующих элементов, в которой действует положительная обратная связь, обеспечивающая наличие двух устойчивых состояний схемы.

В асинхронных триггерах запись нуля или единицы происходит под действием входного управляющего сигнала. В синхронных статических триггерах момент записи определяет уровень сигнала синхронизации. В синхронных динамических триггерах момент записи определяет изменения сигнала синхронизации – фронт или спад импульса.

Элементы И—НЕ, соединенные в замкнутую цепь, образуют

-триггера. Режим хранения информации, при котором в контуре действует положительная обратная связь, возникает при подаче на оба установочных входа сигнала 1, при этом логические элементы передают сигналы положительной обратной связи.

-триггера. Режим хранения информации, при котором в контуре действует положительная обратная связь, возникает при подаче на оба установочных входа сигнала 1, при этом логические элементы передают сигналы положительной обратной связи. Если в режиме хранения при

предположить q=0, то комбинация входных сигналов элемента dd2 с учетом выходного сигнала элемента dd1 будет 10, а на выходе элемента dd2, в соответствии с логикой его работы, появится сигнал

предположить q=0, то комбинация входных сигналов элемента dd2 с учетом выходного сигнала элемента dd1 будет 10, а на выходе элемента dd2, в соответствии с логикой его работы, появится сигнал  = 1. Этот сигнал, поступая на вход элемента dd1, создаст комбинацию входных сигналов 11, в соответствии с которой на выходе этого элемента формируется q= 0. Значение сигнала, поступившего по цепи обратной связи, совпадает с принятым исходным значением. Таким образом, положительная обратная связь обеспечивает сохранение состояния триггера. Подобным образом можно пояснить хранение состояния q= 1.

= 1. Этот сигнал, поступая на вход элемента dd1, создаст комбинацию входных сигналов 11, в соответствии с которой на выходе этого элемента формируется q= 0. Значение сигнала, поступившего по цепи обратной связи, совпадает с принятым исходным значением. Таким образом, положительная обратная связь обеспечивает сохранение состояния триггера. Подобным образом можно пояснить хранение состояния q= 1.

Установочные входы в этом триггере являются инверсными, поэтому в их обозначениях использован знак инверсии. Для установки q = 1 необходимо подать сигнал 0 на вход

.- это установочный вход единицы, а для установки q = 0 - подать 0 на установочный вход нуля

.- это установочный вход единицы, а для установки q = 0 - подать 0 на установочный вход нуля  . и Одновременная подача сигналов установки q = 1 и q = 0 запрещена. Работу триггера описывают таблица истинности и теоретические временные диаграммы (рис. 6.1). Входные сигналы триггера разработаны для иллюстрации определенных режимов работы. На диаграммах отмечены моменты времени: t0 – режим хранения (

. и Одновременная подача сигналов установки q = 1 и q = 0 запрещена. Работу триггера описывают таблица истинности и теоретические временные диаграммы (рис. 6.1). Входные сигналы триггера разработаны для иллюстрации определенных режимов работы. На диаграммах отмечены моменты времени: t0 – режим хранения ( ), t1 – установка 1 (

), t1 – установка 1 ( ), t2 – подтверждение состояния 1 (

), t2 – подтверждение состояния 1 ( ), t3 – установка 0 (

), t3 – установка 0 ( ), t4 – запрещенная комбинация входов (

), t4 – запрещенная комбинация входов ( ), t5 – вновь режим хранения.

), t5 – вновь режим хранения.

module rstrigger (ns, nr,q);

input ns, nr;

output q;

reg q;

always

case ({ns,nr})

2'b00: q=q;

2'b01: q=1'b1;

2'b10: q=1'b0;

2'b11: q=1'bx;

endcase

endmodule

будет полезно при моделировании устройства и оценке экспериментальных данных, которые чаще представляются

будет полезно при моделировании устройства и оценке экспериментальных данных, которые чаще представляются

Признака равенства Е чисел А и В можно получить при помощи комбинационных схем, которые выполняют поразрядную операцию исключающее ИЛИ (сумма по модулю два), и из результатов сравнения отдельных разрядов формируют общий результат. Признак Е равенства четырехразрядных чисел А и В, принимающий значение 1 при равенстве чисел, можно записать в виде:

Признака равенства Е чисел А и В можно получить при помощи комбинационных схем, которые выполняют поразрядную операцию исключающее ИЛИ (сумма по модулю два), и из результатов сравнения отдельных разрядов формируют общий результат. Признак Е равенства четырехразрядных чисел А и В, принимающий значение 1 при равенстве чисел, можно записать в виде: Сумматор – устройство, предназначенное для арифметического суммирования одного разряда кодов двух чисел, при этом производится суммирование трех цифр: первого слагаемого (a), второго слагаемого (b) и переноса из соседнего

Сумматор – устройство, предназначенное для арифметического суммирования одного разряда кодов двух чисел, при этом производится суммирование трех цифр: первого слагаемого (a), второго слагаемого (b) и переноса из соседнего 16. Полусумматор, назначение, принцип работы, синтез (таблица истинности, логические функции, схема, временные диаграммы, описание на языке Verilog) типы, применение.

16. Полусумматор, назначение, принцип работы, синтез (таблица истинности, логические функции, схема, временные диаграммы, описание на языке Verilog) типы, применение.

При использовании двоичного кодирования элементов маски (Рис. 4.4), переход от одного дискретного значения к другому, когда изменяется значение нескольких разрядов, сопровождается ошибками неоднозначности. Изменение состояний отдельных разрядов не может быть одновременным из-за погрешностей изготовления маски.

При использовании двоичного кодирования элементов маски (Рис. 4.4), переход от одного дискретного значения к другому, когда изменяется значение нескольких разрядов, сопровождается ошибками неоднозначности. Изменение состояний отдельных разрядов не может быть одновременным из-за погрешностей изготовления маски.  Для

Для