Практикум по дисциплине Архитектура и организация компьютерных систем Форма обучения очная

Скачать 1.85 Mb. Скачать 1.85 Mb.

|

|

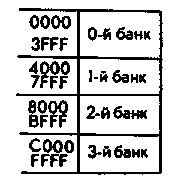

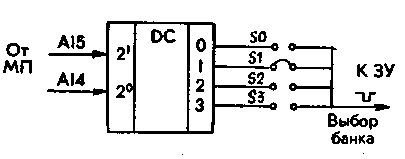

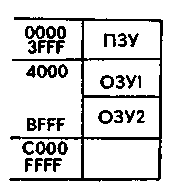

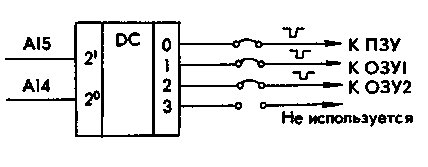

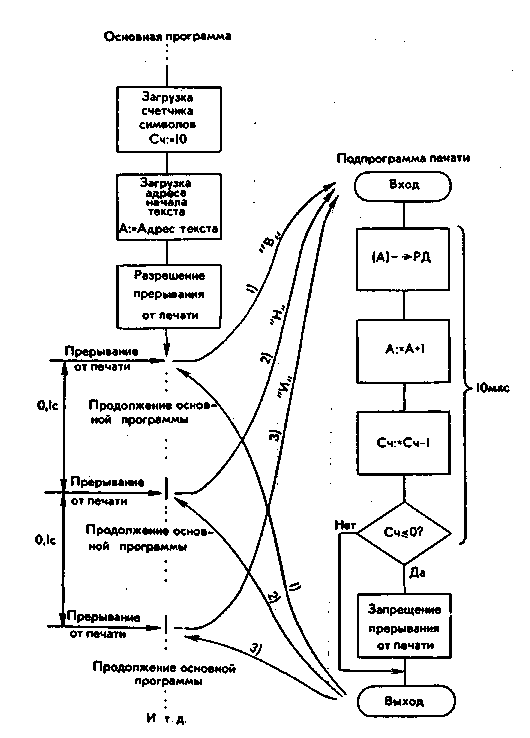

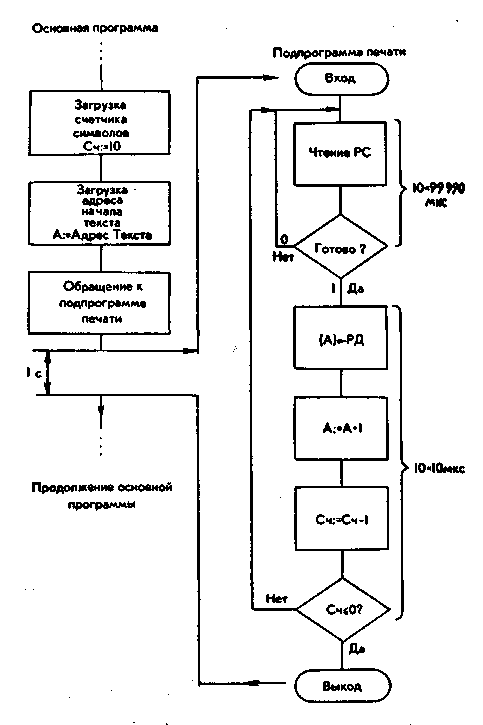

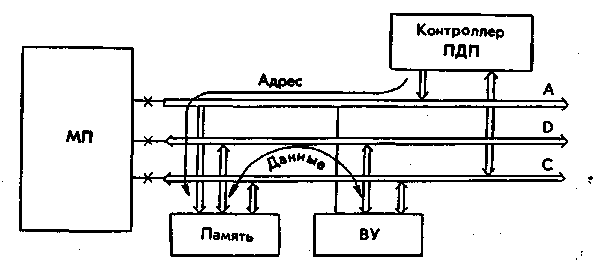

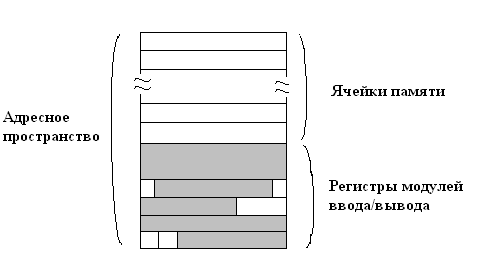

Тема: Организация структуры памяти. Цель: Изучить организацию памяти микропроцессорных устройств. Задание: Ознакомиться с устройствами оперативной памяти. Научиться использовать программный драйвер при эмулировании расширенной памяти как дополнительной. Теоретические сведения Одной из основных функциональных частей микроЭВМ является память — совокупность аппаратных и программных средств, предназначенных для записи, хранения и выдачи информации. Память ЭВМ имеет иерархическую (многоуровневую) структуру. Более низкий уровень иерархии характеризуется меньшим быстродействием и большим объемом. В больших и суперЭВМ число уровней памяти достигнет 5—6. В микроЭВМ принято выделять три уровня: сверхоперативную (СОЗУ), оперативную (ОЗУ) и внешнюю (ВЗУ) память. СОЗУ имеет самые низкие время доступа (дли БИС ТТЛ 50 100 нс) и объем (8— 32 ячейки) и используется для временного хранения команд и данных, как правило, в течение выполнения одной или нескольких операций. Функции сверхоперативной памяти часто выполняют регистры центрального процессора. ОЗУ характеризуется тем, что время поиска ячейки, в которой хранится информация, не зависит от ее адреса (расположения в памяти), а разрядность обычно равна разрядности шины данных и кратна восьми. В ЭВМ адреса ячеек принято нумеровать целыми положительными числами 0, 1,2…N - 1, где N общее число ячеек памяти, связанное с разрядностью r шины адреса формулой N = 2r. Совокупность возможных рапных адресов образует адресное пространство. В каждой конкретной микроЭВМ не обязательно, чтобы нее адресное пространство было заполнено физически подключенной памятью. На рис. 10.1 показана ситуация, когда физическая память занимает четверть адресного пространства (адреса указаны 16-ричной системе счисления). Как видно из рисунка, физическая память может быть расположена в разных четвертях адресного пространства, адреса физической памяти при этом будут различными, а объем один и тот же: 16 К байт. При разбиении адресного пространства на 4, 8, 16 частей говорят о разделении памяти на банки. В зависимости от расположения физический банк памяти имеет свой номер. Чтобы его дешифрировать в адресном пространстве, разделенном на четыре части, два старших разряда А15, А14 адресной шины подают на входы дешифратора DC (рис. 10.2).  Рис. 10.1.  Рис. 10.2. Перемычками S0— S3 задается номер банка, т. е. положение физической памяти 16Кбайт в адресном пространстве 64 К. Перемычка должна быть установлена лишь одна. Для схемы на рис. 19.2 ЗУ 16 Кбайт включено в 1-й банк, следовательно, ему присвоены адреса с 400016 по 7FFF16 включительно. Помимо оперативной памяти, микроЭВМ обычно имеют и постоянную память, в которой хранятся системные программы, тесты, трансляторы, прикладные программы. Информация, записанная в ПЗУ, не подлежит изменению и предназначена только для чтения. Отсюда иногда встречающееся название ПЗУ — ROM (от англ, read only memory — память только для чтения). Для размещения ПЗУ в адресном пространстве микроЭВМ ему необходимо предоставить часть адресного пространства, свободную от ОЗУ. Пересечение адресов ОЗУ и ПЗУ недопустимо. Наиболее просто отвести для ПЗУ один или несколько банков (рис.10.3) при наличии схемы селекции банков (рис. 10.4). Для данного примера распределение адресного пространства памяти таково: нижние 16 Кбайт — ПЗУ, следующие 32 Кбайт — ОЗУ, верхние 16 Кбайт — свободная область. Модульное построение ОЗУ и ПЗУ, возможность быстрого изменения номеров банков позволяют гибко перестраивать структуру адресного пространства памяти микроЭВМ, перераспределяя его между ОЗУ и ПЗУ в зависимости от требований пользователя и конкретной области применения микроЭВМ.  Рис. 10.3.  Рис. 10.4. Применение БИС ЗУ значительно облегчает построение ЗУ по модульному принципу. На рис. 10.5 приведена схема модуля ОЗУ емкостью 4 К байт на микросхемах К537РУ8. Одна из перемычек S0 — S15 должна быть замкнута, этим определяется выбор одного из шестнадцати банков Для замкнутой перемычки, например S1, адреса модуля расположены с 100016 по 1FFF16. Адресная линия А11 выбирает одну из двух микросхем ЗУ. Для адресов 1000-17FF (A11 = 0) выбирается первая БИС ЗУ, а вторая отключена (CS1 = 1). При адресах 1800 -1FFF (А11 = 1) наоборот: первая БИС ЗУ отключена (CS1 = 1), вторая включается при обращении к банку. ВЗУ имеет наибольший объем — десятки и сотни мегабайт и самое большое время поиска, записи и считывания информации. В отличие от СОЗУ, ОЗУ (ПЗУ), называемых иногда внутренней памятью, ВЗУ в основном использует магнитные носители информации и не участвует непосредственно в процессе вычислений. Поскольку ВЗУ часто конструктивно выполняется в виде отдельного устройства, его относят к периферийным устройствам ЭВМ. Задания для самостоятельного выполнения: Проанализировать данные из SysInfo, вкладка Ресурсы аппаратуры- Память. Ответить на контрольные вопросы: Что такое память? Какую структуру имеет память ЭВМ? Три уровня памяти микроЭВМ. Сверхоперативная память. Оперативная памятью Внешняя память. Функции сверхоперативной памяти. Постоянная память. Лабораторная работа №11 (2 часа) Тема: Системы прерываний. Цель: Ознакомиться с аппаратными прерываниями микропроцессора. Задание: Произвести обработку текущего прерывания. Выполнить анализ условия обслуживания прерывания. Теоретические сведения: Для повышения производительности системы необходимо освободить процессор от опроса готовности ВУ к обмену. Эта функция возлагается на контроллер ВУ, Получив команду ввода-вывода, контроллер передает ее ВУ и следит за временем ее выполнения. По окончании действий в ВУ (печати, перфорации и т. и.) контроллер посылает в процессор сигнал требования прерывания, получает очередную команду ввода-вывода, и действия повторяются. Процессор в этом случае, передав в контроллер очередную команду ввода-вывода, может выполнять другие операции основной программы до получения сигнала требования прерывания. Получив его, он обслуживает это прерывание, т. е. формирует и выдает в контроллер очередную команду ввода-вывода, а затем возвращается к выполнению прерванной основной программы.  Рис. 11.1 В программе вывода текста, показанной на рис. 11.2, отсутствует ожидание готовности ВУ. Как только устройство печати готово принять очередной символ, контроллер вырабатывает требование прерывания, и на 10 мкс прерывается основная программа, а затем продолжается ее выполнение. Простои процессора сокращаются, так как пока ВУ не готово, процессор выполняет другие команды основной программы, т. е. процессор и ВУ в это время работают параллельно. Ввод-вывод по прерываниям, однако, требует усложнения аппаратных средств — создания системы прерываний.  Рис. 11.2 Два рассмотренных выше способа обмена — программный и по прерываниям — имеют малую скорость обмена данными. Для передачи одного слова данных процессор должен выполнить несколько команд, среди них вспомогательные — изменение адреса памяти, изменение и анализ содержимого счетчика слов. В некоторых микропроцессорах (например, в МП КР580ВМ80) невозможно в одной команде передать данные из ВУ в память. Сначала необходимо их принять в процессор, а затем из процессора передать в память. Однако во многих случаях требуется передавать большие массивы информации между памятью и внешним устройством (например, накопители на гибких магнитных дисках). В этом случае процессор выступает в роли «лишнего звена», транзитом пропуская через себя информацию. Скорость передачи информации при этом ограничена и не превышает нескольких десятков К байт в секунду. В то же время память микроЭВМ обычно позволяет выполнять чтение-запись данных со скоростью несколько сот Кбайт или даже несколько Мбайт в секунду. Нередко и ВУ позволяют вводить или выводить данные с такими скоростями. Очевидно, что процессор, участвуя в таком обмене, становится «узким местом», снижает возможные скорости обмена, поэтому в режиме прямого доступа к памяти (ПДП) процессор отключается и не участвует в операциях ввода-вывода. Весь обмен информацией выполняется под управлением контроллера ПДП, который «замещает» процессор на это время, т. е. сам формирует адрес памяти, изменяет его и счетчик слов после каждого чтения-записи, принимает решение об окончании обмена и осуществляет синхронизацию. Контроллер ПДП — сложное устройство. В случае необходимости обмена контроллер сообщает об этом процессору сигналом «Запрос на захват шины» или «Требование прямого доступа». Освободив шины, процессор отвечает сигналом «Подтверждение захвата» («Подтверждение прямого доступа»), и с этого момента контроллер ПДП получает шины интерфейса в свое распоряжение. Режим ПДП позволяет достичь максимально возможной скорости обмена, определяемой физическим быстродействием памяти, ВУ, схем интерфейса. Заметим, что программы обмена в этом случае нет, обмен выполняется аппаратно. Данные передаются из памяти в ВУ и из ВУ в память напрямую, как показано на рис. 11.3. Как уже отмечалось, для более эффективной организации ввода-вывода в микроЭВМ существует система прерываний. Под прерыванием понимают переход от выполнения основной программы к другой, называемой программой обработки прерывания, по внешнему запросу на прерывание, причем момент появления запроса заранее не известен. Можно провести аналогию между переходом к программе обработки прерывания и уже известной процедурой обращения к подпрограмме из основной программы. В обоих случаях при выходе из основной программы необходимо запомнить адрес возврата, т. е. адрес команды основной программы, которая будет выполняться после возврата из подпрограммы. Для этого используется стек, куда загружается содержимое программного счетчика (адрес возврата) при переходе к подпрограмме или при прерывании.  Рис. 11.3. Отличие, как уже отмечалось, состоит в том, что момент обращения к подпрограмме заранее «запланирован» в основной программе записью в нужном месте команды обращения к подпрограмме. В системе команд микропроцессора КР580ВМ80 это команда CALL, в системе команд микроЭВМ «Электроника-60» (ДВК, микропроцессоры К1801ВМ1, ВМ2, ВМЗ) — команда ISR. Если микроЭВМ должна обслуживать несколько устройств, способных требовать прерывание, то при появлении запроса необходимо определить источник прерывания и обеспечить переход на соответствующую программу обслуживания, так как каждое устройство обслуживается по-разному. Таким образом, работу системы прерывания можно свести к трем функциям: 1) обнаружение запроса (требования) на прерывание; 2) определение источника прерывания; 3) переход на соответствующую этому источнику программу обслуживания (с запоминанием адреса возврата). Указанные функции в каждой конкретной микроЭВМ реализуются по-разному, при этом используется сочетание аппаратных и программных средств. Контрольные вопросы: Что необходимо выполнить для повышения производительности системы? Опишите процесс ввода-вывода по прерываниям? Что такое контроллер ПДП? Какие функции выполняет контроллер ПДП? Что такое прерывание? Функции системы прерывания. Лабораторная работа №12 (2 часа) Тема: Системы ввода вывода. Цель: Изучить процесс обмена данными между ядром микропроцессорного устройства и периферийными устройствами. Задание: Произвести обработку текущего прерывания. Выполнить анализ условия обслуживания прерывания. Теоретические сведения Помимо центрального процессора (ЦП) и памяти, третьим ключевым элементом архитектуры ВМ является система ввода/вывода (СВВ). Система ввода/вывода призвана обеспечить обмен информацией между ядром ВМ и разнообразными внешними устройствами (ВУ). Технические и программные средства СВВ несут ответственность за физическое и логическое сопряжение ядра вычислительной машины и ВУ. В процессе эволюции вычислительных машин системам ввода/вывода по сравнению с прочими элементами архитектуры уделялось несколько меньшее внимание. Косвенным подтверждением этого можно считать, например, то, что многие программы контроля производительности (бенчмарки) вообще не учитывают влияния операций ввода/вывода (В/ВЫВ) на эффективность ВМ. Следствием подобного отношения стал существенный разрыв в производительности процессора и памяти, с одной стороны, и скоростью ввода/вывода — с другой. Технически система ввода/вывода в рамках ВМ реализуется комплексом модулей ввода/вывода (МВБ). Модуль ввода/вывода выполняет сопряжение ВУ ты ВМ и различные коммуникационные операции между ними. Две основные функции МВВ: обеспечение интерфейса с ЦП и памятью («большой» интерфейс); обеспечение интерфейса с одним или несколькими периферийными устройствами («малый» интерфейс). Анализируя архитектуру известных ВМ, можно выделить три основных способа подключения СВВ к ядру процессора В варианте с раздельными шинами памяти и ввода/вывода обмен•информацией между ЦП и памятью физически отделен от ввода/вывода, поскольку обеспечивается полностью независимыми шинами. Это дает возможность осуществлять обращение к памяти одновременно с выполнением ввода/вывода. Кроме того, данный архитектурный вариант ВМ позволяет специализировать каждую из шин, учесть формат пересылаемых данных, особенности синхронизации на и т. п. В частности, шина ввода/вывода, с учетом характеристик реальных режет иметь меньшую пропускную способность, что позволяет снизить затраты на ее реализацию. Недостатком решения можно считать большое количество точек подключения к ЦП. Второй вариант — с совместно используемыми линиями данных и адреса. Память и СВВ имеют общие для них линии адреса и линии данных, разделяя их во времени. В то же время управление памятью и СВВ, а также синхронизация их взаимодействия с процессором осуществляются независимо по раздельным линиям управления. Это позволяет учесть особенности процедур обращения к памяти и к модулям ввода/вывода и добиться наибольшей эффективности доступа к ячейкам памяти и внешним устройствам. Последний тип архитектуры ВМ предполагает подключение СВВ к системной шине на общих правах с процессором и памятью.Преимущества и недостатки такого подхода обсуждались при рассмотрении вопросов организации. Потенциально возможен также вариант подключения внешних уев к системной шине напрямую, без использования МВБ, но против него можно выдвинуть сразу несколько аргументов. Во-первых, в этом случае ЦП пришлось бы оснащать универсальными схемами для управления любым ВУ. При большом разнообразии внешних устройств, имеющих к тому же различные принципы действия, схемы оказываются чересчур сложными и избыточными. Во-вторых, пересылка данных при вводе, и выводе происходит значительно медленнее, чем при обман ЦП и памятью, и было бы невыгодно задействовать для обмена информация высокоскоростную системную шину. И, наконец, в ВУ часто используете * форматы данных и длина слова, чем в ВМ, к которым они подключены. Как и обращение к памяти, операции ввода/вывода также предполагают наличие некоторой системы адресации, позволяющей выбрать один из модулей СВВ, а также одно из подключенных к нему внешних устройств. Адрес модуля и ВУ является составной частью соответствующей команды, в то время как расположение данных на внешнем устройстве определяется пересылаемой на ВУ информацией. Адресное пространство ввода/вывода может быть совмещено с адресным пространством памяти или быть выделенным. При совмещении адресного пространства для адресации модулей ввода/вывода отводится определенная область адресов (рис. 12.1.). Обычно все операции с модулем ввода/вывода осуществляются с использованием входящих в него внутренних регистров: управления, состояния, данных. Фактически процедура ввода/вывода сводится к записи информации в одни регистры МВВ и считыванию ее из других регистров. Это позволяет рассматривать регистры МВВ как ячейки основной памяти и работать с ними с помощью обычных команд обращения к памяти, при этом в системе команд ВМ вообще могут отсутствовать специальные команды ввода/вывода. Так, модификацию регистров МВБ можно производить непосредственно с помощью арифметических и логических команд. Адреса регистрам МВВ назначаются в области адресного пространства памяти, отведенной под систему ввода/вывода.  Рис. 12.1. Распределение совмещенного адресного пространства Такой подход представляется вполне оправданным, если учесть, что ввод/вывода обычно составляет малую часть всех операций, выполняемых вычислительной машиной, чаще всего не более 1% от общего числа команд в программе. Реализация концепции совмещенного адресного пространства в ВМ с кэш-памятью и виртуальной адресацией сопряжена с определенными проблемами. В частности, усложняется отображение виртуального адреса устройства ввода/вывода на физическое ВУ. Сложности также возникают и с кэшированием регистров МВВ. Сформулируем преимущества и недостатки совмещенного адресного пространства. Достоинства совмещенного адресного пространства: расширение набора команд для обращения к внешним устройствам, что позволяет сократить длину программы и повысить быстродействие; значительное увеличение количества подключаемых внешних устройств; возможность внепроцессорного обмена данными между внешними устройствами, если в системе команд есть команды пересылки между ячейками памяти; возможность обмена информацией не только с аккумулятором, но и с любым •регистром центрального процессора. Недостатки совмещенного адресного пространства: сокращение области адресного пространства памяти; усложнение декодирующих схем адресов в СВВ; трудности распознавания операций передачи информации при вводе/выводе среди других операций. Сложности в чтении и отладке программы, простые команды вызывают выполнение сложных операций ввода/вывода; трудности при построении СВВ на простых модулях ввода/вывода: сигналы управления не смогут координировать сложную процедуру ввода/вывода. Поэтому МВВ часто должны генерировать дополнительные сигналы под управлением программы. Совмещенное адресное пространство используется в вычислительных машинах MIPS и SPARC. В случае выделенного адресного пространства для обращения к модуля ввода/вывода применяются специальные команды и отдельная система адресов. Это позволяет разделить шины для работы с памятью и шины ввода/вывода, что дает возможность совмещать во времени обмен с памятью и ввод/вывод. Кроме того, адресное пространство памяти может быть использовано по прямому назначению в полном объеме. В вычислительных машинах фирмы IBM и микроЭВМ на базе процессоров фирмы Intel система ввода/вывода, как правило, организуется в соответствии с концепцией выделенного адресного пространства. Достоинства выделенного адресного пространства: адрес внешнего устройства в команде ввода/вывода может быть коротким. В большинстве СВВ количество внешних устройств намного меньше количества ячеек памяти. Короткий адрес ВУ подразумевает такие же короткие команды ввода/вывода и простые дешифраторы; программы становятся более наглядными, так как операции ввода/вывода выполняются с помощью специальных команд; разработка СВВ может проводиться отдельно от разработки памяти. Недостатки выделенного адресного пространства: ввод/вывод производится только через аккумулятор центрального процессора. Для передачи информации от ВУ в РОН, если аккумулятор занят, требуется выполнение четырех команд (сохранение содержимого аккумулятора, ввод из ВУ, пересылка из аккумулятора в РОН, восстановление содержимого аккумулятора); перед обработкой содержимого ВУ это содержимое нужно переслать в ЦП. Связь ВМ с внешним миром осуществляется с помощью самых разнообразных внешних устройств. Каждое ВУ подключается к МВВ посредством индивидуальной шины. Интерфейс, по которому организуется такое взаимодействие МВЩ часто называют малым. Индивидуальная шина обеспечивает обмен данными и управляющими сигналами, а также информацией о состоянии участников обмена. Внешнее устройство, подключенное к МВБ, обычно называют периферийным устройством (ПУ). Все множество ПУ можно свести к трем категориям : для общения с пользователем; для общения с ВМ; для связи с удаленными устройствами. Примерами первой группы служат видеотерминалы и принтеры. Ко второй •группе причисляются внешние запоминающие устройства (магнитные и оптические диски, магнитные ленты и т. п.), датчики и исполнительные механизмы. Отметим двойственную роль внешних ЗУ, которые, с одной стороны, представляют собой часть памяти ВМ, а с другой — являются внешними устройствами. Наконец, устройства третьей категории позволяют ВМ обмениваться информацией Вишенными объектами, которые могут относиться к двум первым группам. В роли удаленных объектов могут выступать также другие ВМ. Задания для самостоятельного выполнения Группа делится на две подгруппы. Каждая подгруппа готовит вопросы команде-сопернику. Побеждает та команда, которая даст наибольшее количество правильных ответов. Лабораторная работа №13 (2 часа) |