Шаблон. Пособие ИМПС. Практикум по интегральной и микропроцессорной схемотехнике

Скачать 1.32 Mb. Скачать 1.32 Mb.

|

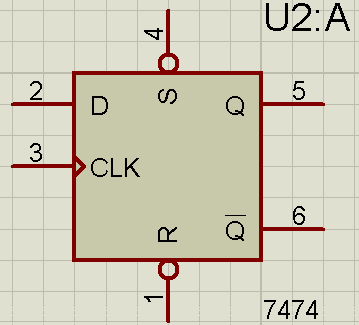

D-ТРИГГЕРRS-триггер, в чистом виде нельзя назвать запоминающим устройством. Входами R и S мы устанавливаем триггер в нужное нам состояние. У него нет как такового информационного входа и нет входа, играющего роль сигнала записи. Если в синхронный RS-триггер дополнить инвертором, сделав входа R и S сделать взаимно-инверсными, то мы получим D–триггер. На рисунке 7.6,а показано получение D-триггера из синхронного RS-триггера и на рисунке 7.6,б УГО D-триггера. Назначение входов D-триггера следующее: D (от англ. – data) – информационный вход;  C (от англ. – clock) – синхронизирующий вход. C (от англ. – clock) – синхронизирующий вход.

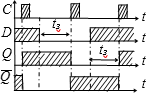

Рисунок 7.6 – УГО D-триггера с синхронизирующим входом Рисунок 7.6 – УГО D-триггера с синхронизирующим входом Рисунок 7.7 – Временная диаграмма работы D-триггера Из анализа временной диаграммы D-триггера (рисунок 7.7) также следует, что выходной сигнал Q триггера повторяет состояние D-входа с поступлением очередного тактового импульса на вход С, с задержкой tзотносительно сменившегося логического состояния на D-входе. D-тригге- ра называют также триггер задержки. D-триггер переключается по закону: Qt+1 = Qt + DC Таблица 7.2 Работа D-триггера

Таблица 7.2 показывает работу D-триггера (для активного перепада по фронту). Основная задача D-триггера состоит в том, что по фронту импульса на входе C сигнал на прямом выходе Q становится таким же, каким был сигнал на входе D в момент этого перехода. Но когда на входе C действует спад импульса или сигнал C остается неизменным, состояние триггера не изменяется, т.е. имеет место режим хранения информации. – означает, что на входе возможно любое состояние (1или 0). Работу в режиме D-триггера называют синхронной. Здесь выходной сигнал триггера изменяется только тогда, когда на входе синхронизации C произошел активный перепад сигнала. В рассматриваемом случае таковым является фронт импульса синхронизации. У интегрального D-триггера (рисунок 7.8) имеется два дополнительных входа – предварительной установки (PreSet) и очистки (CLR). Логический 0 на входе инициирует установку логической единицы на выходе Q (независимо от состояния входов D и C). Логический 0 на входе инициирует очистку выхода Q (установка логического 0 на выходе Q). Необходимо запомнить, что в активных состояниях входы и блокируют действие входов D и С, т.е. для работы с входами D и С, необходимо подать на входы и логическую единицу. Запрещенным состоянием интегрального триггера является одновременное активное состояние входов и т.е. = = 0.   К155ТМ2(7474) Рисунок 7.8 – Интегральный D-триггер | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||