Шаблон. Пособие ИМПС. Практикум по интегральной и микропроцессорной схемотехнике

Скачать 1.32 Mb. Скачать 1.32 Mb.

|

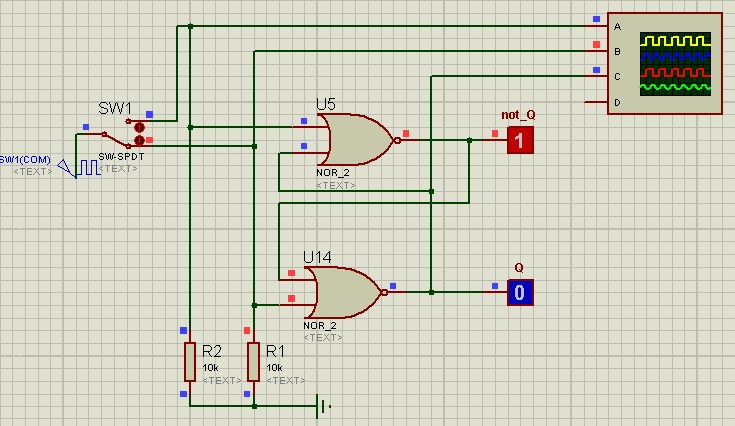

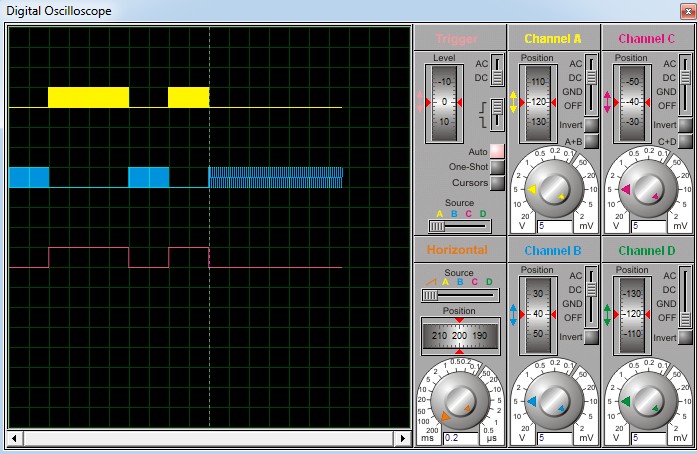

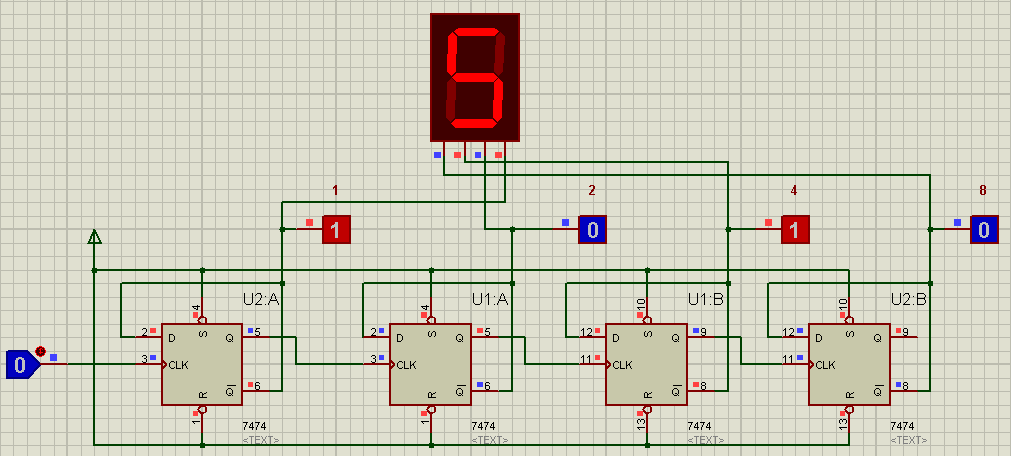

Содержание лабораторной работы Задание:Реализовать схему для испытания асинхронного RS-триггера с активным высоким и низким уровнем. Начертить временные диаграммы для данных устройств. Реализовать устройство защиты от дребезга контактов на элементах: ИЛИ-НЕ, И-НЕ (рисунок 7.12).  Рисунок 7.12 – Схема реализации защиты от дребезга контактов на RS- триггере, выполненная на элементах ИЛИ-НЕ. Параметры осциллографа приведены на рисунке 7.13, генератора на рисунке 7.14. Реализовать схему для испытания синхронного RS-триггера с активным высоким и низким уровнем. Начертить временные диаграммы для данных устройств.  Рисунок 7.13 – Параметры осциллографа и выходные эпюры напряжения Реализовать схему для испытания синхронного RS-триггера с активным высоким и низким уровнем (по варианту). Начертить временные диаграммы для данных устройств.  Рисунок 7.14 – Параметры генератора Реализовать схему для испытания D-триггера в интегральном исполнении и на элементах ИЛИ-НЕ или И-НЕ (по варианту). Начертить временные диаграммы для данных устройств. Реализовать схему для испытания Т-триггера. Начертить временные диаграммы для данных устройств. Реализовать схему для испытания JK-триггера в интегральном исполнении. Начертить временные диаграммы для данных устройств. Реализовать на JK-триггере схемы Т-триггера, Т-триггера со входом разрешения, D-триггера (по варианту). Контрольные вопросыКакие устройства называются последовательностными? В чем заключается отличие асинхронных триггеров от синхронных? Какие основные виды триггеров вам известны? Опишите работу RS-триггера, D-триггера? Почему Т-триггер называют счетным триггером? Преобразуйте JK-триггер в D- и Т-триггеры? Лабораторная работа № 8. ИССЛЕДОВАНИЕ РАБОТЫ СЧЕТЧИКОВЦель работы: Понять принцип работы счетчиков. Изучить асинхронные и синхронные счетчики. Краткие сведения из теорииСчетчик – это устройство, на выходе которого сигналы в определенном коде отображают число импульсов, поступивших на счетный вход. Счетчики строятся на базе триггеров. Счетчик, образованный цепочкой из n последовательно соединенных триггеров, может подсчитать в двоичном коде 2nимпульсов. Число Ксч 2n называется коэффициентом счета, число n определяет количество разрядов двоичного числа. Информация снимается с прямых и (или) инверсных выходов всех триггеров. В паузах между входными импульсами триггеры сохраняют свои состояния, т.е. счетчик запоминает число входных импульсов. Нулевое состояние всех триггеров принимается за нулевое состояние счетчика в целом. Остальные состояние нумеруются по числу поступивших входных импульсов. Когда число входных импульсов Nвх Kсч, происходит переполнение, после чего счетчик возвращается в нулевое состояние и цикл повторяется. Коэффициент счета, таким образом, характеризует число входных импульсов, необходимое для выполнения одного цикла и возвращения в исходное состояние. Число входных импульсов и состояние счетчика взаимно определены только для первого цикла. После окончания каждого цикла на выходах последнего триггера возникают перепады напряжения. Это определяет второе назначение: деление числа входных импульсов. Если входные сигналы периодичны и  следуют с частотой следуют с частотойFвх, то частота выходных сигналов равна Fвых Fвх Ксч. В этом случае коэффициент счета называется коэффициентом деления и обозначается как Кдел. Счетчики характеризуются емкостью и быстродействием. Емкость счетчика численно равна коэффициенту счета и определяет число импульсов, доступное счету за один цикл. Быстродействие счетчика определяется разрешающей способностью tраз.сч и временем установки кода счетчика tуст. Разрешающая  способность - это минимальное время между двумя входными сигналами. способность - это минимальное время между двумя входными сигналами.Величина fmax 1 tраз.сч называется максимальной частотой счета. Время установки кода равно времени между моментом поступления входного сигнала и переходом счетчика в новое устойчивое состояние. Введением дополнительных логических связей – обратных и прямых – двоичные счетчики преобразуются в недвоичные. Наибольшее распространение получили десятичные (декадные) счетчики, работающие с Ксч 10 в двоично-десятичном коде (двоичный – по коду счета, десятичная – по числу состояния). Счетчики на схемах обозначаются буквами СТ (от англ. counter – счетчик), после символа проставляют число, характеризующее модуль счета (например, 4 или 10 – СТ4, СТ10). Рассмотримосновныеклассификациисчетчиков. Если при каждом импульсе код нарастает, то счетчик называется суммирующим, если уменьшается, то вычитающим. Реверсивный счетчик может работать в качестве суммирующего и вычитающего. Счетчики бывают кольцевыми и тупиковыми. Счетчик кольцевой суммирующий, имеющий коэффициент счета, равный 10 будет прибавлять к каждому предыдущему значению кода единицу, по достижении 9, значение кода переходит в 0. Переход из «9» в «0» называется переполнением. Счетчик кольцевой вычитающий имеющий коэффициент счета равный 10 будет отнимать от каждого предыдущего значения кода единицу, по достижении 0, значение кода переходит в 9. Переход от «0» в «9» называется переопустошением. У тупиковых счетчиков нет переполнения и переопустошения, при достижения максимума (минимума). Например, для тупикового суммирующего счетчика с коэффициентом счета равным 10, выходной сигнал будет: 0, 1, 2,…8, 9, 9, 9… Счетчики могут быть асинхронными и синхронными. Они строятся на D- и Т-триггерах.  Рисунок 8.1 – Четырехразрядный асинхронный счетчик Асинхронные счетчики представляют собой цепочку триггеров, в которой триггеров, в которой импульсы, подлежащие счету, поступают на вход первого триггера, а сигнал переноса передается последовательно от одного разряда к другому. Главное достоинство таких счетчиков – простота схемы. Увеличение разрядности осуществляется подключением дополнительных триггеров к выходу последнего триггера. Основной недостаток асинхронных триггеров – сравнительно низкое быстродействие, поскольку триггеры срабатывают последовательно, один за другим, т.е. происходит суммирование задержек каждого триггера. Из этого следует, что чем выше разрядность, тем ниже быстродействие счетчика. Рассмотрим работу четырехразрядного асинхронного счетчика. Его принципиальная схема представлена на рисунке 8.1. На вход счетчика подаются прямоугольные импульсы. Индикаторы LOGICPROBE программы PROTEUS ISIS 7 соответствуют каждому разряду счетчика, 20 – самый младший разряд, 23 – самый старший. Таким образом, индикаторы показывают бинарный код счетчика для каждого такта. Семисегментный индикатор отображает шестнадцатеричный код. При использовании прямых выходов получается счетчик вычитающий, при использовании инверсных выходов – получается суммирующий (для схемы на рисунке 8.1). В ППП PROTEUS ISIS 7 существует достаточное количество библиотечных счетчиков, один из них – асинхронный счетчик 7493, его отечественный аналог К155ИЕ5 (схема на рисунке 8.2).  Рисунок 8.2 – Схема исследования счётчика К155ИЕ5(7493) Выводы QA, QB, QC, QD являются выходами счетчика. Вывод QD соответствует самому старшему разряду, а QA – самому младшему. Счетчик 7493 структурно состоит из двух независимых счётчиков: Делитель на 2, вход – СКА и выход QA; Делитель на 8, вход – СКВ и выход QB, QC и QD. Переключение счётчика происходит по спаду сигнала на входах СКА, СКВ. В случае использования микросхемы 7493 как счётчик-делитель на 16, необходимо соединить выход первого счётчика QA со входом второго СКВ. Сброс счетчика осуществляется подачей уровня высокого напряжения на входа R0(1) и R0(2), объединённые логикой И. На рисунке 8.3 представлена схема реверсивного счётчика 74193, его отечественный аналог К155ИЕ7. Для предварительной записи в счетчик данных используются входы D0, D1, D2, D3. Разрешением на запись будет подача на вход параллельной загрузки напряжения низкого уровня. Выводы Q0, Q1, Q2, Q3 являются выходами счетчика. Вывод Q3 соответствует самому старшему разряду, а Q0 – самому младшему. Сброс всех триггеров счетчика осуществляется подачей уровня высокого напряжения на вход MR. Счётчик имеет раздельные импульсные входа положительной полярности UP – для счёта на увеличение и DN - для счёта на уменьшение. Выход , сигналом Лог. 0 сигнализирует о переполнении и может быть подан на вход UP последующего счетчика. Выход , сигналом Лог. 0 сигнализирует о заёме при вычитании и может быть подан на вход DN последующего счетчика.  Рисунок 8.3 – Схема исследования счётчика К155ИЕ5(74193) |