Шаблон. Пособие ИМПС. Практикум по интегральной и микропроцессорной схемотехнике

Скачать 1.32 Mb. Скачать 1.32 Mb.

|

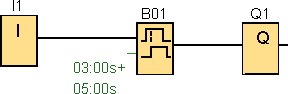

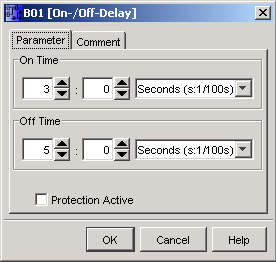

Задержка включения и выключения (ON - /OFF – Delay) Краткое описаниеПри задержке включения и выключения выход включается через запрограммированное время и сбрасывается по истечении параметризуемого периода времени.

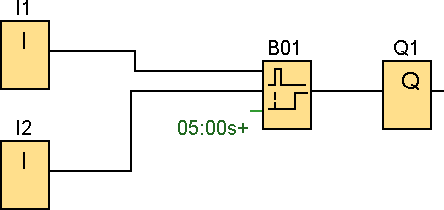

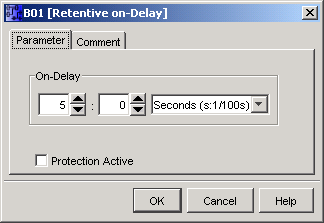

Рисунок 12.3 – Задержка включения и выключения Задание:Ввести программу, представленную на рисунке 12.3; Установить временные параметры переключения; Подать сигнал высокого уровня (ЛОГ. 1) на вход I1; Через параметризуемое время наблюдать появление высокого уровня (ЛОГ. 1) на выходе Q1. При переводе сигнала на входе I1 с высокого уровня (ЛОГ. 1) на низкий (ЛОГ. 0), через параметризуемое время наблюдать появление низкого уровня (ЛОГ. 0) на выходе Q1; Убедиться, что сигнал на выходе Q1 изменяется с 0 на 1 через время ТH только при наличии сигнала запуска на входе I1 в течении времени большее чем ТH. Задержка выключения, когда сигнал на выходе Q1 изменяется с 1 на 0 через время ТL, происходит только если состояние сигнала на входе I1 остается равным 0 по крайней мере в течение параметризованного интервала времени TL; Зарисовать временные диаграммы работы блока. Задержка включения с запоминанием (Retentive ON – Delay) Краткое описаниеВслед за входным импульсом начинается определяемый период времени, по истечении которого выход устанавливается.

Рисунок 12.4 – Задержка включения с запоминанием Задание:Ввести программу, представленную на рисунке 12.4; Установить временные параметры переключения; Подать сигнал высокого уровня (ЛОГ. 1) на вход I1; Через параметризуемое время наблюдать появление высокого уровня (ЛОГ. 1) на выходе Q1.; Убедиться, что сигнал на выходе Q1 изменяется с 0 на 1 через время Ta независимо от повторного перезапуска на входе Trg или переводе сигнала на входе I1 с высокого уровня (ЛОГ. 1) на низкий (ЛОГ. 0). Выход Q1 и время Ta сбрасываются в 0, только при переводе сигнала на входе I2 с низкого (ЛОГ. 0) на высокий уровень (ЛОГ. 1); Зарисовать временные диаграммы работы блока. |