Шаблон. Пособие ИМПС. Практикум по интегральной и микропроцессорной схемотехнике

Скачать 1.32 Mb. Скачать 1.32 Mb.

|

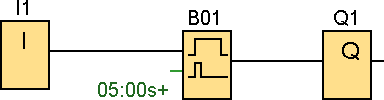

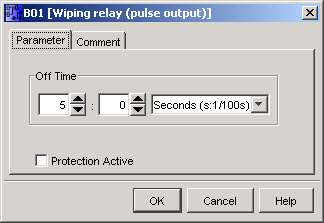

Интервальное реле времени – импульсный выход (Wiping relay[pulse output])Краткое описание Входной сигнал взывает появление сигнала заданной длительности на выходе.

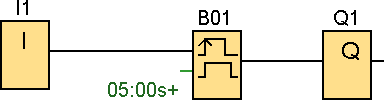

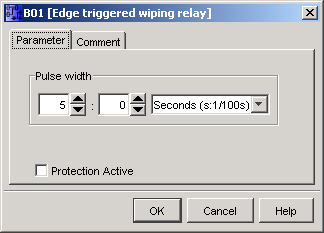

Рисунок 12.5 – Интервальное реле времени – импульсный выход Задание:Ввести программу, представленную на рисунке 12.5; Установить временные параметры переключения; Подать сигнал высокого уровня (ЛОГ. 1) на вход I1; Наблюдать немедленное появление высокого уровня (ЛОГ. 1) на выходе Q1. Через параметризуемое время выход Q1 переключится с высокого уровня (ЛОГ. 1) на низкий (ЛОГ. 0), формируя таким образом импульс, длительностью Та; Убедиться, что при изменении состояние сигнала на входе Trg с 1 на 0 до истечения заданного времени, выход тоже немедленно переключается обратно с 1 на 0; Зарисовать временные диаграммы работы блока. Интервальное реле времени, запускаемое фронтом (Edge triggered wiping relay)Краткое описание Входной сигнал взывает появление сигнала параметризуемой длительности на выходе (с повторным запуском).

Рисунок 12.6 – Интервальное реле времени, запускаемое фронтом Ввести программу, представленную на рисунке 12.6; Установить временные параметры переключения; Подать сигнал высокого уровня (ЛОГ. 1) на вход I1; Наблюдать немедленное появление высокого уровня (ЛОГ. 1) на выходе Q1. Через параметризуемое время выход Q1 переключится с высокого уровня (ЛОГ. 1) на низкий (ЛОГ. 0), формируя таким образом импульс, длительностью Та; Убедиться, что при изменении состояние сигнала на входе Trg с 1 на 0 до истечения заданного времени (перезапуск), время Ta сбрасывается, а выход остается включенным. Зарисовать временные диаграммы работы блока. |