Преобразователи кодов

Скачать 0.72 Mb. Скачать 0.72 Mb.

|

|

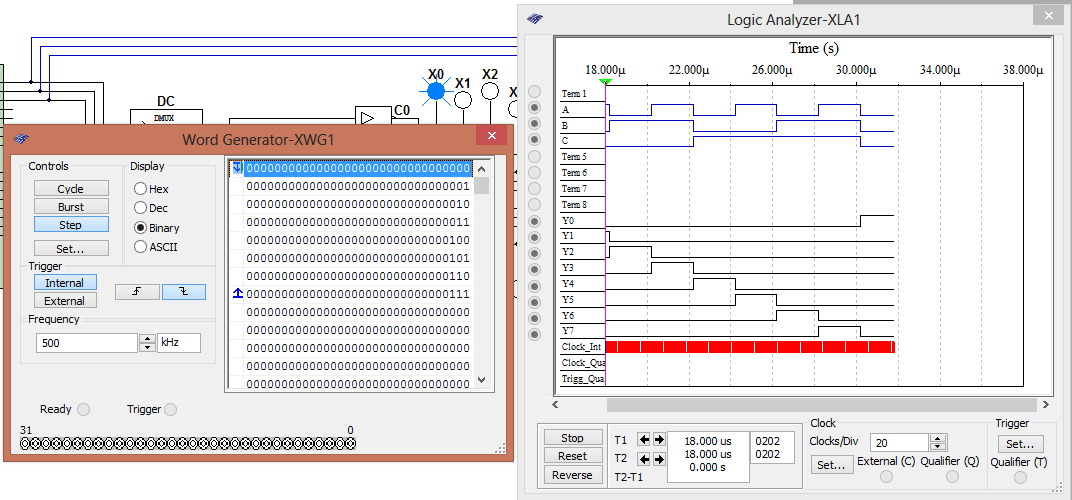

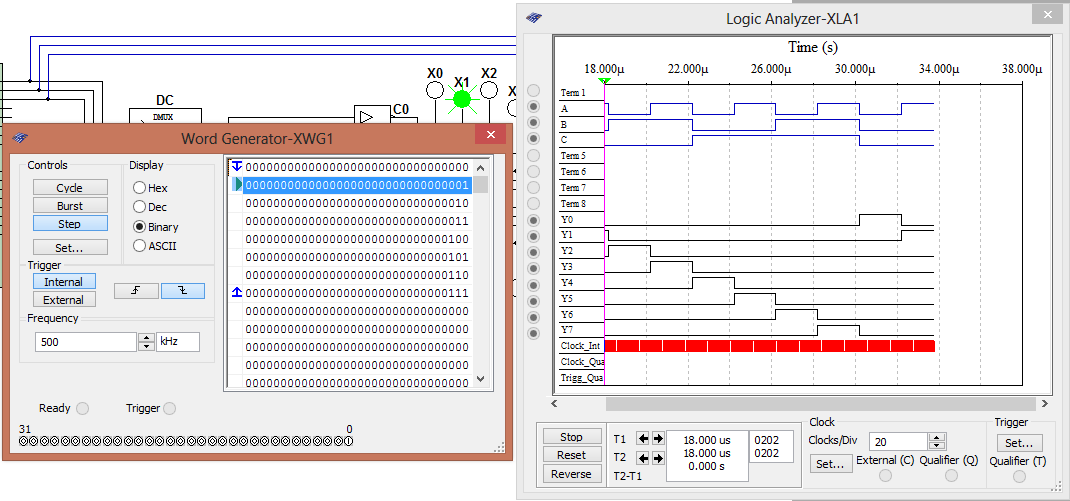

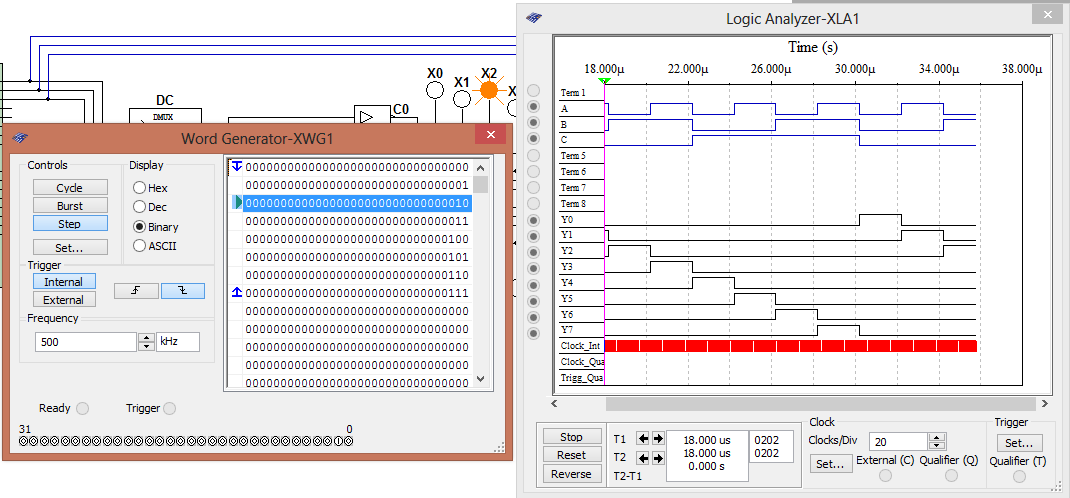

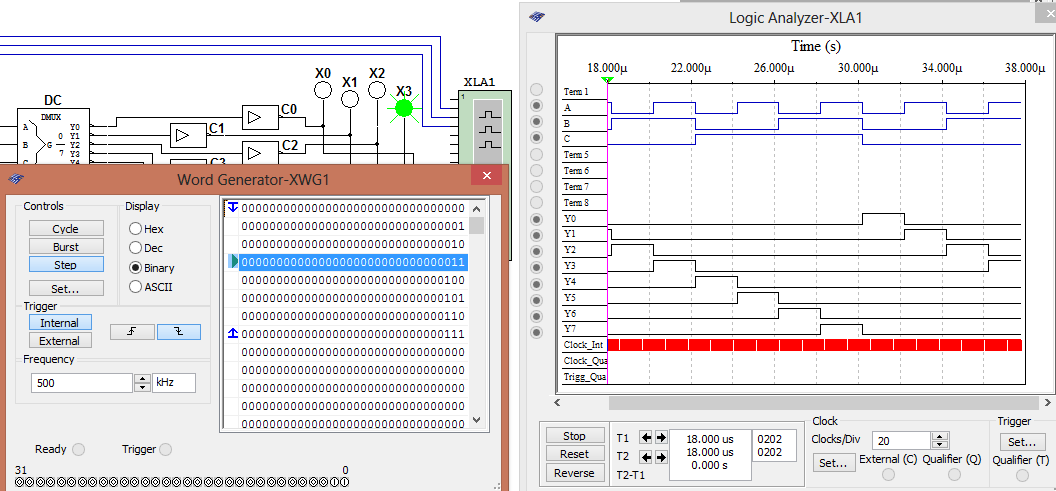

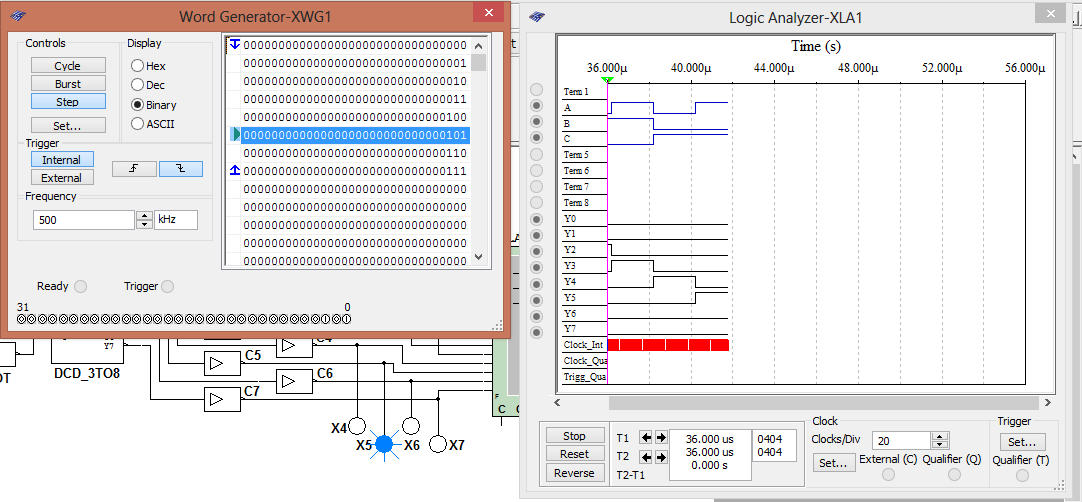

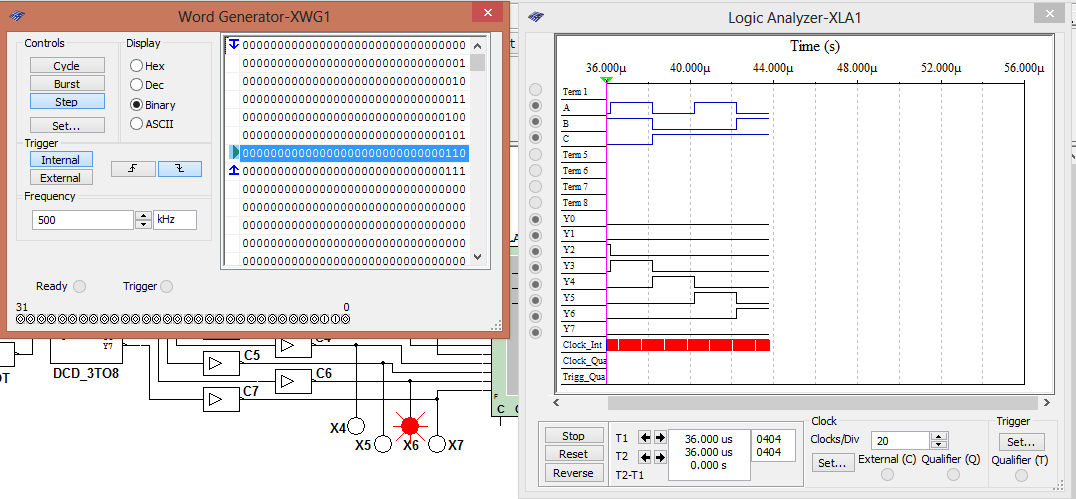

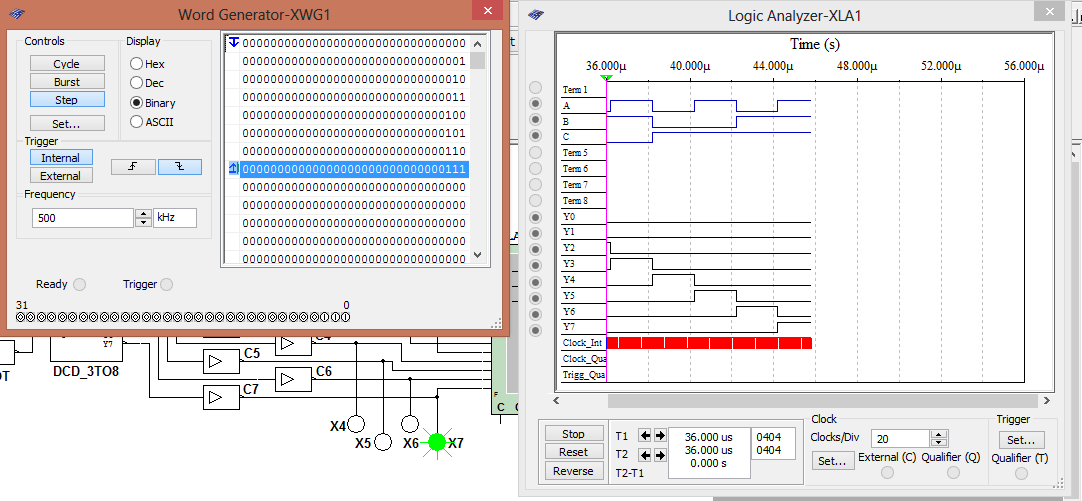

Министерство образования и науки Республики Казахстан Карагандинский государственный технический университет Кафедра ИВС Лабораторная работа №2 по дисциплине: “Схемотехника” Тема: “ Преобразователи кодов” Выполнил: студент гр. ИС-16-1п Сейткалиев Д.Ө. Принял: ст.преп. Триков В.В Караганда 2017 Цель работы: Ознакомление с основными характеристиками и испытание интегральных преобразователей кодов (дешифратора, шифратора, демультиплексора и мультиплексора). Учебные задания и методические указания к их выполнению: Задание 1. Запустить лабораторный комплекс Labworks и среду МS10 (щёлкнув мышью на команде Эксперимент меню комплекса Labworks). Открыть файл 30.6.ms10, размещённый в папке Circuit Design Suite 10.0 среды МS10, или собрать на рабочем поле среды MS10 схему для испытания дешифратора DC (рис. 30.6) и установить в диалоговых окнах компонентов их параметры или режимы работы. Скопировать схему (рис. 30.6) на страницу отчёта. С  хема (рис. 30.6) содержит: • интегральный дешифратор DC (decoder) 3х8, имеющий 3 информационных входа A, B и C (для кода 421), 8 выходов (Y0, …, Y7) и преобразующий позиционный 3-разрядный двоичный код в унитарный "1 из 8": в выходной 8-разрядной кодовой комбинации только одна позиция занята единицей, а все остальные – нулевые (см. рис. 30.7, справа). В зависимости от входного двоичного кода, например 001, на выходе DС появляется сигнал 1 только на одной (второй, см, рис. 30.6) из 8-ми выходных линий, к которым подключены пробники Х0, …, Х7. Данный тип шифратора относится к шифраторам с разным уровнем входных и выходных сигналов: активные входные уровни соответствуют уровню логической 1, а активные выходные сигналы – уровню логического 0. Для получения активных выходных уровней, равных 1, к выходам дешифратора подключено восемь инверторов С0, …, С7; • логический генератор слова XWG1 (fг = 500 кГц) с записанными логическими словами в его ячейки памяти, которые эквивалентны десятичным числам от 0 до 7 (см. рис. 30.7, слева); • логический анализатор XLA1, на экран которого выводятся временные диаграммы как трёх входных (А, В, С), так и восьми (Y0, Y1, …, Y7) выходных сигналов при пошаговом режиме Step генератора XWG1; • источник VCC, напряжение 5 В с выхода которого подано на инвертор NOT. Логический 0 с инвертора подается на управляющий вход дешифратора DC: при  дешифратор находится в активном состоянии. дешифратор находится в активном состоянии.З  апустить программу моделирования дешифратора. Щёлкая мышью на кнопке Step генератора XWG1, последовательно подавать на вход дешифратора логические слова. Убедиться, что при подаче на вход дешифратора каждой новой двоичной кодовой комбинации засвечивается только один пробник, который "распознаёт" свой входной код. Скопировать временные диаграммы входных и выходных сигналов дешифратора на страницу отчёта. По результатам моделирования составить и заполнить таблицу переключений (функций  на выходах дешифратора DC 3х8. на выходах дешифратора DC 3х8.         Таблица истинности дешифратора 3x8:

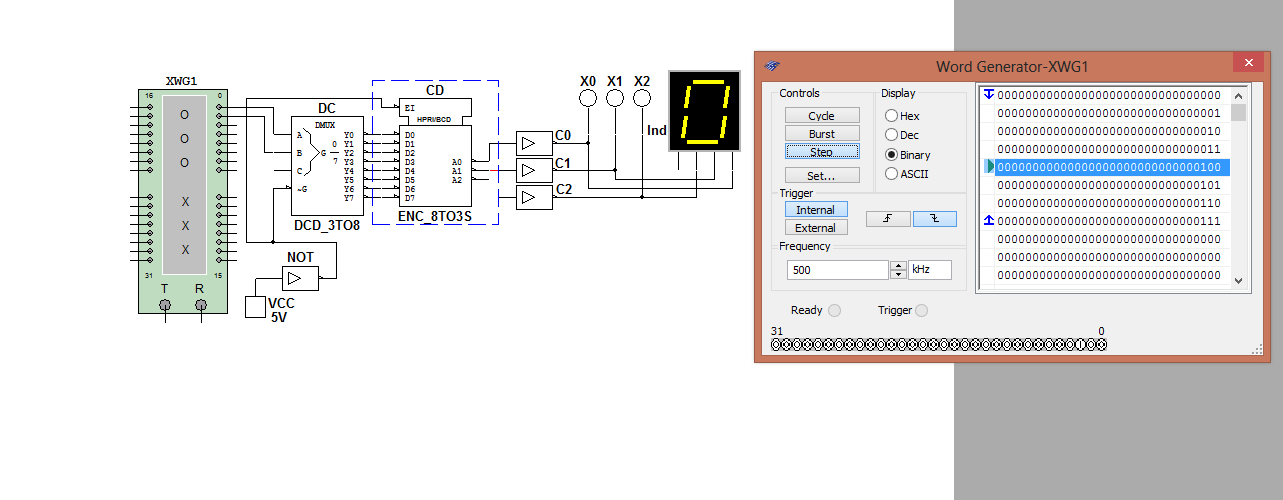

Задание 2. Открыть файл 30.8.ms10, размещённый в папке Circuit Design Suite 10.0 среды МS10, или собрать на рабочем поле среды MS10 схему для испытания шифратора СD (рис. 30.8) и установить в диалоговых окнах компонентов их параметры или режимы работы.  Скопировать схему (рис. 30.8) на страницу отчёт Скопировать схему (рис. 30.8) на страницу отчётИнтегральный шифратор CD 8х3 (из 8 в 3) имеет 8 входов D0, D1, …, D7, подключенных к выходам Y0, Y1, …, Y7 дешифратора DC, и три инверсных выхода А0, А1, А2, к которым через инверторы С0, С1, С2 подключены логические пробники Х0, Х1, Х2 и семисегментный индикатор Ind. Содержимое ячеек памяти генератора слова XWG1: 000, 001, …, 111 (см. рис. 30.7, слева). Запустить программу моделирования шифратора. Щёлкая мышью на кнопке Step генератора XWG1, последовательно подавать на вход дешифратора логические слова. Убедиться, что при подаче с выхода DC на вход шифратора СD 8-разрядной последовательности, в которой только одна позиция занята единицей, а остальные нулями, на выходе шифратора формируются 3-разрядные двоичные коды A0A1A2, где А0 = А, А1 = В и А2 = С, соответствующие двоичным кодовым комбинациям на входе дешифратора DC. По результатам моделирования (по засвечиванию логических пробников Х0, Х1, Х2 и показаниям индикатора Ind) составить и заполнить таблицу переключений на выходе шифратора CD 8х3. Преобразовать схему дешифратора DC 3х8 и шифратора CD 8х3 (см. рис. 30.8) в схему DC 2х4 и шифратора CD 4х2, отсоединив провод С, подходящий к дешифратору, и провод A2 с выхода шифратора, и составить таблицы переключений дешифратора 2х4 и шифратора 4х2. Таблица истинности шифратора 8x3:

Таблица истинности шифратора 4x2:

Таблица истинности дешифратора 2x4:

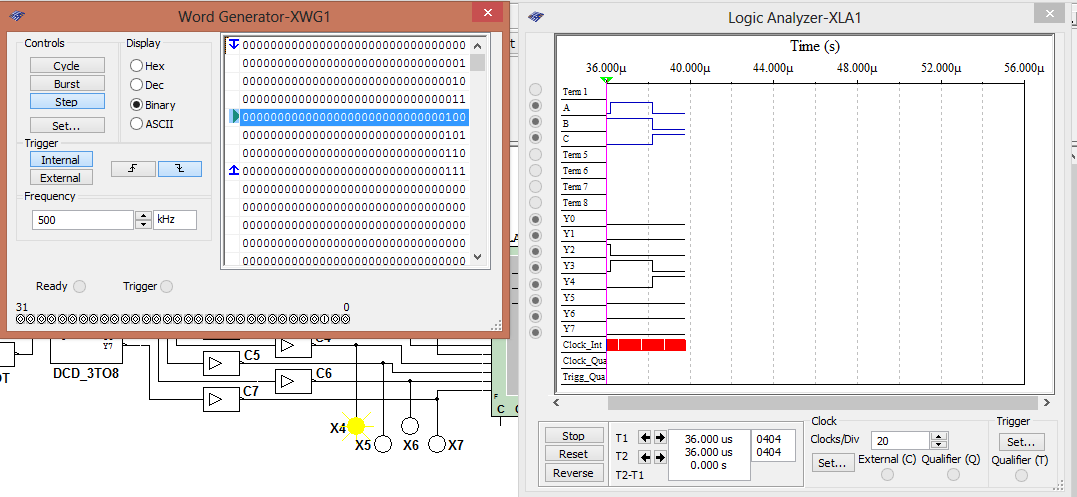

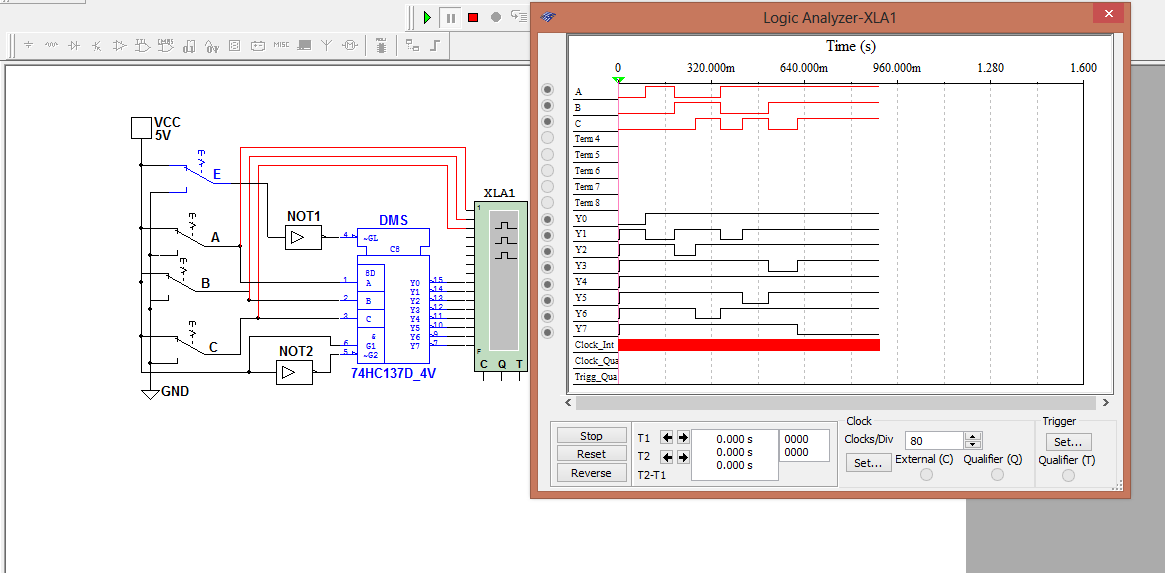

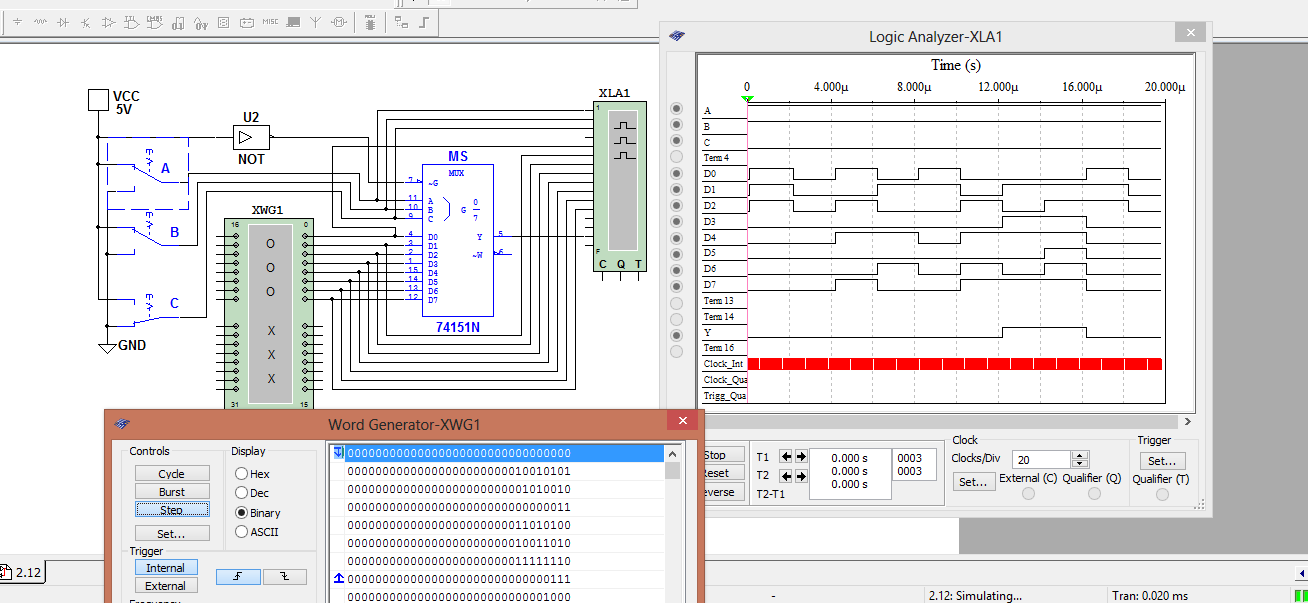

З  адание 3. Открыть файл 30.9.ms10, размещённый в папке Circuit Design Suite 10.0 среды МS10, или собрать на рабочем поле среды MS10 схему для испытания демультиплексора DMS (рис. 30.9) и установить в диалоговых окнах компонентов их параметры или режимы работы. Демультиплексор DMS 1х8 (из 1 в 8) (рис. 30.9) имеет один информационный вход (с активными высоким G1 и низким G2 уровнями), три адресных А, В, С входа, разрешающий GL вход с активным низким уровнем и восемь Y0, Y1, …, Y7 инверсных выходов, соединённых с входами логического анализатора XLA1. На вход анализатора также подаются сигналы с адресных входов А, В, С. С помощью ключей А, В и С можно сформировать восемь трёхразрядных двоичных адресных слов. При последовательной подаче формируемых ключами адресных слов от 111 до 000 на экран анализатора XLA1 при моделировании выводятся 8-разрядные кодовые последовательности с одним активным (низким) уровнем. Для обеспечения медленного перемещения лучей на экране анализатора XLA1 установить частоту его таймера fa = 500 Гц и число импульсов, приходящихся на одно деление, Clocs/div = 80. Задать код ключей 111 и щелкнуть мышью на кнопке Run/Stop. Кривые адресных и выходных логических сигналов медленно разворачиваются во времени на экране анализатора. Остановить (щелчком мыши на кнопке Stop) процесс моделирования при приближении лучей анализатора к линии разметки экрана. Повторять перечисленные выше операции для спадающих счётных комбинаций адресных сигналов (с 110 до 000) до тех пор, пока не будет записан процесс моделирования при адресном слове 000 (см. рис. 30.9, справа). Убедиться, что для каждой комбинации адресных сигналов демультиплексор формирует логический 0 на одном из восьми выходов, номер которого соответствует определенному кодовому слову на входе, т. е. демультиплексор подобен коммутатору, посредством которого поток цифровой информации разделяется на 8 выходных потоков. Скопировать схему (рис. 30.9) и временные диаграммы входных и выходных сигналов на страницу отчёта. Если адресные входы А, В и С принять в качестве информационных входов, а вход G1 (G2) в качестве входа разрешения работы, то мультиплексор превратится в дешифратор.  Задание 5. Открыть файл 30.12.ms10, размещённый в папке Circuit Design Suite 10.0 среды МS10, или собрать на рабочем поле среды MS10 схему (рис. 30.12) для испытания мультиплексора MS 8х1 (из 8 в 1) и установить в диалоговых окнах компонентов их параметры или режимы р  аботы. Скопировать схему (рис. 30.12) на страницу отчёта. Мультиплексор МS с разрешающим входом G осуществляет передачу сигнала с каждого информационного входа D0, D1, …, D7, заданного 3-разрядным кодом АВС – адресом выбираемого входа, на единственный выход Y. Разрядность (3) управляющего сигнала определяет количество входов (23 = 8), с которых мультиплексор может принимать информацию. Если предположить, что к входам D0, D1, …, D7 мультиплексора MS присоединено 8 источников цифровых сигналов – генераторов последовательных двоичных слов, то байты от любого из них можно передавать на выход Y. Для иллюстрации работы мультиплексора MS запишем в ячейки памяти генератора XWG1 произвольные 8-разрядные кодовые слова (рис. 30.13, слева), а с помощью ключей А, В, С сформируем управляющий сигнал 111. Последовательно щёлкая мышью на кнопке Step генератора XWG1 и при G = 1, поступающие на вход D7 мультиплексора байты (сигнал 01001110) с 8-го разряда (на рис. 30.13, слева 8-й разряд показан стрелкой) логических слов генератора XWG1 передаются на выход Y и на вход анализатора (см. рис. 30.13, справа). Если ключ А установить в нижнее положение (сформировав, тем самым, адресный код 011), то с входа D3 на выход Y мультиплексора будут поступать байты 4-го разряда логических слов, записанных в ячейки памяти генератора XWG1, и т. д. З  аписать в первые восемь ячеек памяти генератора XWG1 произвольные 8-разрядные кодовые слова, задать частоту fг = 500 кГц и режим Step его работы (см. рис. 30.13, слева). Задать частоту fa = 20 МГц таймера логического анализатора XLA1 и количество импульсов таймера Clock/div = 20, приходящихся на одно деление. Установить с помощью ключей А, В и С адресный код (самостоятельно или по указанию преподавателя), например 1002 (410) и запустить программу моделирования мультиплексора. Получить и скопировать временные диаграммы входных сигналов D0, D1, …, D7 и выходного сигнала Y мультиплексора на страницу отчёта. Исходный адресный код: 001  Вывод: Ознакомился с основными характеристиками и испытал интегральные преобразователи кодов (дешифратора, шифратора, демультиплексора и мультиплексора).ТЕСТОВЫЕ ЗАДАНИЯ К РАБОТЕ:1. Укажите задачи: а) Для демультиплексирования данных и адресной логики в запоминающих устройствах, а также для преобразования двоично-десятичного кода в десятичный с целью управления индикаторными и печатающими устройствами; б) Для преобразования десятичных чисел в двоичные или в двоично-десятичный код, например, в микрокалькуляторах, в которых нажатие десятичных клавишей вызывает генерацию соответствующих двоичных кодов; в) Для хранения и преобразования многоразрядных двоичных чисел; г) Для коммутации в заданном порядке сигналов, поступающих с нескольких входных шин на одну выходную; д) Для распределения в требуемой последовательности по нескольким выходам сигналов с одного информационного входа, в частности, для передачи информации по одной линии от нескольких установленных на ней датчиков, при решении которых используется:      1. Шифратор: а) б в) г) д) 1. Шифратор: а) б в) г) д)      2. Дешифратор: а) б) в) г) д) 2. Дешифратор: а) б) в) г) д)      3. Мультиплексор: а) б) в) г) д) 3. Мультиплексор: а) б) в) г) д) 4      . Демультиплексор: а) б) в) г) д) . Демультиплексор: а) б) в) г) д) 2. Укажите, с какого разряда бинарного слова генератора логического слова XWG будет передаваться информация на выход мультиплексора 8х3 при адресном коде 100 на его входе?      1 3 5 7 9 1 3 5 7 9 3. Укажите число выводов дешифратора при трёх информационных входах.      2 4 6 8 16 2 4 6 8 16 4. Укажите назначение стробирующих входов в преобразователях кодов.  Для синхронизации работы преобразователей Для синхронизации работы преобразователей Для увеличения числа коммутируемых информационных входов, а также для блокирования работы преобразователей Для увеличения числа коммутируемых информационных входов, а также для блокирования работы преобразователей Д  ля увеличения числа адресных входов ля увеличения числа адресных входов5. Укажите, в каком преобразователе выбор входа по его номеру (адресу) осуществляется с помощью двоичного кода?    В шифраторе В дешифраторе В мультиплексоре В шифраторе В дешифраторе В мультиплексоре  В демультиплексоре В демультиплексоре6. Укажите число выводов у шифратора при четырёх информационных входах.      16 8 4 2 1 16 8 4 2 1 7. Укажите, какой из приведенных преобразователей кодов выпускается промышленностью только в составе других устройств?     Шифратор Дешифратор Демультиплексор Мультиплексор Шифратор Дешифратор Демультиплексор Мультиплексор |