Шинная организация микропроцессорных систем- с одной шиной, с дв. Программа для эвм это упорядоченная последовательность команд, подлежащая обработке

Скачать 1.97 Mb. Скачать 1.97 Mb.

|

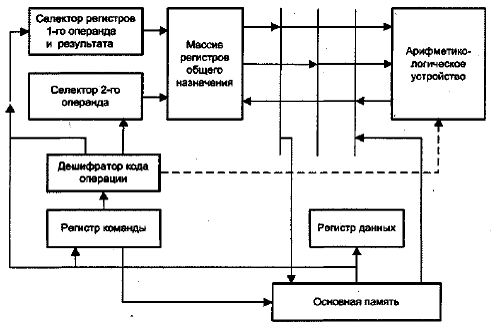

34. Архитектура микропроцессоров с выделенным доступом к памяти.В архитектуре с выделенным доступом к памяти обращение к основной памяти возможно только с помощью двух специальных команд: load и store. В английской транскрипции данную архитектуру называют Load/Storearchitecture. Команда load(загрузка) обеспечивает считывание значения из основной памяти и занесение его в регистр процессора (в команде обычно указывается адрес ячейки памяти и номер регистра). Пересылка информации в противоположном направлении производится командой store(сохранение). Операнды во всех командах обработки информации в АЛУ могут находиться только в регистрах процессора (чаще всего в регистрах общего назначения). Результат операции также заносится в регистр. В архитектуре отсутствуют команды обработки, допускающие прямое обращение к основной памяти. Допускается наличие в наборе команд ограниченного числа команд, где операнд является частью кода команды. Состав и информационные тракты микропроцессора с выделенным доступом к памяти показаны на рис. 51. Две из трех шин, расположенных между массивом РОН и АЛУ, обеспечивают передачу в арифметико-логическое устройство операндов, хранящихся в двух регистрах общего назначения. Третья служит для занесения результата в выделенный для этого регистр. Эти же шины позволяют загрузить в регистры содержимое ячеек основной памяти и сохранить в основной памяти информацию, находящуюся в РОН.  Рисунок 51 – Архитектура микропроцессора с выделенным доступом к памяти Рисунок 51 – Архитектура микропроцессора с выделенным доступом к памятиК достоинствам архитектуры с выделенным доступом к памяти следует отнести простоту декодирования и исполнения команды. Архитектура с выделенным доступом к памяти характерна для всех микропроцессоров с RISC-архитектурой |