Шинная организация микропроцессорных систем- с одной шиной, с дв. Программа для эвм это упорядоченная последовательность команд, подлежащая обработке

Скачать 1.97 Mb. Скачать 1.97 Mb.

|

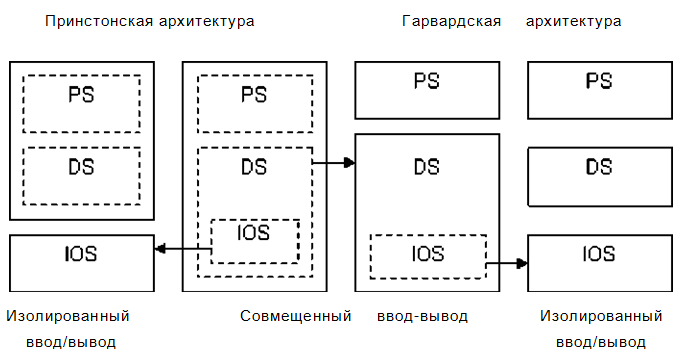

3. Понятие организации и архитектуры.Под организацией понимают состав компонентов (аппаратных или программных средств), связи между ними и их функциональные характеристики. ВМ имеет многоуровневую иерархическую организацию со своими составными компонентами на каждом уровне: нижний уровень – уровень физических компонентов – физическая организация (представляется в виде принципиальной схемы); уровень реализуемых в ВМ функций – логическая (функциональная) организация (представляется в виде функциональной схемы); верхний уровень – уровень аппаратуры (состав, функциональные связи и характеристики аппаратных модулей) – структурная организация (представляется в виде структурной схемы). Определение термина «архитектура компьютера» дал в 1970 г. С.С.Хассон (S.S.Husson): это «характеристики вычислительной системы с точки зрения программиста». Первоначально под термином архитектура вычислительной машины подразумевалось описание структуры данных и регистров, необходимое для уяснения системы команд ВМ и интерпретации этих команд. Иначе говоря, этим понятием охватывались те минимальные знания, которые могли понадобиться программисту для составления программы на машинном языке: программно-доступные регистры (программистская модель) ВМ; форма представления команд для ВМ (коды операций и форматы машинных команд) и правила их интерпретации этой машиной; способы адресации данных в этих командах; форма представления данных (типы и форматы данных). Архитектура, понимаемая в этом смысле, называется архитектурой набора команд. Архитектура набора команд служит границей между аппаратурой и программным обеспечением и представляет ту часть ВМ, которая видна программисту, разрабатывающему программы на машинно-ориентированном языке. Следует отметить, что это наиболее частое употребление этого термина. В широком смысле под архитектурой понимают структурную организацию ВМ в виде совокупности функциональных модулей и определенных связей между ними. Под микроархитектурой понимается структурная организация процессора (микропроцессора), т.е. внутренняя реализация архитектуры набора команд процессора. 4. Фон-неймановская (принстонская) и гарвардская архитектуры. Организация пространств памяти и ввода/вывода.Фон-неймановская (принстонская) и гарвардская архитектуры Эти архитектурные варианты были предложены в конце 1940-х годов специалистами соответственно Принстонского и Гарвардского университетов США для разрабатываемых ими моделей компьютеров. В большинстве современных ВМ для хранения программ и данных используется общая память. Для обращения к этой памяти используется общая системная шина, по которой в процессор поступают и команды, и данные. Такая организация получила название архитектуры фон Неймана или Принстонской архитектуры, а ВМ с такой архитектурой называют машинами фон-неймановского или принстонского типа. В них области для хранения программ (Program Space – PS) и данных (Data Space – DS) образуют единое пространство и могут размещаться в любом месте общей памяти. При этом нет никаких признаков, указывающих на тип информации в ячейке памяти. Содержимое ячейки интерпретируется ЦП, и задача программиста – следить за тем, чтобы данные и программа обрабатывались по-разному. Эта архитектура имеет ряд важных достоинств. Наличие общей памяти позволяет оперативно перераспределять ее объем для хранения отдельных массивов команд и данных в зависимости от решаемых задач. Таким образом, обеспечивается возможность более эффективного использования имеющегося объема основной памяти в каждом конкретном случае применения микропроцессора. Использование общей шины для передачи команд и данных значительно упрощает отладку, тестирование и текущий контроль функционирования системы, повышает ее надежность. Гарвардская архитектура характеризуется физическим разделением памяти команд (программ) и памяти данных. В ее классическом варианте программы и данные хранятся в двух раздельных памятях, каждая из которых соединяется с процессором отдельной шиной, что позволяет полностью совмещать во времени выборку и исполнение команд, т.е. одновременно с чтением-записью данных при выполнении текущей команды производить выборку и декодирование следующей команды. ЭВМ, спроектированные в соответствии с концепцией разделения памяти на два вида, называют машинами гарвардского типа. Такое разделение позволяет повысить быстродействие и упростить схемотехническую реализацию микропроцессорной системы. Недостатки Гарвардской архитектуры связаны с необходимостью использования большего числа шин, а также с фиксированным объемом памяти, выделенной для команд и данных, назначение которой не может оперативно перераспределяться в соответствии с требованиями решаемой задачи. Поэтому приходится использовать память большего объема, коэффициент использования которой при решении различных задач оказывается более низким, чем в системах с Принстонской архитектурой. Однако развитие микроэлектронной технологии позволяет в значительной степени преодолеть указанные недостатки. Дальнейшее совершенствование архитектур обоих типов состояло в выделении специального пространства данных небольшого объема, которое представляет собой набор программно-доступных регистров (Register Space). В отличие от памяти и портов ввода/вывода регистры располагаются всегда внутри процессора вместе с АЛУ, что обеспечивает быстрый физический доступ к информации, хранящейся в них. В некоторые интервалы времени программа наиболее интенсивно работает лишь с небольшим объемом данных. Для временного хранения этих данных и предназначена регистровая область – набор программно доступных регистров. Регистровая область может быть как полностью изолирована от пространства данных DS, так и частично пересекаться с ним, что дает возможность рассматривать отдельные регистры процессора как обычные ячейки памяти данных. Такая организация является целесообразной, если в процессоре поддерживается быстрый доступ ко всей или хотя бы к некоторой части памяти данных. Пространство ввода/вывода представляет набор адресуемых буферных схем и регистров, которые называются портами и через которые осуществляется связь с внешними и внутренними аппаратными средствами ВМ. В вычислительной машине может использоваться два варианта организации доступа к портам ввода/вывода: изолированный и совмещенный ввод/вывод. При изолированном вводе/выводе порты размещены в специальном пространстве ввода/вывода (Input/Output Space – IOS), изолированном от других пространств данных. В этом случае процессор имеет специальный набор команд ввода/вывода. При совмещенном вводе/выводе или вводе/выводе с отображением на память изолированное пространство ввода/вывода отсутствует, а в пространстве памяти данных DS выделяются области, в которых размещаются порты. Организация доступа к портам в такой ВМ ничем не отличается от процесса обращения к данным в памяти. На рис. 2 представлены четыре типовых набора областей для хранения программ и данных. Стрелками показан процесс изоляции отдельных областей, приводящий к появлению нового типового набора. Все наборы существуют реально, каждый имеет свои преимущества и недостатки, учет которых позволяет создавать высокоэффективные системы различного назначения.  Рисунок 2 – Типовые наборы областей для хранения программ и данных Организация пространств памяти и ввода/вывода Память представляет собой линейно упорядоченный набор n-разрядных ячеек с произвольным доступом (одномерный массив) – линейная память. Все ячейки пронумерованы, таким образом каждой ячейке набора соответствует число, называемое ее адресом. Все адреса занимают целочисленный диапазон от 0 до 2m-1 (m – разрядность адреса), который образует адресное пространство памяти. В большинстве случаев процессор может адресоваться к памяти с точностью до одного байта, т.е. наименьшей адресуемой единицей является байт и память имеет байтовую организацию. Программные объекты (команды и операнды) могут иметь длину, превышающую один байт, например, два байта – 16-разрядное слово или просто слово, четыре байта – 32-разрядное слово или двойное слово, восемь байтов – 64-разрядное слово или учетверенное слово. Такие объекты располагаются в смежных ячейках пространства памяти. Адресом объекта служит наименьший из адресов ячеек, занимаемых им. Обычно младший байт размещается в ячейке с меньшим адресом, в этом случае адресом объекта является адрес его младшего байта. Такой порядок называется Little-Endian Memory Format. Он используется в микропроцессорах с архитектурой x86 фирмы Intel. В других семействах процессоров применяют обратный порядок – Big-Endian Memory Format, в котором объекты располагаются в смежных ячейках памяти, начиная со старшего байта, а младшие байты размещаются в последующих ячейках. В этом случае адресом объекта является адрес его старшего байта. Такой порядок используется, например, в процессорах фирмы Motorola. Для взаимного преобразования форматов в процессорах имеются специальные команды. Операция обращения к памяти предполагает считывание или запись всего объекта как единого целого. Например, 16-разрядные слова в памяти хранятся в двух соседних ячейках. Старший байт слова занимает ячейку с большим адресом, а младший – ячейку с меньшим адресом. При этом адрес младшего байта служит адресом слова. Часто организация памяти предусматривает определенные ограничения на возможное расположение многобайтовых объектов. В этом случае объекты должны выравниваться по соответствующей границе: слова по четному адресу, двойного слова по адресу, кратному четырем, учетверенного слова по адресу, кратному восьми. Например, слова в памяти могут находиться только по четным адресам. Тогда при доступе к слову значение младшего разряда его адреса, указывающего на байт в слове, во внимание не принимается. Такая память имеет границу слов. Рассмотренная организация памяти соответствует нижнему (физическому) уровню представления памяти. Пространство ввода/вывода имеет такую же организацию. Существует более высокий (логический) уровень организации памяти, на котором работает программист и который связан с архитектурой процессора. |