Шинная организация микропроцессорных систем- с одной шиной, с дв. Программа для эвм это упорядоченная последовательность команд, подлежащая обработке

Скачать 1.97 Mb. Скачать 1.97 Mb.

|

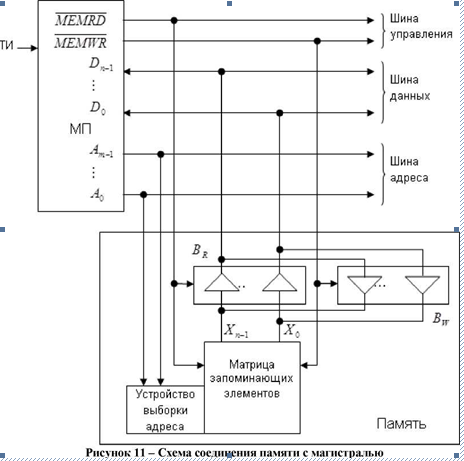

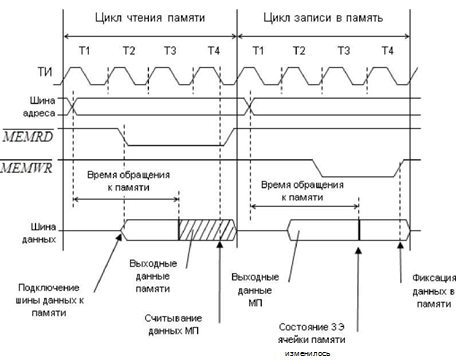

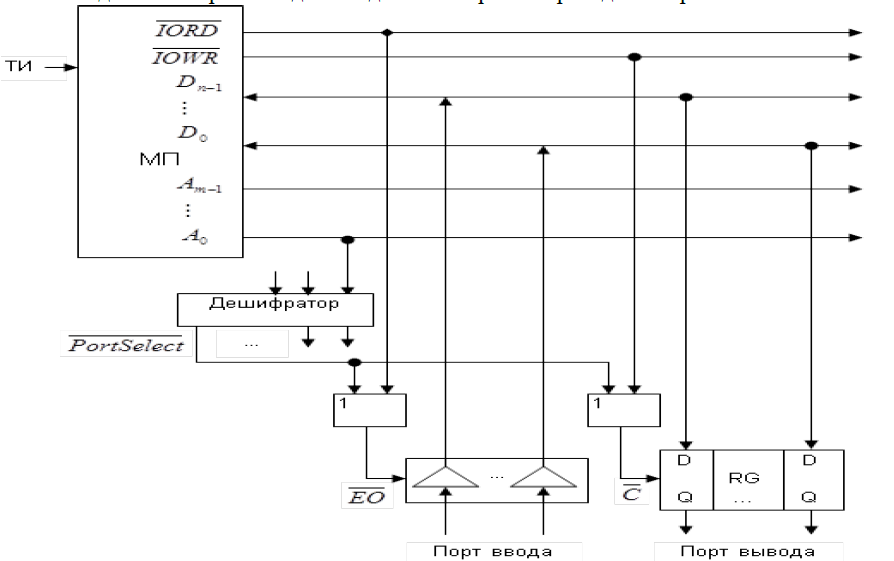

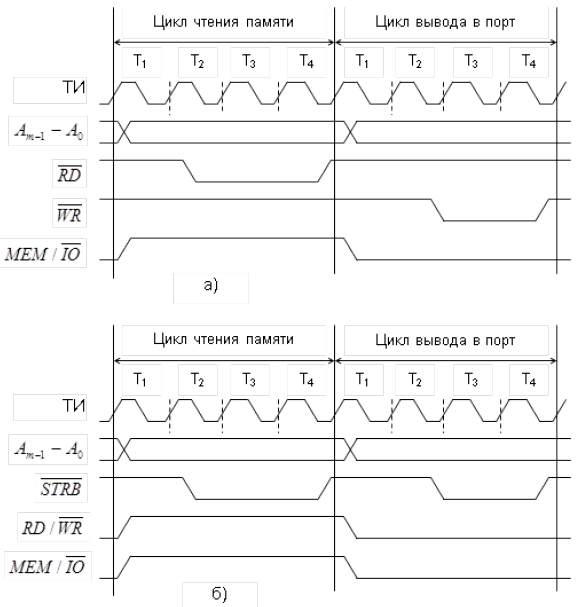

11. Организация обращения к магистрали с синхронным доступом.МП управляет работой шины синхронно с входной тактовой частотой. Элементарным интервалом времени при реализации протоколов обмена является такт магистрали, равный одному периоду синхросигнала. Каждый цикл шины содержит несколько тактов. Протокол обмена по магистрали предполагает выполнение определенной последовательности действий: 1. адресация памяти или порта ввода/вывода; 2. коммутация направления передачи (задание операции обмена – чтение или запись); 3. передача данных (выполнение операции обмена); 4. фиксация данных. В стандартном цикле магистрали для реализации каждого из приведенных выше действий отводится по одному такту, т.е. стандартный цикл магистрали содержит четыре обязательных такта T1-T4. Чтение/запись данных в память. Схема соединения памяти с магистралью приведена на рис. 11.  Рисунок 11 – Схема соединения памяти с магистралью В начале циклачтения памяти (рис. 12) МП по адресной шине передает адрес, по которому происходит выборка ячейки в памяти, и указанная ячейка памяти подключается к линиям Xn-1-X0. В первой половине такта T2 сигнал MEMRD переходит на низкий уровень, а во второй половине такта T4 он возвращается на высокий уровень. Низким уровнем этого сигнала открывается тристабильный вентиль чтения BR и линии Xn-1-X0 соединяются с линиями Dn-1-D0 шины данных. При этом вентиль записи BW закрыт. С момента передачи адреса по адресной шине в память до выдачи содержимого указанной ячейки памяти требуется определенное время, которое называют временемобращениякпамяти. Во время считывания микропроцессором данные на шине данных (выходе памяти) должны поддерживаться в неизменном состоянии. Выполнение этого требования обеспечивается за счет наличия в цикле магистрали такта T3 – к концу этого такта содержимое указанной ячейки памяти должно находиться на шине данных. По заднему фронту положительного импульса такта T4 содержимое шины данных заносится в МП (данные считываются МП и фиксируются во внутреннем регистре).  Рисунок 12 – Циклы чтения/записи в память В начале циклазаписивпамять (см. рис. 12) МП передает адрес. С первой половины такта T2 до окончания такта T4 МП осуществляет вывод записываемых данных на линии шины данных. Низким уровнем сигнала открывается тристабильный вентиль записи BW, линии соединяются с линиями Xn-1-X0, и начинается процесс записи в выбранную ячейку памяти. Для записи информации в память также требуется некоторое время, в течение которого происходит изменение состояния запоминающих элементов ячейки памяти. Поэтому в течение времени, пока сигнал MEMWR имеет низкий уровень, данные на входе памяти должны поддерживаться в неизменном состоянии. Для этого служит такт T3. Когда уровень сигнала MEMWR на такте T4 становится высоким, содержимое линий Xn-1-X0 фиксируется в ячейке памяти, указанной адресом. Ввод/выводданных.Схема соединения портов ввода/вывода с магистралью приведена на рис. 13. .  Рисунок 13 – Схема соединения портов ввода/вывода с магистралью Порт ввода представляет собой ряд тристабильных вентилей, при открывании которых по сигналу EO данные, поступающие в этот порт, передаются на линии шины данных, откуда уже считываются МП. Порт вывода представляет собой регистр, работа которого заключается в следующем. МП выводит данные на линии шины данных. Эти данные стробирующим сигналом C заносятся в регистр, который обеспечивает их сохранность до записи новых данных. Для выбора портов ввода/вывода используется дешифратор. Младшими k разрядами адресной шины можно осуществлять выбор 2k портов ввода или вывода. Временная диаграмма работы в циклах ввода/вывода данных аналогична временной диаграмме в циклах чтения/записи в память. Различие состоит в том, что вместо сигналов MEMRD и MEMWR МП выдает сигналы IORD и IOWR соответственно. Временные диаграммы работы шины в системе с тремя управляющими сигналами приведены на рис. 14 (на рисунке не показана шина данных).  Рисунок 14 – Циклы обращения к магистрали в системе с тремя управляющими сигналами Cигнал MEM/IO формируется в начале цикла одновременно с адресом и поддерживается неизменным в течение всего цикла магистрали. Аналогично формируется сигнал RD/WR, так как направление передачи остается неизменным в течение всего цикла шины. Управляющие сигналы RD и WR стробируют выполнение операций чтение и запись и вырабатываются аналогично сигналам MEMRD (IORD) и MEMWR (IOWR) соответственно. Стробирующий сигнал STRB определяет время выполнения операции чтение или запись и формируется так же, как и сигналы MEMRD, MEMWR, IORD или IOWR. В рассмотренных циклах обращения к магистрали временные соотношения чтения/записи полностью задаются МП. В этом случае память и порты ввода/вывода должны постоянно находиться в рабочем (готовом) состоянии. Такая организация обмена по магистрали называется обращением с синхронным доступом. |