Шинная организация микропроцессорных систем- с одной шиной, с дв. Программа для эвм это упорядоченная последовательность команд, подлежащая обработке

Скачать 1.97 Mb. Скачать 1.97 Mb.

|

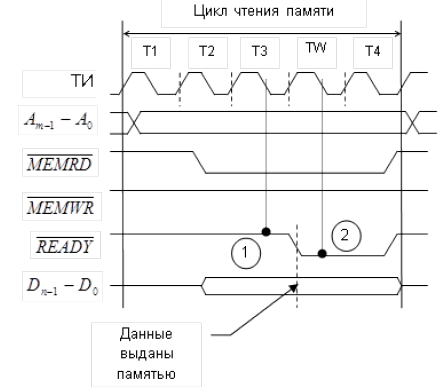

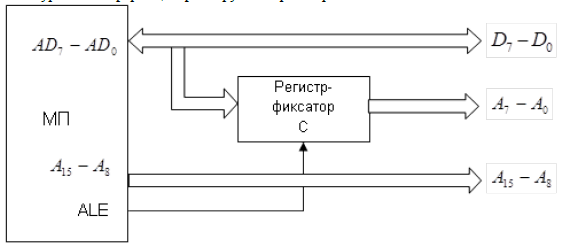

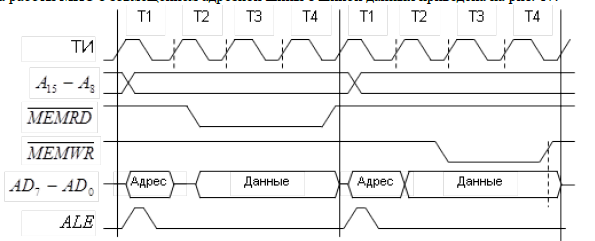

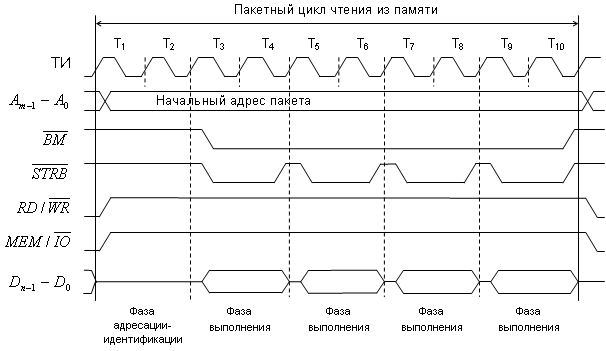

12. Организация обращения к магистрали с асинхронным доступом.Для медленных устройств система должна позволять произвольно увеличивать длительность циклов магистрали. Для этого из памяти или из портов ввода/вывода передаются управляющие сигналы, задающие время окончания цикла (подтверждающие окончание цикла). Как правило для этой цели используется сигнал READY (ГОТОВНОСТЬ), но могут также использоваться сигналы WAIT (ОЖИДАНИЕ) и TRANSFER_ACKNOWLEDGE (ПОДТВЕРЖДЕНИЕ ПЕРЕДАЧИ). Временная диаграмма работы магистрали с применением сигнала готовности приведена на рис. 15.  Рисунок 15 – Цикл обращения к магистрали с применением сигнала готовности МП по заднему фронту положительного импульса такта T3 (момент времени 1) анализирует состояние сигнала READY. Если данный сигнал имеет высокий уровень, цикл дополняется еще одним тактом (ожидания) TW. По заднему фронту положительного импульса такта TW (момент времени 2) опять анализируется состояние сигнала READY. Если уровень этого сигнала низкий, новые дополнительные такты не вводятся, а следующий такт T4 является последним тактом цикла. Если сигнал READY, анализируемый в такте TW, имеет высокий уровень, цикл дополняется новыми тактами. Таким образом, длительность цикла можно изменять в зависимости от готовности памяти или порта ввода/вывода. Такая организация обмена по магистрали называется обращением с асинхронным доступом. 13. Совмещение адресной шины и шины данных. Двухшинная магистраль с совмещенными шинами адреса/данных. В некоторых МП с целью сокращения ширины физической магистрали используют совмещение адресной шины с шиной данных. В течение первого такта цикла магистрали шина данных не используется, поэтому этот интервал можно использовать для передачи по шине данных адресных сигналов (адреса). Такая шина называется совмещенной шиной адреса/данных AD (Address/Data Bus). Этап передачи адресной информации по совмещенной шине адреса/данных отделяется по времени от этапа передачи данных и стробируется специальным сигналом ALE (Address Latch Enable), который включается в состав шины управления. Данную магистраль называют двухшинной с совмещенными шинами передачи адреса и данных. Если разрядность данных меньше разрядности адреса, то по совмещенной шине передаются только младшие разряды адреса, а старшие разряды при этом передаются по адресной шине. Входящий в состав шины управления сигнал ALE используется для разделения функций, выполняемых совмещенной шиной AD. По этому сигналу присутствующая на шине AD адресная информация должна быть принята (зафиксирована) во внешний (по отношению к МП) адресный регистр-фиксатор. Для этой цели обычно служит срез сигнала ALE (переход из высокого уровня в низкий). Обычно каждый модуль микропроцессорной системы с двухшинной магистралью (модуль памяти или интерфейс периферийного устройства) содержит локальный адресный регистр для запоминания адресной информации. Для фиксации адресной информации может быть использован и один общий регистр, в результате МП с двухшинной магистралью преобразуется в МП с тремя раздельными шинами (рис. 16). Когда уровень управляющего сигнала, приходящего на вход C регистра-фиксатора, становится высоким, входная информация без изменения передается на выход. При переходе управляющего сигнала на входе C в низкий уровень информация фиксируется в регистре.  Рисунок 16 – МПС с двухшинной магистралью Временная диаграмма работы МПС с совмещением адресной шины с шиной данных приведена на рис. 17.  Рисунок 17 – Цикл магистрали с совмещенными шинами передачи адреса и данных В течение первого такта T1 по совмещенной шине AD7-AD0 передаются адресные разряды A7-A0. Эти разряды по сигналу ALE фиксируются в регистре фиксаторе, который находится вне МП. 14. Механизм пакетной передачи данных по системной магистрали.Для обслуживания некоторых внутренних запросов при работе с памятью процессору может понадобиться последовательность циклов обмена, во время которых передаются данные, расположенные в смежной области адресного пространства. Такая ситуация может иметь место при выборке операндов, имеющих разрядность большую, чем разрядность шины данных (например, 32-разрядный процессор может обращаться к 64- или 128-разрядным операндам), или при заполнении строки кэш-памяти (например, если строка кэша имеет длину 32 байта, то для ее пересылки требуется четыре 64-разрядных цикла магистрали). Во всех таких случаях, когда требуется больше одного цикла для передачи данных, микропроцессор может выполнять пакетные циклы. Во время пакетного цикла между МП и памятью передается более одного слова, причем эти слова занимают смежные адреса и направление передачи для всех слов одинаково (т.е. все слова читаются из памяти или записываются в память). Такой блок данных называется пакетом, а протокол обмена по магистрали – режимом пакетной передачи (пакетный режим – Burst Mode). Выполнение стандартного цикла магистрали можно разбить на две фазы: • фаза адресации, которая включает адресацию памяти и коммутацию направления передачи; • фаза данных, которая включает передачу данных и их фиксацию. В пакетном режиме одна фаза адресации сопровождается множественными фазами данных (чтения или записи, но не чередующимися). Это означает, что пакет данных передается без указания текущего адреса внутри пакета. При этом передается адрес только первого слова, все последующие адреса генерируются из первого в самой памяти по определенному, заранее известному правилу. Такой протокол обмена возможен, если адрес и сигналы идентификации типа цикла выдавать только в первой фазе пакета, а в каждой из последующих фаз передавать только данные, адреса для которых уже не передаются по адресной шине. В результате на передачу первого слова затрачивается две фазы, а далее данные передаются в каждой фазе, а не через фазу, как в обычных циклах обмена. На рис. 21 приведена временная диаграмма пакетного цикла чтения из памяти, включающего передачу четырех слов.  Рисунок 21 – Пакетный цикл чтения из памяти Рисунок 21 – Пакетный цикл чтения из памяти В пакетном цикле фаза 1 занимает такты T1 и T2, а фаза 2 – такты T3 и T4. Пакетный цикл начинается МП так же, как и обычный: в первой фазе на шине адреса устанавливается адрес первого слова пакета, а на шине управления – сигналы идентификации типа цикла (например, MEM/IO и RD/WR). В следующей фазе передается первое слово данных, и, если оно не единственное, специальный управляющий сигнал BM, который указывает, что данный цикл пакетный. Далее МП продолжает цикл как пакетный, не вводя фазы адресации, а сразу перейдет к передаче следующего слова данных. О завершении пакетного цикла микропроцессор сообщает памяти снятием сигнала BM. Скорость передачи собственно данных в пакетном режиме увеличивается естественным образом за счет уменьшения числа передаваемых адресов. Из рис. 21 видно, что для передачи четырех слов с помощью пакетного цикла требуется 10 тактов, в то время как передача четырех слов с помощью обычных циклов занимает 4 цикла х 4 такта = 16 тактов. |