Шинная организация микропроцессорных систем- с одной шиной, с дв. Программа для эвм это упорядоченная последовательность команд, подлежащая обработке

Скачать 1.97 Mb. Скачать 1.97 Mb.

|

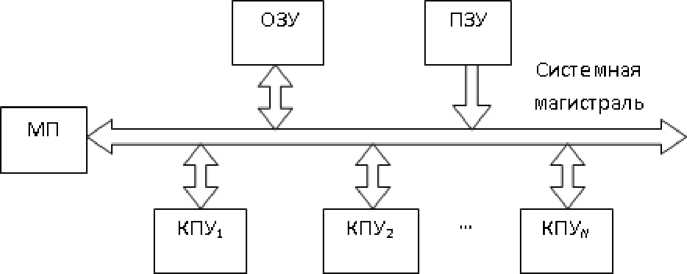

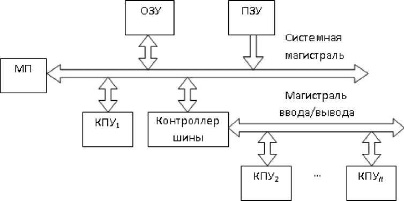

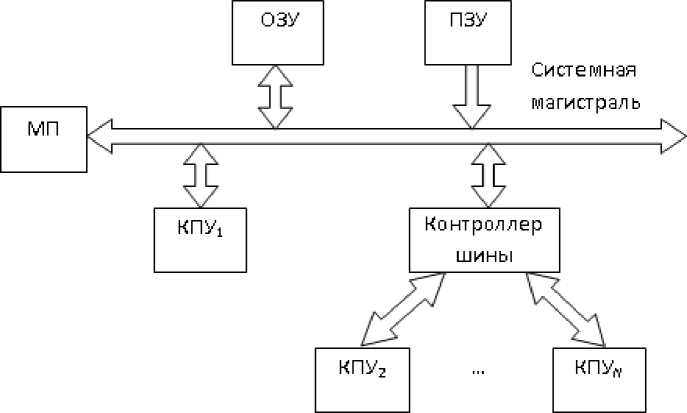

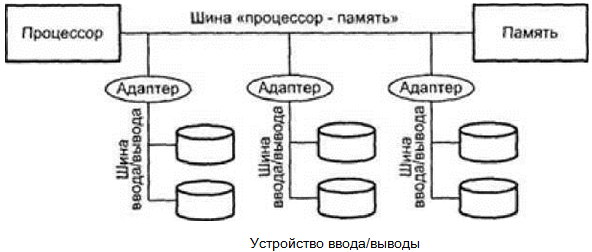

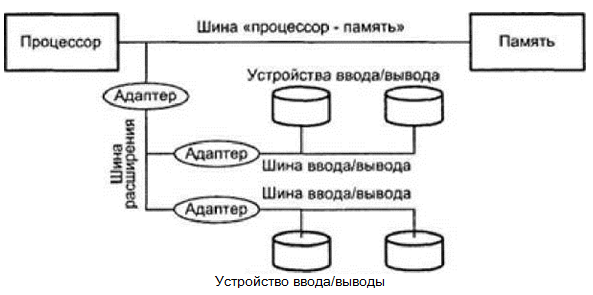

6. Типовые структуры МПС: магистральная, магистрально-каскадная, магистрально-радиальная.Магистральная, магистрально-каскадная и магистрально-радиальная структуры В зависимости от способа подключения отдельных модулей микропроцессорной системы к системной магистрали различают три типовые структуры микропроцессорных систем: магистральная; магистрально-каскадная; магистрально-радиальная. В магистральной структуре (рис. 5) все модули подсистем памяти и ввода/вывода подключаются непосредственно к системной магистрали.  Рисунок 5 – Магистральная структура Это наиболее простая структура. Недостатками магистральной структуры являются: • все модули должны поддерживать протокол обмена по системной магистрали и содержать средства сопряжения с ней, которые в зависимости от микропроцессора могут быть достаточно сложными; • небольшое быстродействие, так как медленные периферийные устройства могут надолго занимать системную магистраль. В магистрально-каскадной и магистрально-радиальной структурах отдельные модули подключаются с помощью специальных контроллеров (адаптеров) шин, основное назначение которых – реализовать приоритетные соотношения при использовании магистрали. В магистрально-каскадной структуре (рис. 6) отдельные модули подключаются к контроллеру шины с помощью дополнительного общего канала, например, магистрали или шины ввода/вывода, т.е. по магистральной схеме.  Рисунок 6 – Магистральная-каскадная структура В магистрально-радиальной структуре (рис. 7) каждый модуль подключается к контроллеру шины с помощью индивидуального канала, т. е. по радиальной схеме.  Рисунок 7 – Магистральная-радиальная структура Рисунок 7 – Магистральная-радиальная структура 7.Шинная организация микропроцессорных систем: с одной шиной, с двумя видами шин, с тремя видами шин.В микропроцессорной системе системная магистраль служит единственным трактом для потоков команд, данных и управления. Наличие общей шины существенно упрощает реализацию МПС, позволяет легко менять ее состав и конфигурацию. Вместе с тем, именно с шиной связан и основной недостаток такой архитектуры: в каждый момент передавать информацию по шине может только одно устройство. Основную нагрузку на шину создают обмены между процессором и памятью, связанные с извлечением из памяти команд и данных и записью в память результатов вычислений. На операции ввода/вывода остается лишь часть пропускной способности шины. Практика показывает, что даже при достаточно быстрой шине для 90% приложений этих остаточных ресурсов обычно не хватает, особенно в случае ввода или вывода больших массивов данных. Поэтому при сохранении фон-неймановской концепции последовательного выполнения команд программы шинная архитектура в чистом ее виде оказывается недостаточно эффективной. Более распространена архитектура с иерархией шин, где помимо системной шины имеется еще несколько дополнительных шин. Они могут обеспечивать непосредственную связь между устройствами с наиболее интенсивным обменом, например процессором и кэш-памятью. Другой вариант использования дополнительных шин – объединение однотипных устройств ввода/вывода с последующим выходом с дополнительной шины на системную. Это позволяет снизить нагрузку на общую шину и более эффективно расходовать ее пропускную способность. Наибольшее распространение получили микропроцессорные системы с одной шиной, с двумя или тремя видами шин. В структурах с одной шиной имеется одна системная шина, обеспечивающая обмен информацией между процессором и памятью, а также между устройствами ввода/вывода, с одной стороны, и процессором либо памятью – с другой (рис. 8). Рисунок 8 – МПС с одной шиной Для такого подхода характерны простота и низкая стоимость. Однако одношинная организация не в состоянии обеспечить высокую скорость обмена, причем узким местом является именно шина. В МПС с двумя видами шин устройства ввода/вывода подключаются к шинам ввода/вывода, которые берут на себя основной обмен, не связанный с выходом на процессор или память (рис. 9). Подключение осуществляется с помощью адаптеров шин, которые обеспечивают буферизацию данных при их пересылке между системной шиной и контроллерами устройств ввода/вывода. Это позволяет микропроцессорной системе поддерживать работу множества устройств ввода/вывода и одновременно развязать обмен информацией по тракту процессор-память и обмен информацией с устройствами ввода/вывода. Подобная схема существенно снижает нагрузку на скоростную шину процессор-память и способствует повышению общей производительности микропроцессорной системы.  Рисунок 9 – МПС с двумя видами шин Шина процессор-память обеспечивает непосредственную связь между процессором и основной памятью. В современных микропроцессорах такую шину часто называют шиной переднего плана (передней или первичной) и обозначают аббревиатурой FSB (Front-Side Bus). Интенсивный обмен между процессором и памятью требует, чтобы полоса пропускания шины, т.е. количество информации, проходящей по шине в единицу времени, была наибольшей. В варианте с одной шиной роль этой шины выполняет системная шина, однако в плане эффективности значительно выгоднее, если обмен между процессором и основной памятью ведется по отдельной шине. К рассматриваемому виду можно отнести также шину, связывающую процессор с кэш-памятью второго уровня, известную как шина заднего плана (тыльная или вторичная) – BSB (Back-Side Bus). BSB позволяет вести обмен с большей скоростью, чем FSB, и полностью реализовать возможности более скоростной кэш-памяти. Архитектура с использованием шин FSB и BSB известна как архитектура двойной независимой шины DIB (Dual Independent Bus). Наличие двух шин позволяет одновременно обращаться к основной памяти и кэш-памятью второго уровня, тем самым увеличивая общую производительность системы. Для подключения быстродействующих периферийных устройств в систему шин может быть добавлена высокоскоростная шина расширения (рис. 10).  Рисунок 10 – МПС с тремя видами шин Шины ввода/вывода подключаются к шине расширения, а уже с нее через адаптер к шине процессор-память. Схема еще более снижает нагрузку на шину процессор-память. Такую организацию шин называют архитектурой с «пристройкой» (mezzanine architecture). |