Шинная организация микропроцессорных систем- с одной шиной, с дв. Программа для эвм это упорядоченная последовательность команд, подлежащая обработке

Скачать 1.97 Mb. Скачать 1.97 Mb.

|

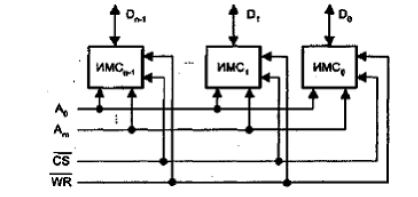

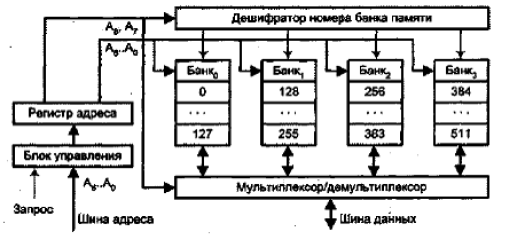

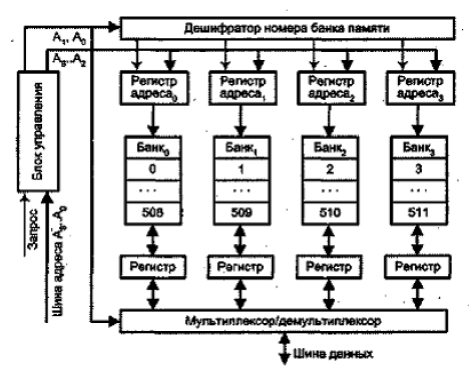

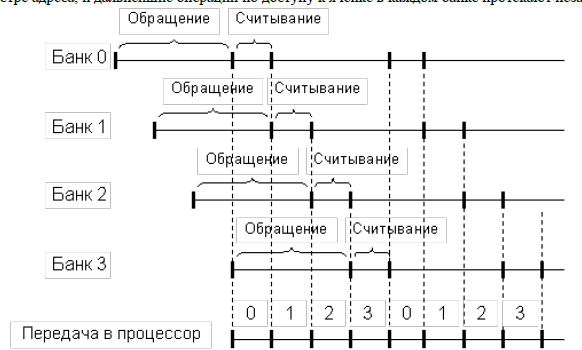

18. Стековая память.Стековая память является безадресной памятью с последовательным доступом. В стековом ЗУ ячейки образуют одномерный массив, в котором соседние ячейки связаны друг с другом разрядными цепями передачи слов. Слова становятся доступными для чтения и записи только в определенном порядке. Каждое хранящееся слово привязано не к конкретной ячейке, а к своему положению относительно других хранящихся слов. Слова могут перемещаться по ячейкам, но при этом сохраняют свою взаимную упорядоченность. Поэтому достаточно обеспечить средства для чтения только определенной ячейки. Конкретное слово считывается в тот момент, когда в процессе перемещения по памяти оно оказывается в ячейке, из которой может производиться чтение. Аналогично достаточно обеспечить средства для записи только в определенную ячейку ЗУ. В зависимости от того, как перемещаются слова в ЗМ, стековые ЗУ подразделяются на два основных типа: память типа очереди или память типа FIFO (First In First Out – первым вошел, первым вышел); память магазинного типа или стек. Память типа очереди или память типа FIFO. В ЗУ этого типа слова перемещаются всегда в одном направлении от входа к выходу. Данные становятся доступными для считывания в том порядке, в котором производилась запись. Возможно два варианта организации памяти типа FIFO. В первом случае информация записывается в ячейку в начале цепочки и считывается в ее конце. Запись и чтение информации производятся синхронно. ЗУ этого типа используются в качестве задержки на N тактов, где N – количество ячеек в памяти. Во втором случае информация записывается в первую свободную ячейку. Запись и чтение информации производятся асинхронно. ЗУ этого типа используются в качестве буферов с целью согласования различных скоростей информационных потоков двух компонентов микропроцессорной системы. Стек. В ЗУ этого типа слова считываются в порядке, обратном порядку записи, т.е. по правилу LIFO (Last In First Out – последним вошел, первым вышел). Стек можно представить в виде вертикально расположенного массива ячеек. Доступ осуществляется всегда к верхней ячейке, которая называется вершиной стека. При записи в вершину стека все слова сдвигаются вниз на одну ячейку, а содержимое нижней ячейки теряется, т.е. стек опускается и происходит операция вталкивания в стек (PUSH). При чтении из вершины стека происходит обратное действие, т.е. стек поднимается и происходит операция выталкивания из стека (POP). При этом становится доступным слово из второй ячейки. В универсальных МП стековая память организуется с использованием адресной памяти – памяти с произвольным доступом (моделируется на памяти с произвольным доступом). При этом в качестве стека используется часть основной памяти. Такой стек называется аппаратно-программным стеком. Это дает дополнительную гибкость, поскольку емкость стека может меняться при необходимости, и максимальный размер стека оказывается ограниченным только объемом основной памяти. Кроме того, перенос стека в память дает экономию аппаратуры. Для организации стека в памяти с произвольным доступом используется реверсивный счетчик, который называется указателем стека. В стандартном стеке в указателе стека всегда находится адрес ячейки памяти, которая соответствует вершине стека. При записи в стек слова сначала указатель стека уменьшается на 1, а затем слово помещается по адресу, полученному в указателе стека. При чтении слова из стека сначала слово извлекается из вершины стека (по адресу, находящемуся в указателе стека), а затем указатель стека увеличивается на 1. В случае использования памяти с побайтовой адресацией при занесении слова в стек и извлечении слова из стека содержимое указателя стека изменяется на величину, равную количеству байт в слове. Возможны и другие варианты организации стека в памяти с произвольным доступом, отличающиеся тем, что указатель стека указывает на первую свободную ячейку в стеке (на ячейку, расположенную над вершиной стека), а также тем, что стек продвигается в памяти в направлении увеличения адресов. В универсальных МП стек и стековая адресация используются для временного хранения данных, при организации переходов к подпрограммам и возврате из них, а также при обработке прерываний. 19. Основная память: блочная, циклическая и блочно-циклическая схемы организации основной памяти.В процессе выполнения программы МП обращается непосредственно только к основной памяти, т.е. основная память представляет собой единственный вид памяти, к которой процессор может обращаться непосредственно (исключение составляют лишь регистры процессора). Основная память – это реально существующая (физическая) память, в которой с точки зрения процессора находятся выполняемые программы и в которой должны размещаться данные, чтобы программа во время работы могла к ним обращаться. Информация, хранящаяся на внешних ЗУ, становится доступной процессору только после того, как будет переписана в основную память. Адреса, существующие в основной памяти, называются физическими адресами, а диапазон физических адресов, к которым может обращаться конкретный процессор, называется пространством физических адресов этого процессора. Обычно адресация основной памяти производится с точностью до байта. С целью ускорения этого процесса при обращении к основной памяти запись и считывание нескольких байтов могут осуществляться за один раз. Основную память образуют запоминающие устройства с произвольным доступом. Основная память может включать в себя два типа устройств: оперативные запоминающие устройства (ОЗУ) и постоянные запоминающие устройства (ПЗУ). Особенностью современной ОП является ее блочная организация. Необходимость объединения нескольких микросхем памяти возникает по двум причинам: разрядность ячеек в микросхемах памяти, как правило, меньше разрядности шины данных МПС; емкость основной памяти современных МПС слишком велика, чтобы ее можно было реализовать на базе единственной интегральной микросхемы памяти. Получение требуемой разрядности ЗУ реализуется за счет объединения адресных входов объединяемых микросхем памяти. Информационные входы и выходы микросхем являются входами и выходами модуля ЗУ увеличенной разрядности (рис. 24).  Рисунок 24 – Получение требуемой разрядности ЗУ Полученную совокупность микросхем называют модулем памяти. Модулем можно считать и единственную микросхему, если она уже имеет нужную разрядность. Один или несколько модулей образуют банк памяти. Для получения требуемой емкости ЗУ нужно определенным образом объединить несколько банков памяти меньшей емкости. В общем случае основная память МПС практически всегда имеет блочную структуру, т. е. содержит несколько банков. При использовании блочной памяти, состоящей из B банков, адрес ячейки A преобразуется в пару (b, w), где b – номер банка, w – адрес ячейки внутри банка. Известны три схемы распределения адресов A по банкам памяти (распределения разрядов адреса A между b и w): блочная – номер банка b определяют старшие разряды адреса A; циклическая – b = A mod B (остаток от деления), w = A div B (частное от деления); блочно-циклическая – комбинация первых двух схем. Рассмотрение основных структур блочной ОП будем проводить на примере памяти емкостью 512 слов, построенной из четырех банков по 128 слов в каждом. Блочная структура (схема). Адресное пространство памяти разбивается на группы последовательных адресов, и каждая такая группа обеспечивается отдельным банком памяти (рис. 25). Для обращения к ОП используется 9-разрядный адрес, семь младших разрядов которого (А6-А0) поступают параллельно на все банки памяти и выбирают в каждом из них одну ячейку. Два старших разряда адреса (A8, А7) содержат номер банка. Выбор банка обеспечивается либо с помощью дешифратора номера банка памяти, либо путем мультиплексирования информации (на рис. 25 показаны оба варианта). В функциональном отношении такая ОП может рассматриваться как единое ЗУ, емкость которого равна суммарной емкости составляющих банков, а быстродействие – быстродействию отдельного банка.  Рисунок 25 – Структура основной памяти на основе блочной схемы Циклическая схема. Кроме возможности наращивания емкости, блочное построение памяти обладает еще одним достоинством – позволяет сократить время доступа к данным. Это возможно благодаря потенциальному параллелизму, присущему блочной организации. Большей скорости доступа можно достичь за счет одновременного доступа к нескольким банкам памяти. Одна из используемых для этого методик называется расслоением памяти. В ее основе лежит так называемое чередование адресов (address interleaving). Прием чередования адресов базируется на рассмотренном ранее свойстве локальности по обращению, согласно которому последовательный доступ в память обычно производится к ячейкам, имеющим смежные адреса. Суть процедуры чередования адресов состоит в том, что соседние адреса относятся к разным банкам. Чередование адресов обеспечивается за счет использования для распределения адресов между банками памяти циклической схемы. В нашем примере (рис. 26) для выбора банка используются два младших разряда адреса (A1, A0), а для выбора ячейки в банке – 7 старших разрядов (A8-A2).  Рисунок 26 – Структура основной памяти на основе циклической схемы Поскольку в каждом такте на шине адреса может присутствовать адрес только одной ячейки, параллельное обращение к нескольким банкам невозможно, однако оно может быть организовано со сдвигом на один такт. Адрес ячейки запоминается в индивидуальном регистре адреса, и дальнейшие операции по доступу к ячейке в каждом банке протекают независимо (рис. 27).  Рисунок 27 – Организация обращения к основной памяти на основе циклической схемы При большом количестве банков среднее время доступа к ОП сокращается почти в В раз (В – количество банков), но при условии, что ячейки, к которым производится последовательное обращение, относятся к разным банкам. Если же запросы к одному и тому же банку следуют друг за другом, каждый следующий запрос должен ожидать завершения обслуживания предыдущего. Такая ситуация называется конфликтом по доступу. При частом возникновении конфликтов по доступу метод становится неэффективным. Обычно B равно 2-16, но в некоторых случаях число банков памяти может достигать 64-128. Механизм расслоения памяти может использоваться и для повышения надежности памяти. При неисправностях или повреждениях соответствующие банки памяти исключаются из основной памяти с последующим ее перегруппированием, в результате чего работоспособность памяти сохраняется, хотя и с некоторым ухудшением ее параметров. |