Шинная организация микропроцессорных систем- с одной шиной, с дв. Программа для эвм это упорядоченная последовательность команд, подлежащая обработке

Скачать 1.97 Mb. Скачать 1.97 Mb.

|

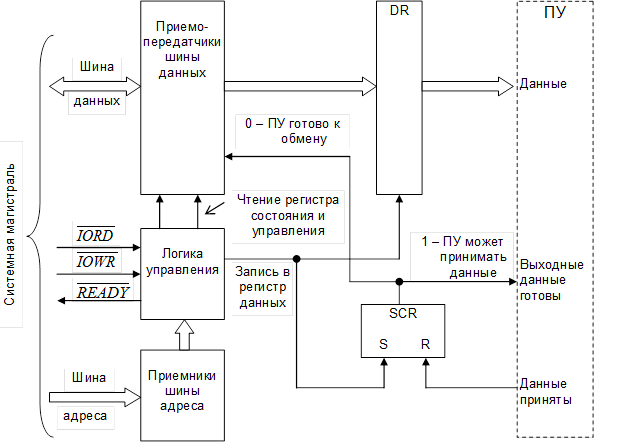

50.Организация параллельной передачи данных.Параллельные интерфейсы характеризуются тем, что в них для передачи бит в слове используются отдельные сигнальные линии, и биты передаются одновременно. Параллельная передача данных между МПС и ПУ является по своей организации наиболее простым способом обмена. Для организации параллельной передачи данных помимо шины данных, количество линий в которой равно числу одновременно передаваемых битов данных, используется минимальное количество управляющих сигналов. В простейшем случае в контроллере параллельного интерфейса, обеспечивающем передачу данных в периферийное устройство (рис. 77), в шине связи с ПУ используются всего два управляющих сигнала – Выходныеданныеготовыи Данныеприняты.  Рисунок 77 – Контроллер параллельного интерфейса, обеспечивающий передачу данных в ПУ Рисунок 77 – Контроллер параллельного интерфейса, обеспечивающий передачу данных в ПУДля формирования управляющего сигнала Выходныеданныеготовыи приема из ПУ управляющего сигнала Данныепринятыв контроллере используется одноразрядный адресуемый регистр состояния и управления SCR. Одновременно с записью очередного слова данных из шины данных системной магистрали в адресуемый регистр данных DR контроллера (по команде вывода) в регистр состояния и управления записывается логическая единица. Тем самым формируется управляющий сигнал Выходныеданныеготовыв шине связи с ПУ. ПУ, приняв слово данных, управляющим сигналом Данныепринятыобнуляет регистр состояния и управления контроллера. При этом формируется признак готовности ПУ к обмену, который может быть принят МП по одной из линий шины данных системной магистрали посредством стандартной операции ввода (чтение регистра состояния и управления). Логика управления контроллера обеспечивает селекцию адресов регистров контроллера, прием управляющих сигналов системной магистрали и формирование на их основе внутренних управляющих сигналов контроллера. Для сопряжения регистров контроллера с шинами адреса и данных системной магистрали в контроллере используются приемники шины адреса и приемопередатчики шины данных. Алгоритм обмена со стороны МП с использованием такого контроллера включает два шага: МП проверяет готовность ПУ к приему данных, путем чтения регистра состояния и управления контроллера; если ПУ готово к приему данных (логический 0 в регистре SCR), то МП выводит данные в регистр данных контроллера. Иначе повторяется шаг 1. Организация простого контроллера параллельного интерфейса, обеспечивающего прием данных из ПУ, показана на рис. 78. В этом контроллере при взаимодействии с периферийным устройством также используются два управляющих сигнала – ДанныеотПУготовыи Данныеприняты.  Рисунок 78 – Контроллер параллельного интерфейса, обеспечивающий прием данных из ПУ Для формирования управляющего сигнала Данныепринятыи приема из ПУ управляющего сигнала Данныеот ПУготовытакже используется одноразрядный адресуемый регистр состояния и управления SCR. ПУ сигналом ДанныеотПУготовызаписывает в регистр данных DR контроллера очередное слово данных. Этим же сигналом устанавливается в единицу регистр состояния и управления SCR. При этом формируется признак готовности ПУ к обмену, который может быть принят МП по одной из линий шины данных системной магистрали посредством стандартной операции ввода (чтение регистра состояния и управления). Тем самым контроллер извещает процессор о готовности данных в регистре DR. Процессор читает слово данных из регистра данных контроллера и обнуляет регистр состояния и управления SCR. При этом формируется управляющий сигнал Данныепринятыв шине связи с ПУ. Логика управления контроллера и приемопередатчики шин системной магистрали выполняют те же функции, что и в контроллере вывода. Алгоритм обмена со стороны МП с использованием такого контроллера включает два шага: МП проверяет наличие данных в регистре данных контроллера DR, путем чтения регистра состояния и управления контроллера; если данные готовы (логическая 1 в регистре SCR), то МП считывает данные из регистра данных контроллера. Иначе повторяется шаг 1. Как видно из рассмотренных примеров, для приема или передачи одного слова данных микропроцессору необходимо выполнить всего несколько команд, время осуществления которых и определяет максимально достижимую скорость обмена данными при параллельной передаче. При этом время обработки слова данных в электронных схемах контроллера можно не учитывать, так как оно существенно меньше времени выполнения одной команды процессора. Таким образом, при параллельной передаче обеспечивается скорость обмена, ограниченная только быстродействием ПУ. Простота реализации и относительно высокая скорость обмена, присущие параллельной передаче данных, обеспечили широкое распространение этого способа обмена с ПУ в микропроцессорных системах. |